# R&D for a 2nd generation AHCAL prototype

Mathias Reinecke

on behalf of the AHCAL partners

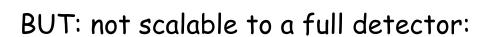

## Current AHCAL Testbeam Prototype

**FEB**

-8000 Tiles with SiPMs in 38 layers

-New Readout Electronics

-LED Calibration System

- -Electronics (ASICs), Tiles and Calibration System not integrated into layer

- -Electronics not optimized for SiPMs

- -Assembly to complicated (time, cost)

- -ADC not in Front End ASIC

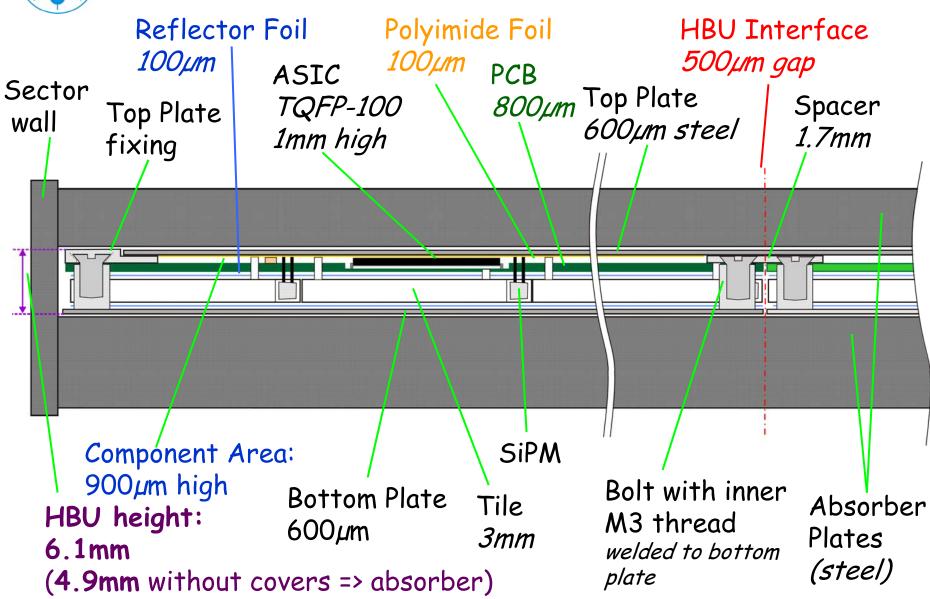

#### Mechanical Constraints

**FEB**

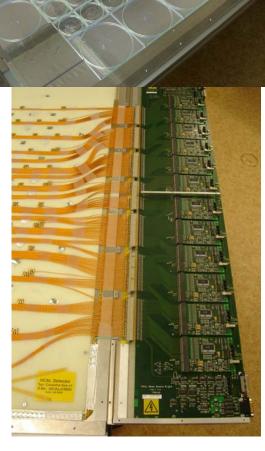

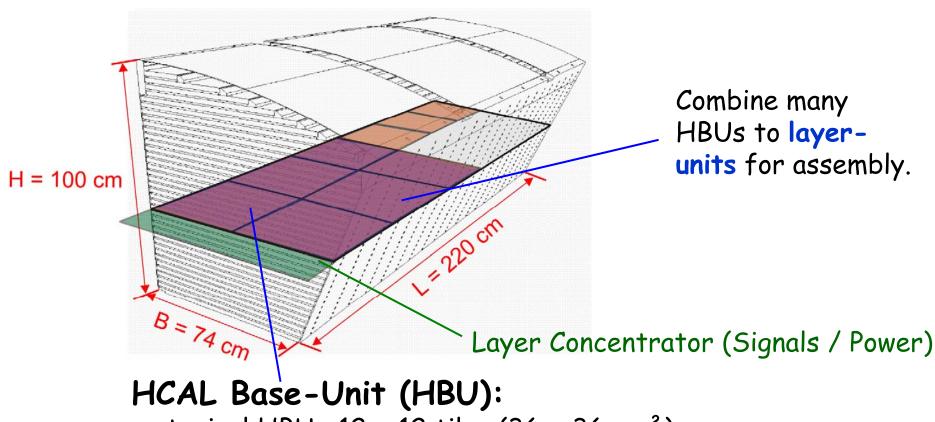

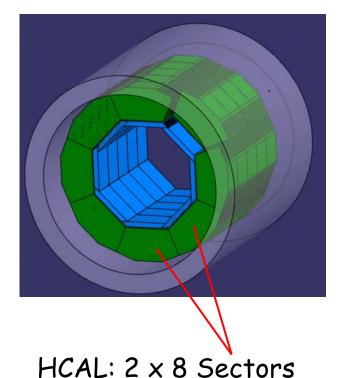

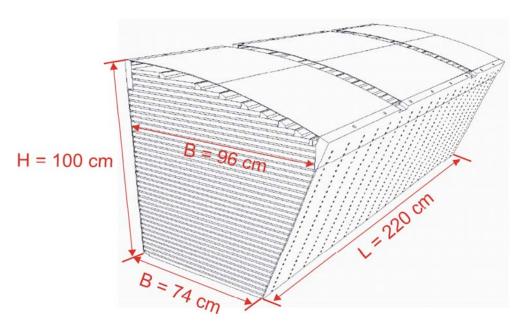

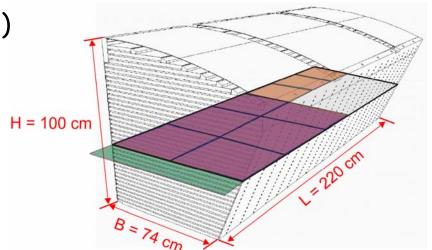

#### AHCAL Half-Sector with 38 layers

- typical HBU:  $12 \times 12$  tiles  $(36 \times 36 \text{ cm}^2)$

- Tiles and Electronics together on a PCB

#### Mechanical Constraints

2,432,000 Tiles

Requirements for a HCAL Base-Unit (HBU) from the Barrel's mechanics:

- -As large as possible (assembly time)

- -As thin as possible (barrel diameter)

- -Easy de-/installation of single units (repair)

- -Rail System needed (Sector walls?)

- -Minimize dead area

#### Tiles in the HBU

## Standard Tile: 30 x 30 x 3 mm<sup>3</sup>

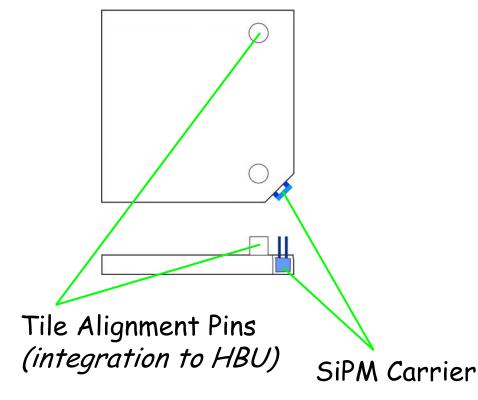

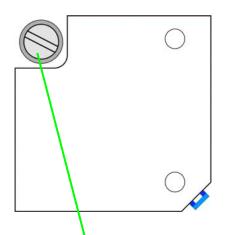

#### Mechanics Tile: HBU interconnection

HBU interconnection and HBU module setup

Minimum: 8 of 144 tiles in a HBU

6mm bolt with M3 thread inside

See last talk from Mikhail Danilov (ITEP)

#### HBU - How could it look like?

**FEB**

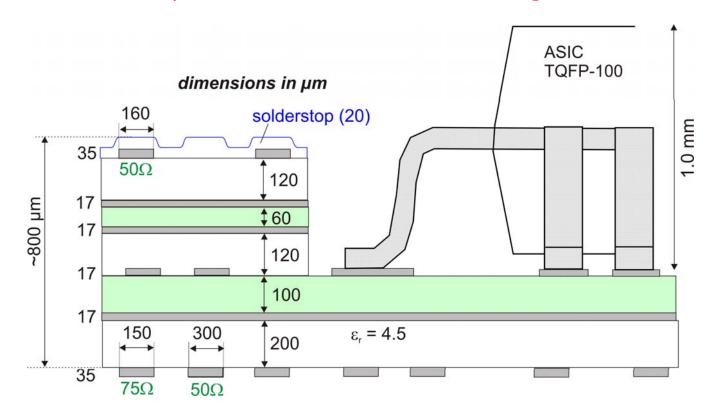

## HBU PCB - Layer Structure

- -6 layer design with cut-outs for ASICS and connectors

- $-75\Omega$  Lines for high-gain SiPM setup

- -Two signal layers for impedance-controlled routing

- -Total height (PCB + components): 1.5mm

- -Feasibility / Cost-factor under investigation

#### SPIROC - SiPM Readout ASIC

New ASIC, optimized for SiPM readout (L. Raux et al., LAL):

#### **Analog Part:**

- -36 SiPM input channels with 16-stage analogue memory

- -Variable gain (2x), dynamic range 1-2000 photo-electrons

- -Variable shaping time, 50-100ns

#### Digital Part:

- -Auto Trigger (threshold 1/2 photo-electrons, adjustable)

- -Time measurement (since last bunch crossing): 12-bit TDC

- -12-bit ADC and SRAM on-chip

- $-25\mu W$  per channel (power pulsing)

Submission in June 2007

See next talk from Christophe DE LA TAILLE (LAL)

## Temperature / Power Dissipation

From P. Göttlicher (DESY)

No. channels: 1100 / m<sup>2</sup>

Pow. Diss.:  $40\mu W$  / channel (25 $\mu W$  ASIC, 15 $\mu W$  HV, 3A / layer during bunch train)

Time constant of heat effects:  $\alpha = 6$  days

Temperature at far end ( $\Delta T$ ):  $\Delta T \approx 0.3 \, ^{\circ}C$

Power pulsing and a good thermal connection (cooling) enables a stable operation!

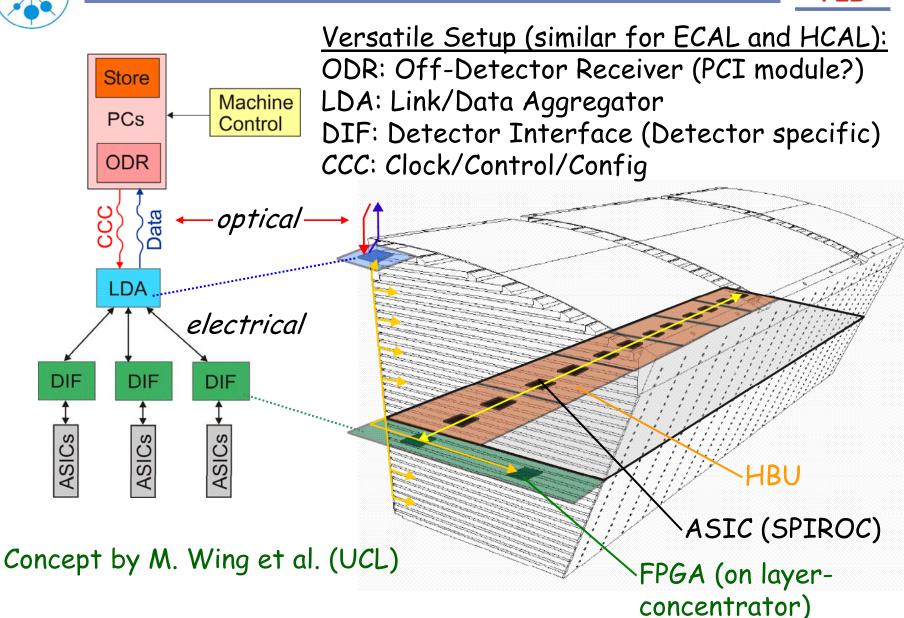

### DAQ - Interface

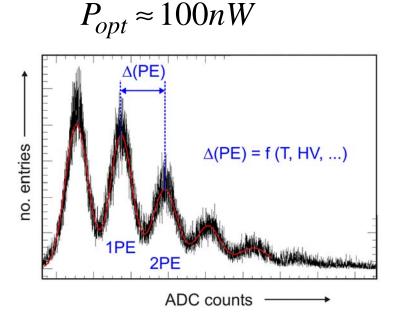

## Light Calibration System (LCS)

For single photon peaks (incl. losses):

SiPM response strongly depends on temperature and bias voltage.

LCS (based on UV LEDs) needed for:

- -Calibration (ADC counts per PE)

- -Gain Monitoring

#### <u>Different options under consideration</u>:

- -One LED per tile, integration into HBU => no fibers

- -One LED per HBU => no fibers between modules

- -LED outside HCAL gap (on DIF) => no electr. crosstalk to SiPM

Concept evaluation together with our colleagues from Prague!

**PCB**

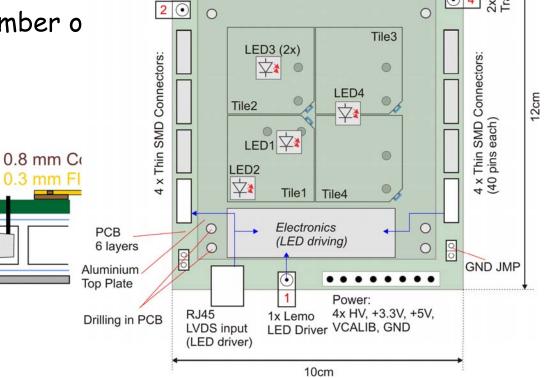

#### Testboard I: LED

**GND JMP**

⊙ 3

0

#### Test LED integration into HBU (LCS):

-Crosstalk of driving circuit to SiPN

-Integration to PCB / coupling to tile

-Connector test: stability, number o connection-cycles?

Reflector foil

LED

Testboard Interface

Pin 1

4x Lemo SiPM Outputs

₩ LED5 □□

1x Lemo LED AC/DC (Backside)

bottom plate

Module

Tile

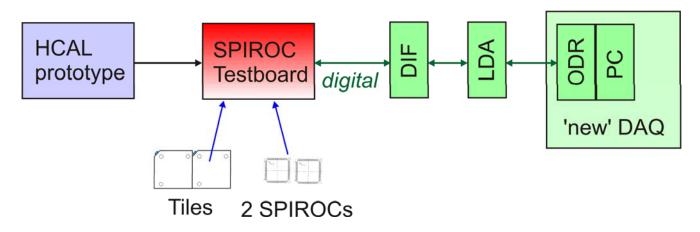

## Testboard II: ASIC + Integration

**FEB**

#### SPIROC Testboard (HBU prototype):

- -Assembly (Tiles, PCB, ASICs, LEDs), Cassette Construction

- -Performance in the dense HBU setup: Noise, gain, crosstalk, power and signal integrity

- -DAQ Interface

- -LCS with LEDs on board.

Timescale for the first DAQ prototype is under discussion (coupling to the analogue interface of the current DAQ?)

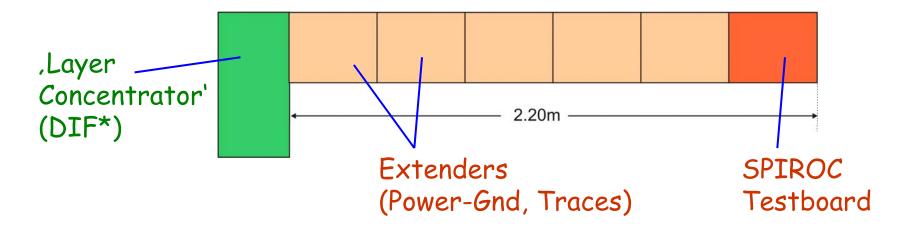

## Testboard III: Power-System

**FEB**

Test Power-Ground System (2.20m)

- -Oscillations when switching?

- -Voltage drop, signal integrity (traces, connectors)?

- -SPIROC performance @ far end (blocking caps sufficient)?

#### Conclusion

- -First ideas about the next generation AHCAL develop to a promising concept.

- -Feasibility of many design aspects (e.g. PCB structure) have to be proved.

- -Testboard Design I (LCS) under development (PCB order mid June 07).

- -Testboard II (HBU prototype) design starts in winter 2007.

- -Testboard III (power plane test) runs in parallel (beginning of 2008).