# Status on CMOS sensors

#### **Auguste Besson**

#### on behalf of

DAPNIA/Saclay, LPSC/Grenoble, LPC/Clermont-F., DESY, Uni. Hamburg, JINR-Dubna & IPHC/Strasbourg contributions from

IPN/Lyon, Uni. Frankfurt, GSI-Darmstadt, STAR coll.(LBNL, BNL)

- > ILC requirements

- > Review on CMOS Performances: state of the art

- > Progress on fast read-out sensors & ADC

- > Roadmap for the coming years

- > Summary

# **ILC** requirements

- Beam background: 1<sup>st</sup> layer: ≥~ 5 hits/cm<sup>2</sup>/BX

- $\triangleright$  (4T, 500 GeV, R<sub>0</sub> = 1.5 cm, no safety factor)

- $\sim 1.8 \times 10^{12} \text{ e}^{\pm}/\text{cm}^2/\text{yr}$  (safety factor of 3)

- occupancy:

- ➤ keep it below ~ few % (cluster multiplicity ~5-10)

- $\triangleright$  aim for a read-out time  $\sim \le 25 \,\mu s$

- ILC vertex detector

- 5−6 cylindrical layers : ~3000 cm²

- 300-500 million pixels (20–40 μm pitch)

- 1st complete ladder prototype ~ 2010

- Read-out speed objectives/ constraints

- column parallel read-out ⊥ to beam axis

- ADC @ the end of each column

- −  $\varnothing$  zero suppression  $\mu$ -circuits.

# Review on CMOS Performances

- Detection efficiency

- Radiation hardness

- Resolution

# General performances

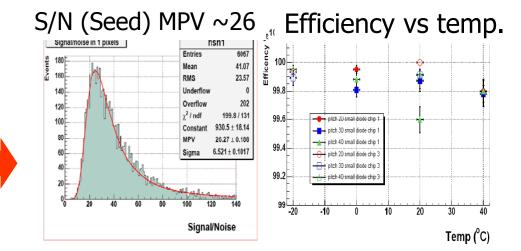

(from H.E. beam tests @ DESY and CERN)

- Charged particle detection well established (analog output)

- best performing technology:

- > AMS 0.35 µm OPTO

- N~ 10 e- ⇒S/N (MPV) 20-30

- > eff>~ 99.5 %

- operating temperature ≥~ 40°C

- macroscopic sensors:

- ➤ MIMOSA-5 (1 Mpix, 3.5 cm²)

- ➤ MIMOSA-20 (=M\*3) (200 kpix, 1x2 cm²)

- ➤ MIMOSA-17 (65 kpix, 0.8 x 0.8 cm<sup>2</sup>)

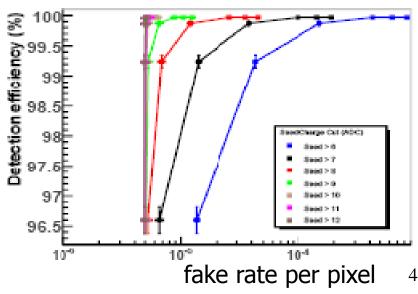

- Efficiency vs rate of fake clusters:

- vary cut on seed pixel:

- $\gt$  6  $\Rightarrow$  12 ADC units (Noise  $\sim$ 1.5 ADC u.)

- vary cut on  $\Sigma$  of crown charge:

- > 0,3,4,9,13,17 ADC units

- eff ~99.9 % for fake rate ~10<sup>-5</sup>

### Radiation hardness: MIMOSA-15

#### Non ionising radiation tolerance

M-15 irradiated with O(1 MeV) neutrons tested with 6 GeV e- beam (DESY)

$$ightharpoonup T = -20 \, ^{\circ}\text{C}, \, t_{\text{r.o.}} \sim 700 \, \mu\text{s}$$

$\gt$  5.8x10<sup>12</sup> n<sub>eq</sub>/cm<sup>2</sup> values

derived with standard and soft cuts

#### Very Preliminary!

| Fluence       | 0                 | 0.47              | 2.1               | 5.8 (5/2)         | 5.8 (4/2)    |

|---------------|-------------------|-------------------|-------------------|-------------------|--------------|

| S/N (MPV)     | <b>27.8</b> ± 0.5 | <b>21.8</b> ± 0.5 | <b>14.7</b> ± 0.3 | <b>≪8.7</b> ± 2.≫ | ≪7.5 ± 2.≫   |

| Det. Eff. (%) | 100.              | $99.9 \pm 0.1$    | $99.3 \pm 0.2$    | 77. $\pm$ 2       | $84. \pm 2.$ |

#### Ionising radiation tolerance

M-15 irradiated with 10 keV X-rays up to 1 MRad (tested @ DESY)

pixels modified against hole accumulation (thick oxide) and leakage current increase (guard ring)

$$F$$

T = -20 °C,  $t_{ro}$  ~ 180  $\mu$ s

$\succ$  t<sub>r o</sub> << 1 ms crucial @ room T

### Very Preliminary!

| Integ. Dose | Noise          | S/N (MPV)                        | Detection Efficiency |  |

|-------------|----------------|----------------------------------|----------------------|--|

| 0           | 9.0 ± 1.1      | 27.8 ± 0.5                       | 100 %                |  |

| 1 MRad      | $10.7 \pm 0.9$ | $\textbf{19.5} \pm \textbf{0.2}$ | 99.96 $\pm$ 0.04 %   |  |

#### Preliminary conclusion

- at least 3 years of running viable @ room T° (or close to)

- further assessment needed

- > test 10 MeV e

- > sensors with integrated CDS, ADC, etc.

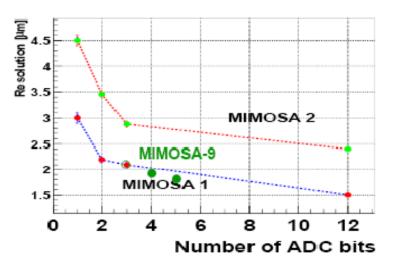

# Spatial Resolution vs ADC resolution

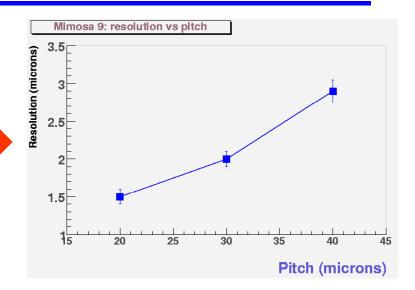

- Single point resolution vs pitch

- hit position reconstructed with eta function, exploiting charge sharing between pixels

- $-\sigma_{sp}\sim 1.5~\mu m$  (20  $\mu m$  pitch)

- obtained with charge encoded on 12 bits.

- $\sigma_{sp}$  dependence on ADC granularity

- minimise number of ADC bits

- > minimise dimensions, t<sub>r.o.</sub>, P<sub>diss</sub>

- effect simulated on real MIMOSA data

(20  $\mu$ m pitch, 120 GeV/c  $\pi$ <sup>±</sup> beam, M9, T=20 °C)

- $> \sigma_{sp} < 2 \mu m$  (4 bits ADC)

- $\succ \sigma_{sp} \sim 1.6\text{-}1.7 \ \mu m \ (5 \ bits \ ADC)$

- results based on simple pixel (N~≤10 e<sup>-</sup>)

- ➤ rad.tol. pixel integrating CDS (N ~≤ 15 e<sup>-</sup>) not yet evaluated

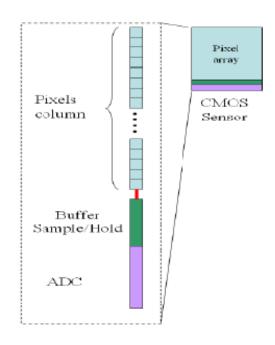

# Fast read-out sensors with // read-out and digital output

Discri. , ADC, ∅ suppression

### Fast read-out architecture

- Parallel development of 3 components

- column // arrays with CDS/pixel and discriminated output

- 4-5 bit ADCs intended to replace discriminators

- − ∅ µcircuits & output memories

- 2 stages approach

- develop sensors for mid-term applications (2009)

(less severe requirements)

- $\triangleright$  EUDET: 1x2 cm<sup>2</sup>, tr.o. ~100 µs, discri. binary charge encoding (no ADC)

- > STAR: 2x2 cm², tr.o. ~200 μs, discri. binary charge encoding (no ADC)

- ⇒ will be operated in real experimental conditions by 2009/2011

- develop ILC sensors (mainly for inner layer) extrapolated from EUDET & STAR

- ➤ increase row rad-out frequency by ~50%

- replace discriminators by ADCs

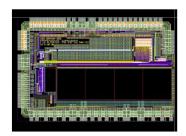

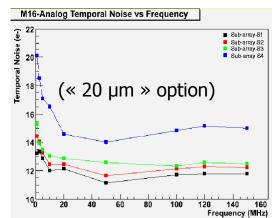

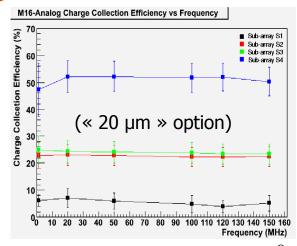

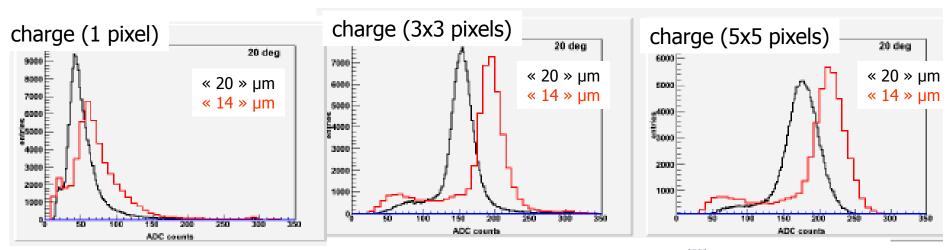

### MIMOSA-16

- Features: M8 (TSMC 0.25 μm) translation in AMS-OPTO 0.35 μm techno.

- ~11 (« 14 ») AND 15  $\mu$ m (« 20 ») epi layer instead of < 7  $\mu$ m

- 32 // columns of 128 pixels (pitch 25 μm), 24 ended with Discriminator

- on pixel CDS; 4 sub arrays (various diode size, rad. hard pixels, enhanced in pixel amplification against noise of read-out chain)

- Preliminary tests of analog part ("20 μm" epi.) performed in Saclay:

- sensors illuminated with  $^{55}$ Fe source and r.o. frequency varied up to ≥~ 150 MHz

- measurements of N(pixel), FPN (end of column),

pedestal variation, CCE (3x3 pixel clusters) vs F<sub>r.o.</sub>

- tests of analog part (« 14 » epitaxy) started in Saclay first results (CCE)

- > noise performance satisfactory (like MIMOSA-8 and -15)

- $\triangleright$  CCE: very poor for S1 (1.7x1.7  $\mu$ m<sup>2</sup>) & poor for S2/S3 (2.4x2.4  $\mu$ m<sup>2</sup>)

- already observed with MIMOSA-15 but more pronounced for "20 μm" option

- suspected origin: diffusion of P-well, reducing the N-well/epitaxy contact, supported by CCE of S4 (4.5x4.5  $\mu m^2$  diode)

- tests of analog part (« 14 »µm epitaxy) started in Saclay

- digital part: June 2007 at IPHC

- beam tests in September 2007 at CERN (T4 H6)

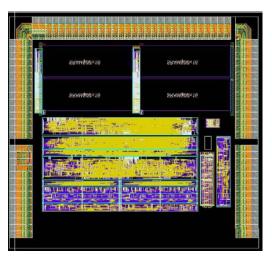

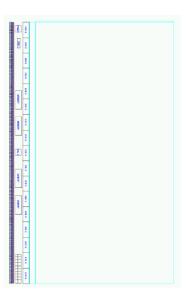

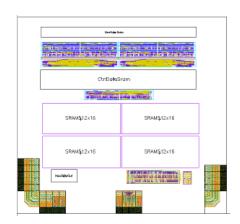

# Zero suppression: Block diagram and 1st proto.

- Chip read-out architecture including digitisation and zero suppression

- pixel array: 1024 x 1024 pixels read-out row by row.

- > 16 groups of rows.

- > ADC at the bottom of each column

- zero suppression algorithm ,

- > find M Hits for each row

- find N Hits for each group \_

N and M determined by occupancy rate

> memory which stores M hits and serial transmission

- 2 step, line by line, logic (adapted to EUDET and STAR):

- > step-1 (inside blocks of 64 columns): identify up to 6 series of 4 neighbour pixels per line delivering signal > discriminator threshold

- step-2 : read-out outcome of step-1 in all blocks and keep up to 9 series of 4 neighbour pixels

- 4 output memories (512x16 bits) taken from AMS I.P. library

- surface 3.6 x 3.6 mm<sup>2</sup>

- status : ➤ design under way

- > submission scheduled for end of June 2007

- back from foundry end of September 2007

- tests completed by end of year

## **ADC Developments**

- Several different ADC architecture under development @IN2P3 and DAPNIA

- LPSC (Grenoble): Ampli + semi-flash (pipe-line) 5- and 4-bit ADC for a column pair

- LPCC (Clermont): flash 4+1.5-bit ADC for a column pair

- DAPNIA (Saclay): Ampli + SAR (4- and) 5-bit ADC

- IPHC (Strasbourg): SAR 4-bit and Wilkinson 4-bit ADCs

| Lab    | proto | Phase  | bits | chan.  | F <sub>r.o.</sub> (MHz) | dim. (µm²) | P <sub>diss.</sub> (μW) | eff. bits | Problems                  |

|--------|-------|--------|------|--------|-------------------------|------------|-------------------------|-----------|---------------------------|

| LPSC   | ADC1  | test   | 5    | 8      | 15-25                   | 43 x 1500  | 1700                    | 4         | Offset & N                |

|        | ADC2  | test   | 5    | 8      | 15-25                   | 43 x 1500  | 1700                    |           |                           |

|        | ADC3  | fab    | 4    | 8      | 25                      | 40 x 943   | 800                     |           |                           |

|        | ADC4  | design | 5    | 8 - 64 | 25                      | 40 X 1100  | 900                     |           |                           |

| LPCC   | ADC1  | test   | 5.5  | 1      | 5(T)-10(S)              | 230 x 400  | 20 000                  | 2.5       | P <sub>diss.</sub> & bits |

|        | ADC2  | fab    | 5.5  | 1      | 10                      | 40 X 1100  | 1000                    |           |                           |

| DAPNIA | ADC1  | test   | 5    | 4      | 4                       | 25 x 1000  | 300                     | ≥~ 2*     | missing bits              |

|        | ADC2  | fab    | 5    | 4      | 4                       | 25 x 1000  | 300                     |           |                           |

| IPHC   | ADC1  | test   | 4    | 16     | 10                      | 25 x 1385  | 660                     |           |                           |

|        | ADC2  | test   | 4    | 16     | 10                      | 25 x 1540  | 545                     |           |                           |

- First mature ADC (LPSC) design expected to come out before spring 2008

- > submission of 1st col. // pixel array prototype hosting integrated ADCs in spring 2008

- ➤ integrated Ø zero supp. in 2009

# Miscellaneous

Roadmap & other developments

# roadmap / other developments

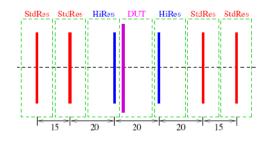

#### EUDET

- 2 arms of 3 planes (1-2 high resolution plane)

- provide ~1 μm resolution on 3 GeV e− beam (DESY)

- 2 steps: 2007 (analog outputs) & 2009 (digital outputs)

#### STAR

- 2 cylindral layers: 2000/3000 cm<sup>2</sup>

- 500 millions pixels (30 μm pitch)

- resolution requirements ~≤ 8 μm

- non ionising radiation hardness (@ room T)

- MIMOSA-8 results :  $\sim$  7-8  $\mu$ m resolution with a 25  $\mu$ m pitch

- ⇒ discri output, with pitch ≤ 20 μm

- 2 steps: 2008 (analog outputs) & 2011 (digital outputs)

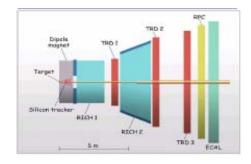

#### CBM

- 3 rectangular layers: 2000 cm<sup>2</sup>

- 200–300 milion pixels ( 20–30 μm pitch)

### MIMOSTAR-3 (=M-20)

#### Features

- AMS-OPTO engineering run, fabricated in summer 2006.

- 2+4 wafers; 2 epi layers options (« 14 » & « 20 »  $\mu$ m)

- 200 k-pixels, ~2 cm<sup>2</sup>,  $t_{r.o.}$  ~ 4 ms

#### Applications

- STAR: first step (analog output)

- EUDET: demonstrator (1kframe/s) adapted for standard resolution plane

- ILC: discri replaced by ADC ⇒ fulfill Layers 3-4-5 requirements.

MIMOSA-20 ("14" & "20"  $\mu m$  epitaxy) illuminated with  $^{55}$ Fe source

ightarrow CCE ("14"  $\mu m$ )  $\sim$  30–40 % higher than CCE ("20"  $\mu m$ )

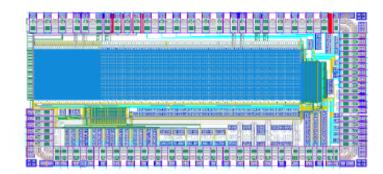

### Next prototype with column // architecture : MIMOSA-22

- Extension of MIMOSA-16

- > ⇒ larger surface, smaller pitch, optimised pixel, JTAG, more testability

- Pixel characteristics (still under studies)

- pitch =  $18.4 \mu m$  (compromise resolution/pixel layout)

- diode surface  $\sim 10-20 \ \mu m^2$  (to optimise charge coll. eff. & gain)

- 64 columns ended with discriminator

- 8 columns with analog output (test purposes)

- $\ge 8$  sub-matrices ( $\ge 4$  pixels designs w/o ion. rad. tol. diode)

- > active digital area : 64 x 544-576 pixels

- Status ⇒ design underway @ IPHC and DAPNIA.

- submission end of September 2007

### Roadmap towards the Final Chip for EUDET & STAR ⇒ILC

- Spring 2008: MIMOSA-22+

- MIMOSA-22 +  $\varnothing$  (SUZE-01)

- 1 or 2 subarrays

- large surface:  $\sim 1 \times 0.5$  cm<sup>2</sup> ( $\sim 500$  pixels in column)

- $\geq \sim \frac{1}{4}$  of final number of columns (256 / 1088)

- extension of MIMOSA-22+

- 1088 col x 544/576 pixels (1x2 cm²) ⇒engineering run

- read-out time  $\sim 100 \mu s$

- incorporate ADC (with integrated discrimination) ⇒ outer layers

- increase frequency by ~ 50 % (new Ø and memory design)⇒ inner layers

# **Summary**

- CMOS sensors developed for running conditions

- > with beam background >> MC simulation (sizeable occupancy uncertainty)

- General performances well established

- eff., S/N, fake hits, resolution, rad. hardness, moderate cooling

- AMS 0.35 μm OPTO techno assessed. ⇒Baseline for R & D

- new generation of full scale sensors underway:

- > real experimental conditions: equip STAR, EUDET, CBM demonstrator in 2007/2008

- Fast read-out sensors progressing steadily

- column // architecture with integrated discri. operationnal

- ADCs close to final design

- — Ø μcircuits: 1<sup>st</sup> generation close to fabrication

- Milestones

- EUDET/STAR: final sensors with discri. binary charge encoding (2009 and 2010 resp.)

- replace discris by ADCs. Increase final read-out frequency

- find the final fabrication process ( $\sim$ < 0.2 µm)

- Not covered by this talk:

- integration issues

- thinning : (see Marco/Devis talk)

- exploration of new fab. process (ST μ-electronics 0.25 μm) ⇒M21 under test.

# back up slides

# Constraints from beamstrahlung

```

lacksquare 1st layer (L0) : \gtrsim 5 hits/cm^2/BX for 4T / 500 GeV / {f R}_0 = 1.5 cm / no safety factor

\Rightarrow \lesssim 1.8 \cdot 10^{12} \text{ e}^{\pm}/\text{cm}^2/\text{yr} (safety factor of 3)

2nd layer: 8 times less (direct)

3rd layer: 25 times less (direct)

Consequences on Occupancy in 1st layer (L0): \lesssim 0.9 % hit occupancy in 50 \mu s (r.o. time of TESLA TDR)

\hookrightarrow signal spread on \lesssim 4.5–9 % pixels (cluster multiplicity \sim 5-10)

\Rightarrow 1) aim for shorter read-out time in L0 than in TDR \mapsto typically \lesssim 25 \mu s

(compromise with power dissipation, multiple scattering, ...)

2) aim for shorter read-out time in L1 than in TDR \rightarrow typically \sim 50 \mu s (vs 250 \mu s)

and presumably smaller radius (e.g. \sim 20 – 22 mm)

(use tracks extrapolated from L1-4 down to L0)

3) aim for relaxed read-out time in L2, L3, L4: \sim 100 – 200 \mu s (vs 250 \mu s)

\hookrightarrow depends on backscattered e^\pm rate

Consequences on Radiation Tolerance in L0:

st dose integrated over 3 years: \lesssim 5.4·10^{12} e/cm^2 \longrightarrow \lesssim 2·10^{11} n_{eq}/cm^2 (NIEL \sim 1/30)

\diamond neutron dose integrated over 3 years much smaller : \lesssim 3 \cdot 10^{10} \; n_{eq}/{\rm cm}^2 (safety factor of 10)

```

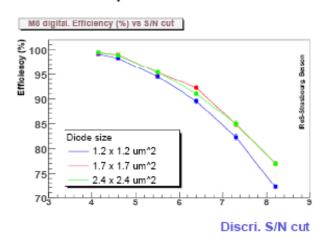

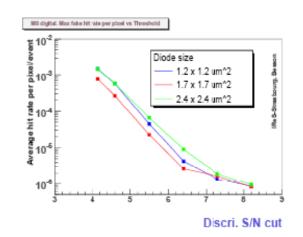

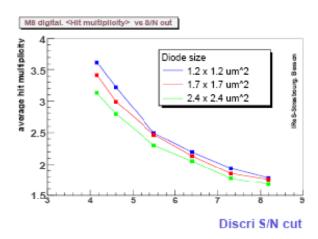

### MIMOSA-8

- MIMOSA-8: TSMC 0.25  $\mu m$  digital fab. process (< 7  $\mu m$  epitaxy)

- ullet 32 // columns of 128 pixels (pitch: 25  $\mu m$ )

- ullet read-out time  $\sim$  50  $\mu s$  (resp. 20  $\mu s$ ) with (resp. without) DAQ

- on-pixel CDS

- discriminator (and DS) integrated at end of each of 24 columns

■ Detection performance with 5 GeV/c e beam (DESY):

- Excellent m.i.p. detection performances despite modest thickness of epitaxial layer

- st det. eff.  $\sim$  99.3 % for fake rate of  $\sim$  0.1 %

- st discri. cluster mult.  $\sim$  3–4

- $*P_{diss} \lesssim$  500  $\mu$ W / col.

- >> Architecture validated for next steps: techno. with thick epitaxy, rad. tol. pixel at Troom. ADC. Ø. etc.

#### APPENDIX A: Summary of fabricated MIMOSA sensors mentionned in the report

```

MIMOSA-8

fabrication.

2003 - TSMC-0.25 techno. - epitaxy thickness < 7 \mu m

25 μm pitch - 128 rows - 24/8 col. with digital/analog output - 4 sub-arrays with different pixels

geometry

column parallel read-out - clock frequency \geq 100 \text{ MHz} - row read-out frequency \sim 6 \text{ MHz}

features

MIMOSA-9

2003 - AMS-0.35 OPTO techno. - epitaxy thickness \sim 11 \ \mu m (also with "high-res" substrate without epitaxy)

fabrication

geometry

20, 30 & 40 μm pitch - various pixel architectures

technology exploration - analog output - serial read-out

features

2005 - AMS-0.35 opto techno. - epitaxy thickness \sim 11~\mu m

MIMOSA-11 fabrication

20 & 30 μm pitch - 106x106 pixels - 4 sub-arrays

geometry

analog output - serial read-out

features

MIMOSA-14 fabrication

2005 - AMS-0.35 opto techno. - epitaxy thickness \sim 11~\mu m

30 \mu m pitch - 2 groups of 64x128 pixels

geometry

features

STAR prototype - ionising rad. tol. pixels - analog output - serial read-out

2005 - AMS-0.35 opto techno. - epitaxy thickness \sim 11~\mu m

MIMOSA-15 fabrication

20 & 30 μm pitch - 4 sub-arrays with various pixels

geometry

non-ionising rad.tol. pixels - analog output - serial read-out

features

MIMOSA-16 fabrication

2006/7 - AMS-0.35 opto techno. - epitaxy thickness \sim 11 \& 15 \ \mu m

25 μm pitch - 128 rows - 24/8 col. with digital/analog output - 4 sub-arrays with different pixels

geometry

column parallel read-out - clock frequency \geq 100 \text{ MHz} - row read-out frequency \gtrsim 6 \text{ MHz}

features

MIMOSA-17 fabrication

2006/7 - AMS-0.35 opto techno. - epitaxy thickness \sim 11 \& 15 \ \mu m

30 \mu m pitch - 4 groups of 64x256 pixels

geometry

EUDET demonstrator - 4 analog outputs - serial read-out inside each group

features

MIMOSA-18 fabrication

2006/7 - AMS-0.35 opto techno. - epitaxy thickness \sim 11 \& 15 \ \mu m

10 \mu m pitch - 512x512 pixels

geometry

EUDET sensor - sub-micron resolution - analog output - serial read-out inside each group

features

2006/7 - AMS-0.35 opto techno. - epitaxy thickness \sim 11 \& 15 \ \mu m

MIMOSA-20 fabrication

30 μm pitch - ionising rad tol.pixels - 2 groups of 320x320 pixels

geometry

STAR demonstrator (final prototype) - 2 analog outputs - serial read-out inside each group

features

MIMOSA-21 fabrication

2006 - STM-0.25 BICMOS techno. - sensitive volume includes "high-res" substrate

128x192 pixels with 10 \mu m pitch - 64x96 pixels with 20 \mu m pitch

geometry

beta-imager - analog outputs - serial read-out

features

```

#### APPENDIX B: Sensors and micro-circuits to be fabricated $\leq 2010$

| MIMOSA-22<br>(for EUDET<br>and STAR.) | fabrication<br>geometry<br>features | 2007 - AMS-0.35 OPTO techno epitaxy thickness $\sim 11~\mu m$<br>18 $\mu m$ pitch - 500-600 rows - 64/8 col. with digital/analog output - 6-8 sub-arrays with different pixels col. parallel read-out - clock frequency $\geq 100~{\rm MHz}$ - row read-out frequency $\sim 6~{\rm MHz}$                      |

|---------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUZE-01<br>(for EUDET & STAR.)        | fabrication<br>features             | 2007 - AMS-0.35 OPTO techno no epitaxy<br>zero suppression logic & memories - specific to EUDET & STAR.                                                                                                                                                                                                       |

| MIMOSA-22+E<br>(for EUDET)            | fabrication<br>geometry<br>features | 2008 - AMS-0.35 opto techno epitaxy thickness $\sim 11~\mu m$<br>18 $\mu m$ pitch - 500-600 rows - $\geq$ 256 col. with digital output - $\leq$ 2 sub-arrays with different pixels col. parallel read-out with integ. zero suppression - clock frequency $\geq$ 100 MHz - row read-out frequency $\sim$ 6 MHz |

| MIMOSA-22+S<br>(for STAR.)            | fabrication<br>geometry<br>features | 2008 - AMS-0.35 opto techno epitaxy thickness $\sim 11~\mu m$<br>18 $\mu m$ pitch - 1088 rows - $\geq$ 256 col. with digital output - $\leq$ 2 sub-arrays with different pixels col. parallel read-out with integ. zero suppression - clock frequency $\geq$ 100 MHz - row read-out frequency $\sim$ 6 MHz    |

| MIMOSA-22++E<br>(for EUDET)           | fabrication<br>geometry<br>features | 2008/2009 - AMS-0.35 opto techno epitaxy thickness $\sim 11~\mu m$<br>18 $\mu m$ pitch - 500-600 rows - 1088 col. with digital output<br>final chip equipping telescope - col. parallel read-out with integ. zero suppression - read-out time $\sim 100~\mu s$                                                |

| MIMOSA-22++S<br>(for STAR.)           | fabrication<br>geometry<br>features | 2009 - AMS-0.35 OPTO techno epitaxy thickness $\sim 11~\mu m$<br>18 $\mu m$ pitch - 1088 rows - 1088 col. with digital output<br>final chip for HFT col. parallel read-out with integ. 0 supp read-out time $\lesssim 200~\mu s$                                                                              |

| ADC<br>(for ILC)                      | fabrication<br>features             | 2007/2008 - AMS-0.35 opto techno no epitaxy various architectures - $4$ or $5$ bits - $\geq 8$ channels - specif. for EUDET & STAR.                                                                                                                                                                           |

| MIMOSA16+<br>(for ILC)                | fabrication<br>geometry<br>features | 2008 - AMS-0.35 opto techno epitaxy thickness $\sim 11~\mu m$<br>20-22 $\mu m$ pitch - 256-320 rows - $\geq$ 64 col. with digital output - $\geq$ 2 sub-arrays with different pixels col. parallel read-out with integ. ADC                                                                                   |

| SUZE-02<br>(for ILC)                  | fabrication<br>features             | 2008 - AMS-0.35 opto techno no epitaxy<br>0 suppression micro-circuits & memories - specific to ILC                                                                                                                                                                                                           |

| MIMOSA-X                              | fabrication                         | $2008/2009$ - various technologies with $< 0.2~\mu m$ feature size                                                                                                                                                                                                                                            |

| ADC-X                                 | fabrication                         | $2008/2009$ - various technologies with $< 0.2~\mu m$ feature size                                                                                                                                                                                                                                            |

| SUZE-X                                | fabrication                         | $2008/2009$ - selected technology with $< 0.2~\mu m$ feature size                                                                                                                                                                                                                                             |

| MIMOSA16++<br>(for ILC)               | fabrication<br>geometry<br>features | 2009 - AMS-0.35 opto techno.? - epitaxy thickness $\sim 11~\mu m$ ? 20-22 $\mu m$ pitch - 256-320 rows - $\geq$ 256 col. with digital output - $\leq$ 2 sub-arrays with different pixels col. parallel read-out with integ. ADC & zero suppression                                                            |

| MIMOSA16+++<br>(for ILC)              | fabrication<br>geometry<br>features | 2010 - technology? 20-22 $\mu m$ pitch - 256-320 rows - $\geq$ 256 col. with digital output - $\leq$ 2 sub-arrays with different pixels final sensor - col. parallel read-out with integ. ADC & 0 suppression                                                                                                 |

# Zero suppression: Block diagram and 1st proto.

- SUZE-01: small fully digital prototype in AMS 0.35 μm

- 2 step, line by line, logic (adapted to EUDET and STAR):

- > step-1 (inside blocks of 64 columns): identify up to 6 series of 4 neighbour pixels per line delivering signal > discriminator threshold

- > step-2 : read-out outcome of step-1 in all blocks and keep up to 9 series of 4 neighbour pixels

- 4 output memories (512x16 bits) taken from AMS I.P. library

- surface 3.6 x 3.6 mm<sup>2</sup>

- status : > design under way

- > submission scheduled for end of June 2007

- back from foundry end of September 2007

- tests completed by end of year

| Labs   | No. of Chip | Phase*<br>(D. F. T.) | No. of Bits | No. Of channels | Freq. of<br>Readout<br>(MHz) | Dimension<br>(µm²)   | Power                        | Effective<br>No. of Bits | Pb?                   |

|--------|-------------|----------------------|-------------|-----------------|------------------------------|----------------------|------------------------------|--------------------------|-----------------------|

| LPSC   | 2           | Т                    | 5           | 8               | 15 - 25                      | 43x1500<br>(1 ADC→2) | 1700 μW<br>(1 ADC→2)         | 4                        | Offset<br>Digit noise |

|        | 1           | F                    | 4           | 8               | 25                           | 40x943<br>(1 ADC→2)  | 800 μW<br>(1 ADC <b>→</b> 2) |                          |                       |

|        | 1           | D                    | 5           | +8- < 64        | 25                           | 40x1100<br>(1 ADC→2) | 900 μW<br>(1 ADC <b>→</b> 2) |                          |                       |

| Labs   | No. of Chip | Phase*<br>(D. F. T.) | No. of Bits | No. Of channels | Freq. of<br>Readout<br>(MHz) | Dimension<br>(µm²)   | Power                        | Effective<br>No. of Bits | Pb?                   |

| LPCC   | 1           | Т                    | 5.5         | 1               | 5 Test<br>10 Sim             | 230x400              | 20000 μW                     | 2.5                      | Power x20             |

|        | 1           | F                    | 5.5         | 1               | 10                           | 40x1100              | 1000 μW                      |                          |                       |

| Labs   | No. of Chip | Phase*<br>(D. F. T.) | No. of Bits | No. Of channels | Freq. of<br>Readout<br>(MHz) | Dimension<br>(µm²)   | Power                        | Effective<br>No. of Bits | Pb?                   |

| DAPNIA | 1           | Т                    | 5           | 4               | 4                            | 25x1000              | 300 µW                       | 2 - 5**                  | Missing bits          |

|        | 1           | F                    | 5           | 4               | 4                            | 25x1000              | 300 μW                       |                          | Offset nonlinearity   |

| Labs   | No. of Chip | Phase*<br>(D. F. T.) | No. of Bits | No. Of channels | Freq. of<br>Readout<br>(MHz) | Dimension (µm²)      | Power                        | Effective<br>No. of Bits | Pb?                   |

| IPHC   | 1           | Т                    | 4           | 16              | 10                           | 25x1385              | 660 µW                       |                          |                       |

|        | 1           | Т                    | 4           | 16              | 10                           | 25x1540              | 545 μW                       |                          | 24                    |

<sup>\*</sup> D: Design, F: Fabrication, T: Test

<sup>\*\* 2</sup> bits if LSB=1 mV, 5 bits if LSB = 20 mV