#### ALCPG07, Fermilab, October 22 - 25, 2007

#### SOI Sensor Development at LBNL

Lindsay Glesener University of California, Berkeley Lawrence Berkeley National Laboratory

M. Battaglia, D. Contarato, P. Denes, P. Giubilato, C.Q.Vu

# Outline

- Introduction: Description of the SOI sensor prototype

- Single transistor tests

- Back-gating effect

- Irradiation studies

- Analog pixel tests

- Laser studies: charge collection properties

- Leakage current

- Depletion region

- Beam test with 1.35 GeV electrons

- Digital pixel tests: Electron beam test results

Lindsay Glesener UC-Berkeley & LBNL

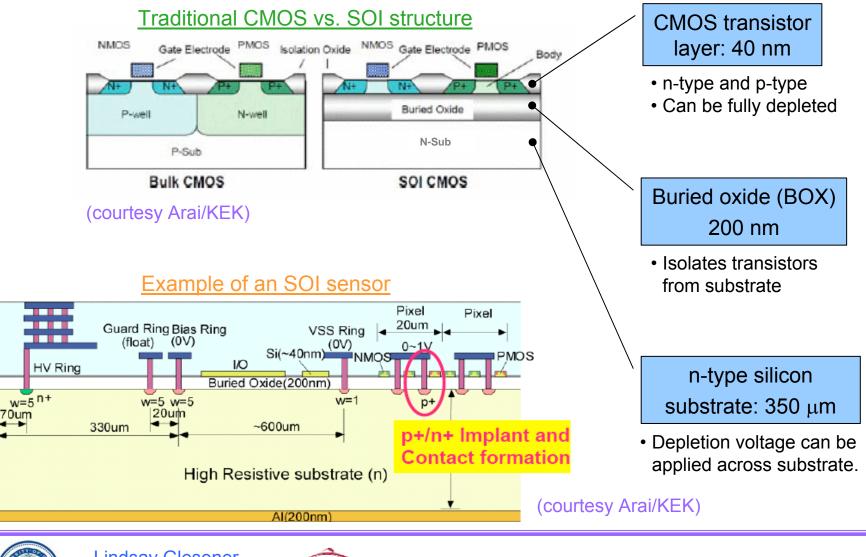

## 0.15 μm OKI FD-SOI process

Lindsay Glesener UC-Berkeley & LBNL

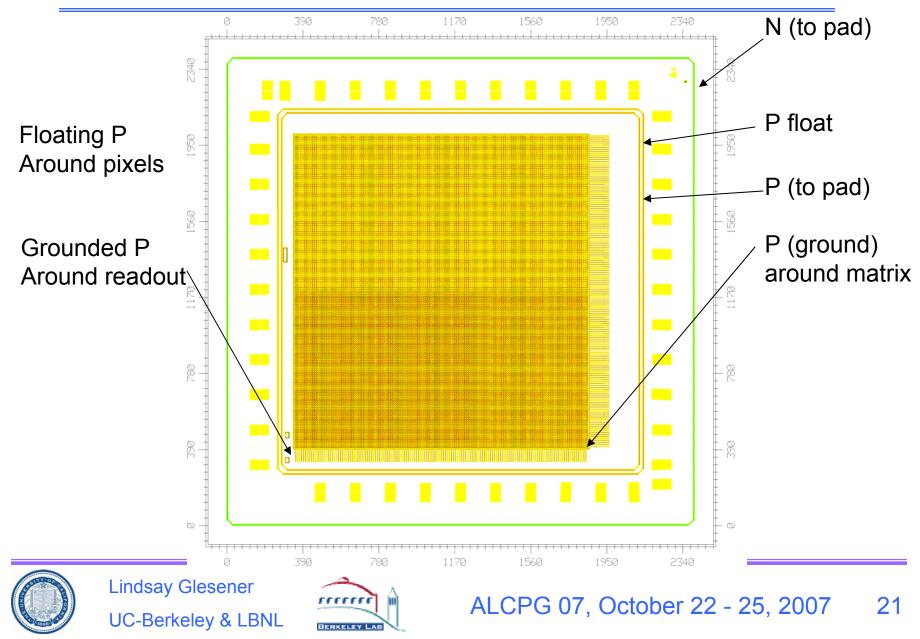

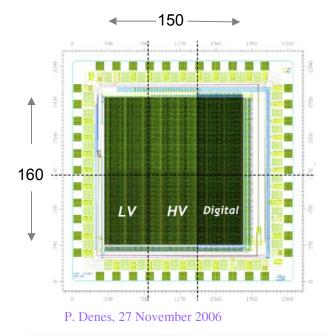

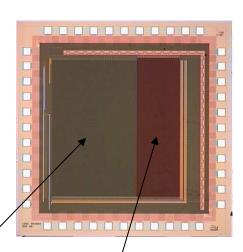

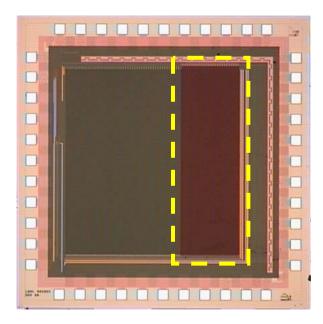

## LDRD-SOI at LBNL

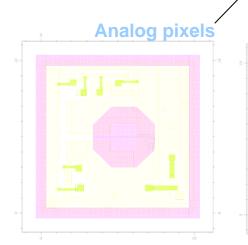

#### • Pixels:

- $-10 \ \mu m$  pitch

- -160 x 150 matrix

- Diodes: 1µm to 4µm diameter

- -Floating p-type guard-ring around each pixel

- 2 sections with analog pixels

- Simple 3T structure

- Biased at 1.0V (LV) and 1.8V (HV)

- 1 section with digital pixels

- simple comparator and latch architecture

- 15 transistors per pixel

Lindsay Glesener UC-Berkeley & LBNL

## Single transistor tests

- 18 test transistors

- p-type and n-type

- 1.0V and 1.8V bias

- Various body contacts: floating, source, gate

- W = 50 $\mu$ m, L = 0.3 $\mu$ m

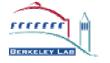

- Input and output characteristics measured for different depletion voltages

- Backgating causes a shift in threshold voltage as the substrate voltage increases.

Lindsay Glesener UC-Berkeley & LBNL

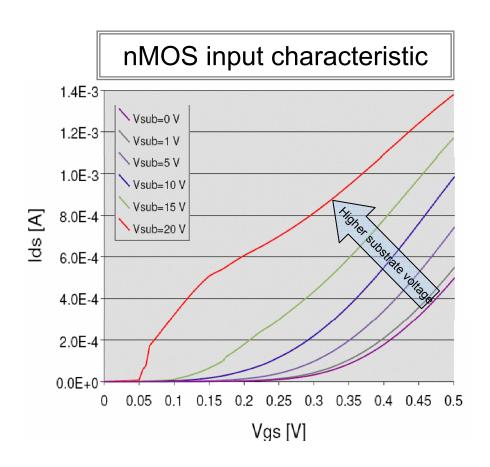

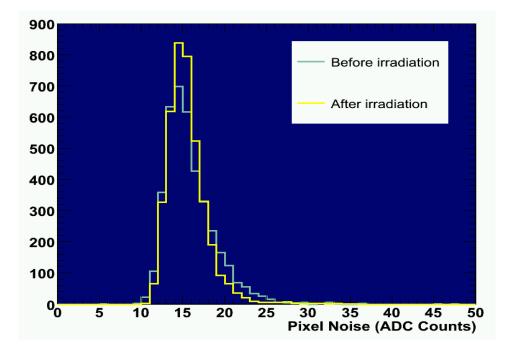

## Irradiation effects

- Irradiations performed at LBNL 88" Cyclotron

- **30 MeV protons**: fluence up to 2.5 x 10<sup>12</sup> p/cm<sup>2</sup>

- Transistor measurements show a shift in threshold voltage throughout irradiation.

- Charge trapping in BOX increased backgating

- **1-20 MeV neutrons**: fluence up to 10<sup>11</sup> n/cm<sup>2</sup>

- No change in transistor characteristics

Lindsay Glesener UC-Berkeley & LBNL

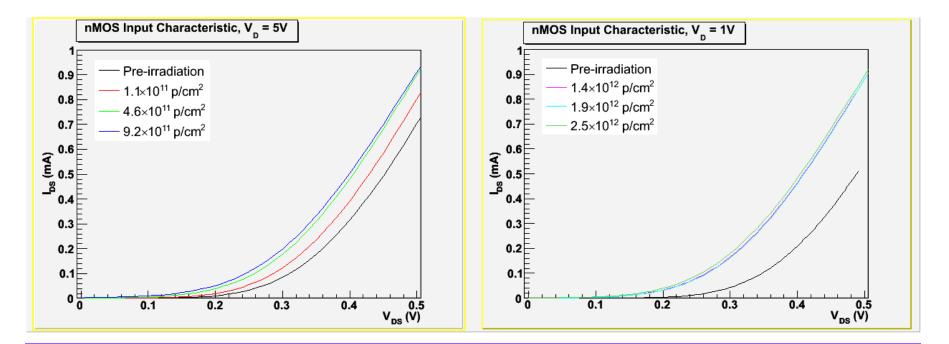

## Laser studies

Charge collection properties of the SOI were tested with 850nm and 1060nm lasers focused to a ~20um spot.

- Signal loss was noted at long integration times.

- More loss at large substrate voltages

- Combined effect of leakage current and backgating

- <u>To retain the entire signal,</u> <u>pixels must be read out</u> <u>immediately following charge</u> <u>collection.</u>

Lindsay Glesener

UC-Berkeley & LBNL

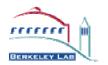

## Leakage current: Effects of cooling

- Noise and leakage current were studied at temperatures down to -10°C

- Each pixel is read twice and the difference in ADC counts is computed --> correlated double sampling

- Fixed integration time between readings:1.384 ms

- Decrease in leakage current at lower temperatures

Lindsay Glesener UC-Berkeley & LBNL

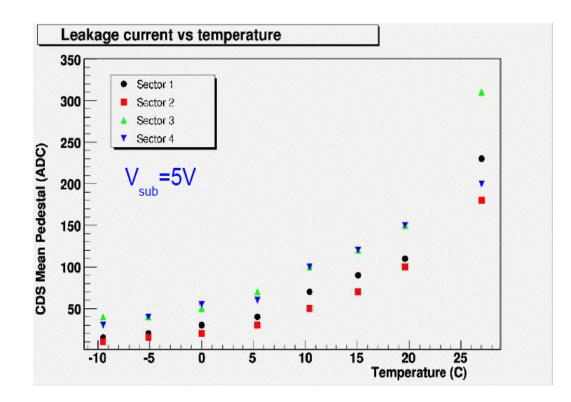

## Depletion region vs substrate voltage

Depletion region

thickness

$$D \propto \sqrt{V_d}$$

- 1060 nm laser signal for different substrate voltages

- Good agreement with expected depletion region up to V<sub>d</sub> ~ 10V

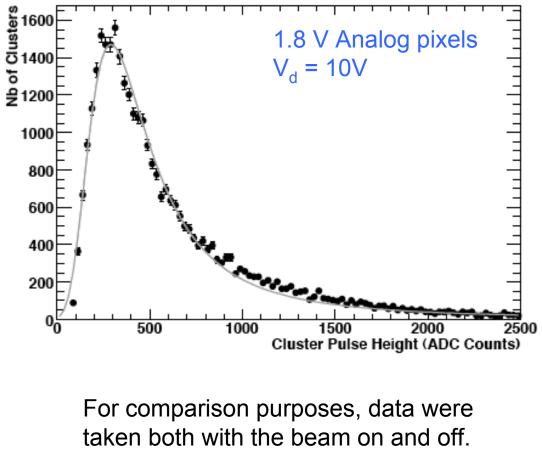

#### Electron beam tests: Analog sectors

1.35 GeV electrons extracted from the booster ring of the Advanced Light Source (ALS) at LBNL.

to appear in NIM A (2007)

Lindsay Glesener UC-Berkeley & LBNL

## Electron beam tests: Analog sectors

|                       | 1.0 V Analog Pixels           |                                |                            |                         |  |  |  |

|-----------------------|-------------------------------|--------------------------------|----------------------------|-------------------------|--|--|--|

| V <sub>d</sub><br>(V) | Clusters / Spill<br>(Beam on) | Clusters / Spill<br>(Beam off) | Signal MPV<br>(ADC Counts) | Average<br>Signal/Noise |  |  |  |

| 1                     | 3.9                           | 0.02                           | 105                        | 7.4                     |  |  |  |

| 5                     | 6.7                           | 0.03                           | 140                        | 8.8                     |  |  |  |

| 10                    | 4.4                           | 0.03                           | 164                        | 8.1                     |  |  |  |

| 15                    | 1.4                           | 0.02                           | 123                        | 6.5                     |  |  |  |

|                       | 1.8 V Analog Pixels           |                                |                            |                         |  |  |  |

|-----------------------|-------------------------------|--------------------------------|----------------------------|-------------------------|--|--|--|

| V <sub>d</sub><br>(V) | Clusters / Spill<br>(Beam on) | Clusters / Spill<br>(Beam off) | Signal MPV<br>(ADC Counts) | Average<br>Signal/Noise |  |  |  |

| 1                     | 9.7                           | 0.05                           | 132                        | 8.9                     |  |  |  |

| 5                     | 14.0                          | 0.12                           | 242                        | 14.9                    |  |  |  |

| 10                    | 7.8                           | 0.20                           | 316                        | 15.0                    |  |  |  |

| 15                    | 3.9                           | 0.01                           | 301                        | 13.6                    |  |  |  |

to appear in NIM A (2007)

Lindsay Glesener UC-Berkeley & LBNL

# Digital pixels

- Structure

- In-pixel comparator plus latch

- Adjustable threshold

- No internal amplification

- No static power dissipation

- Digital circuitry active only during sampling

- Readout

- No CDS or pedestal needed

- Adjustable integration time

- Reduced problem of charge loss due to leakage current

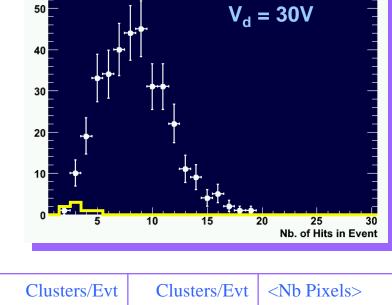

## Digital pixels: ALS results

50

- Noticeable charge collected only at high substrate voltages (but not too high!)

- Analog threshold is affected by backgating

- Large depletion: increased charge signal

- At 25-30V, these effects seem to combine for best detection capabilities.

- Cluster multiplicity decreases with increasing substrate voltage

- Single transistor test data collection in progress

- Model back-gating effect

- Understand effect on pixel threshold

| V <sub>d</sub><br>(V) | Clusters/Evt<br>w/ beam | Clusters/Evt<br>w/o beam | <nb pixels=""></nb> |

|-----------------------|-------------------------|--------------------------|---------------------|

| 20                    | 3.62                    | 0.04                     | 1.78                |

| 25                    | 5.81                    | 0.04                     | 1.32                |

| 30                    | 8.31                    | 0.04                     | 1.26                |

| 35                    | 1.60                    | 0.01                     | 1.14                |

Lindsay Glesener **UC-Berkeley & LBNL**

## **Conclusions and Plans**

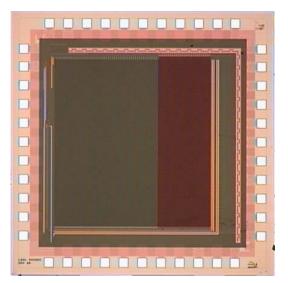

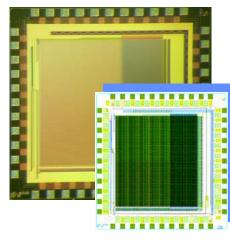

- First OKI 0.15µm FD-SOI pixel prototype designed and successfully tested at LBNL

- Analog and digital pixel detection capabilities have been demonstrated with infrared lasers and 1.35 GeV electrons

- Up to 10-15V for analog pixels

- 20-30V for digital pixels

- Backgating effects become significant at high substrate voltages and after irradiation with protons

- Further electron beam tests at the ALS under way

- Pairing with a 50  $\mu$ m thin MIMOSA-5 sensor to normalize flux and correlate hits

- Detailed laser studies

- Consistency of threshold across digital pixels

- Uniformity scan of analog pixels

- New prototype submission in December/January in optimized 0.20µm process

- Repeat simple architecture + added functionalities

#### **Backup Slides**

Lindsay Glesener UC-Berkeley & LBNL

## Neutron irradiation

- Neutron irradiation:

- Fluence up to 10<sup>11</sup> n/cm<sup>2</sup>

- 1-20 MeV neutrons

- Readout at 6.25 MHz pixel clock

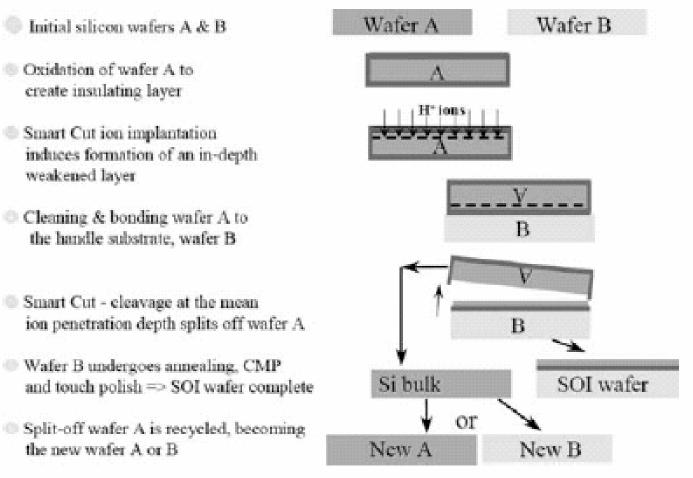

#### **UNIBOND** Process

#### Y. Arai, "Electronics and Sensor Study with the OKI SOI process", TWEPP-07

Lindsay Glesener UC-Berkeley & LBNL

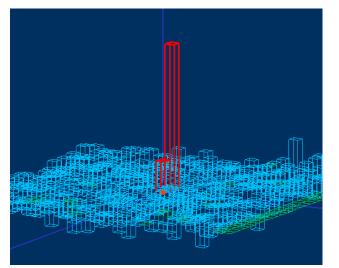

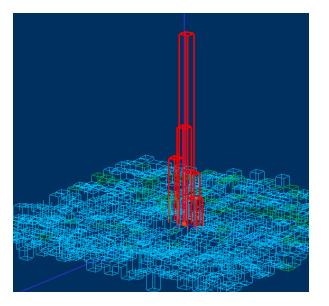

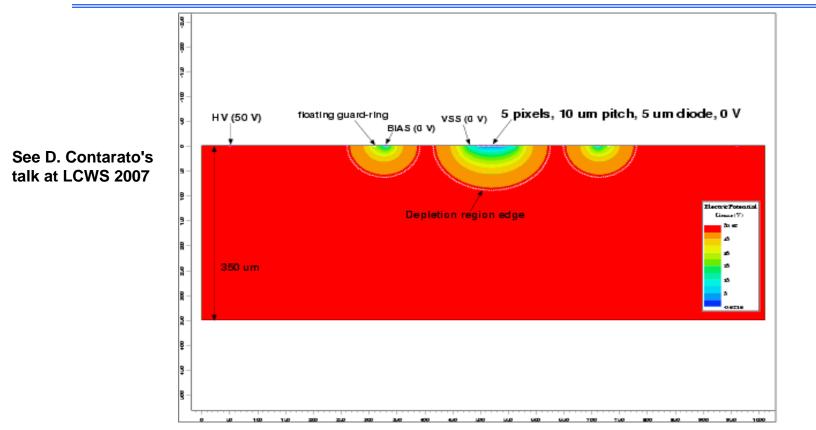

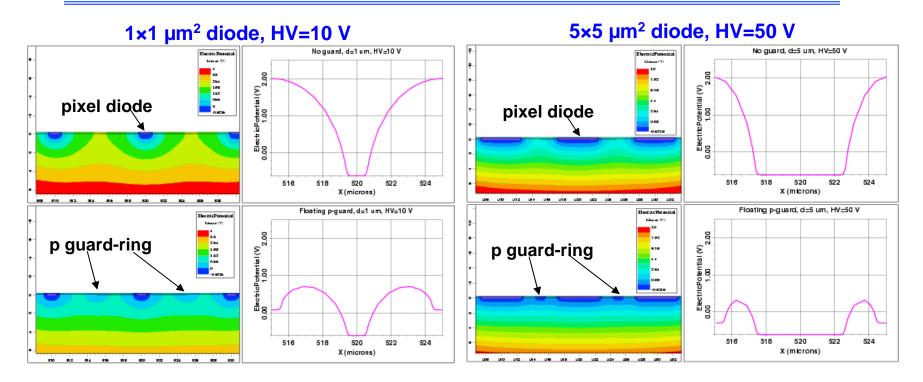

#### **TCAD Simulations**

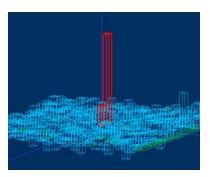

- . Simulation performed with Synopsys TCAD (Taurus Device)

- . 2D model of 5 pixel cluster (10  $\mu m$  pixel pitch) and substrate contact regions

- 350 μm thick substrate, n-type silicon (6×10<sup>12</sup> cm<sup>-3</sup>); 200 nm buried oxide

- Different diode sizes (1×1 µm<sup>2</sup> and 5×5 µm<sup>2</sup>)

## Surface potential, choice of pixel guard-ring

- . Pixel surface potential for different diode sizes and depletion voltages

- . Potential in-between pixels too high, especially for smaller diode size

- ${\ }$  Add floating p-guard structure (1  $\mu m$  wide) to keep potential low and limit back-gate effects on MOS transistors on top of buried oxide

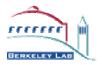

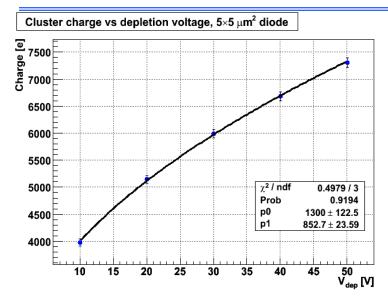

### Charge collection simulation

$\hfill \ \hfill \ \$

- Study collected signal as a function of depletion voltage and of track position within hit pixel

- Total cluster signal ~constant as a function of position within hit pixel

- Most of the charge is collected in hit pixel, expect larger cluster size for smaller diode pitch

Lindsay Glesener UC-Berkeley & LBNL

ALCPG 07, October 22 - 25, 2007

20

#### N and P substrate connections