# Design of a 16 bit ∑∆ DAC for ECAL calibration Status report

1

#### D. Dzahini, L. Gallin-Martel, O. Rossetto, C. Vescovi

Laboratoire de Physique Subatomique et de Cosmologie, Grenoble

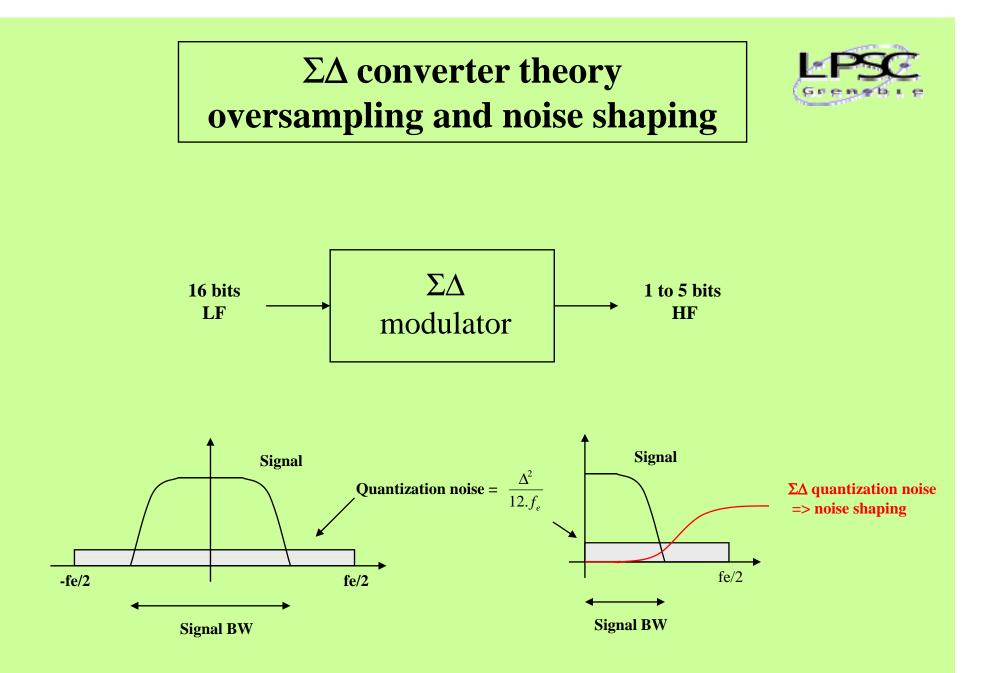

- Theory

- $-\Sigma\Delta$  modulators

- 1<sup>st</sup> order modulator implementation

- Design

- Modulator

- Dynamic Element Matching

- SC DAC

- SC Filter

- Conclusion Remaining tasks

Calice Meeting – Prague September 12<sup>th</sup> 2007

Signal to Noise Ratio of ideal converters

Nyquist rate converters :  $SNR_{db} = 6.02 \times N + 1.76$

Oversampled converters :  $SNR_{db} = 6.02 \times N + 1.76 + 10\log(OSR)$

$\Sigma\Delta$  converters :

$$SNR_{db} = 10\log(3\frac{2k+1}{\pi^{2k}} \times 2^{2N-1} \times OSR^{2k+1})$$

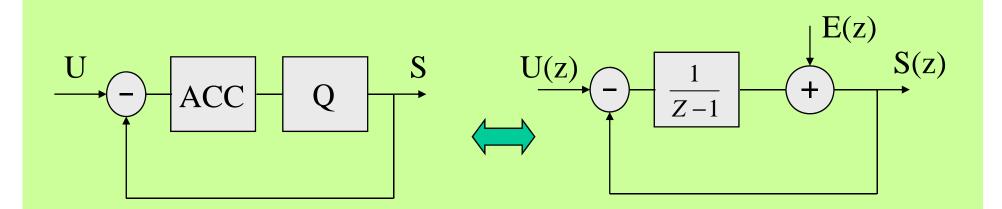

with N : number of bit OSR : oversampling ratio k : modulator order First order  $\Sigma\Delta$  modulator DAC implementation (1)

E(z) : quantization noise

$$\begin{cases} S(z) = z^{-1}U(z) + (1 - z^{-1})E(z) \\ STF = Z^{-1} \\ NTF = 1 - Z^{-1} \text{ (high pass filter)} \end{cases}$$

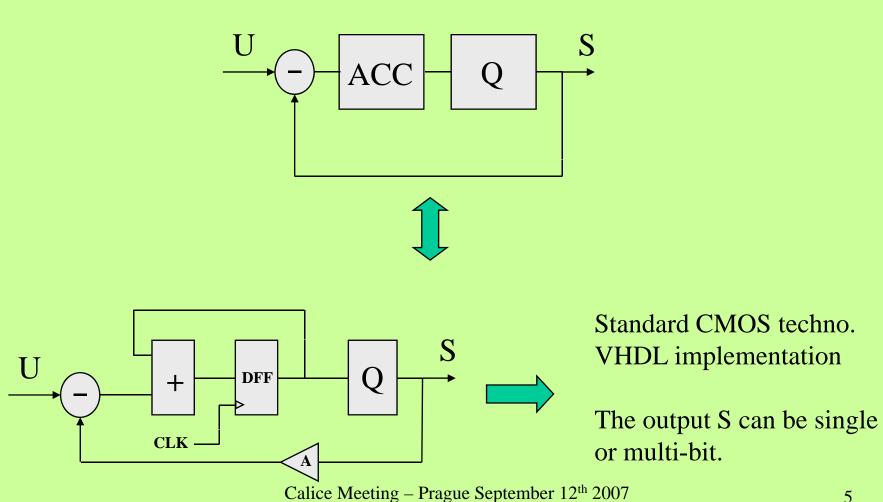

First order  $\Sigma\Delta$  modulator **DAC implementation (2)**

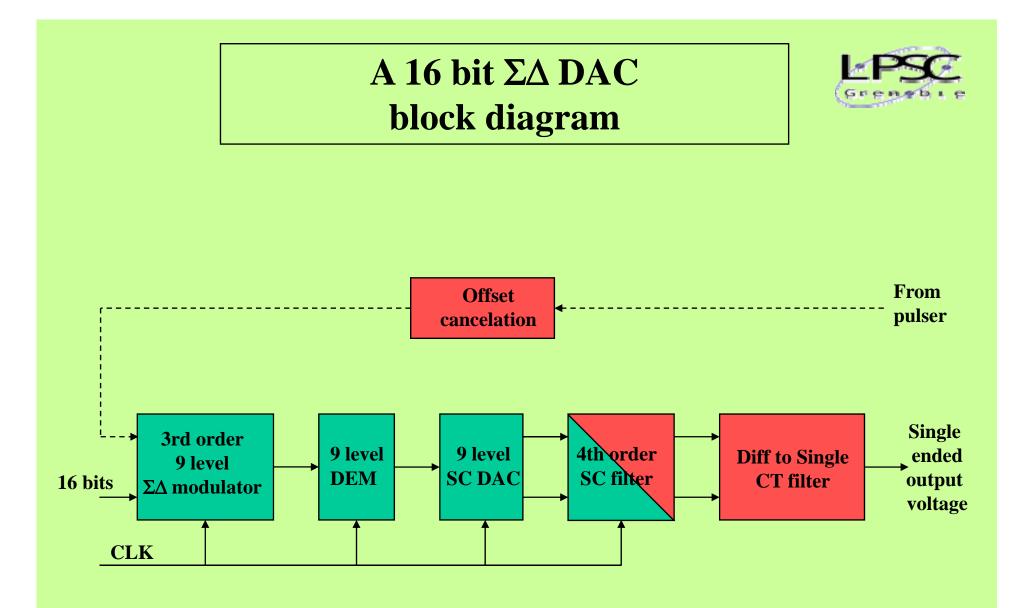

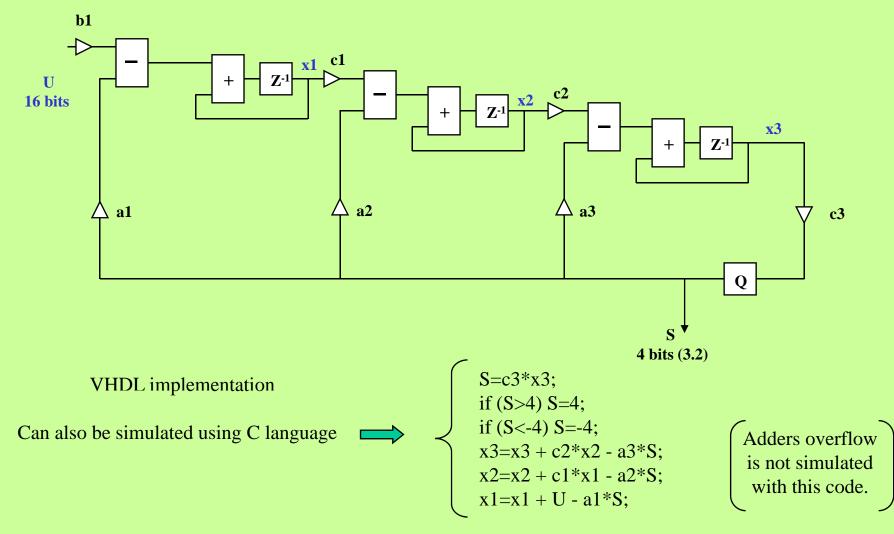

## A 16 bit ΣΔ DAC 3<sup>rd</sup> order, 9 level modulator (1)

A 96 dB SNR is necessary to achieve a 16 bit resolution.

A 3<sup>rd</sup> order, 9 level (3.2 bit) modulator leads to a SNR :

168dB for OSR=256 147dB for OSR=128 126dB for OSR=64

=> related to the SC filter design (settling time).

Multi-bit : SC filtering and OPA constraints are relaxed quantization noise is reduced, a DEM is necessary to reduce the DNL effect of the 9 level DAC.

The modulator was designed using the Matlab toolbox written by R. Schreier

### A 16 bit ΣΔ DAC 3<sup>rd</sup> order, 9 level modulator (2)

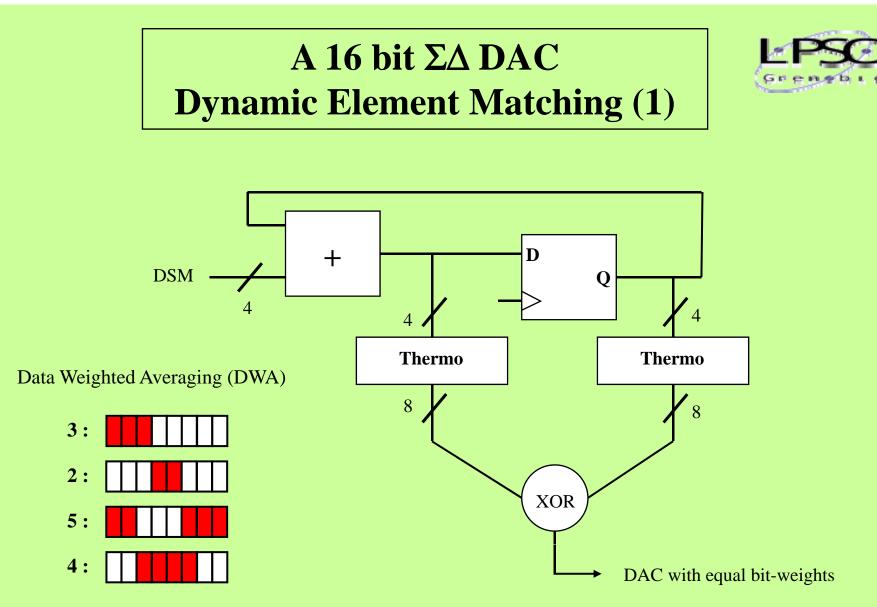

Random re-mapping turns elements mismatch into white noise.

DWA re-mapping shapes DAC errors noise.

### A 16 bit $\Sigma \Delta$ DAC **Dynamic Element Matching (2)**

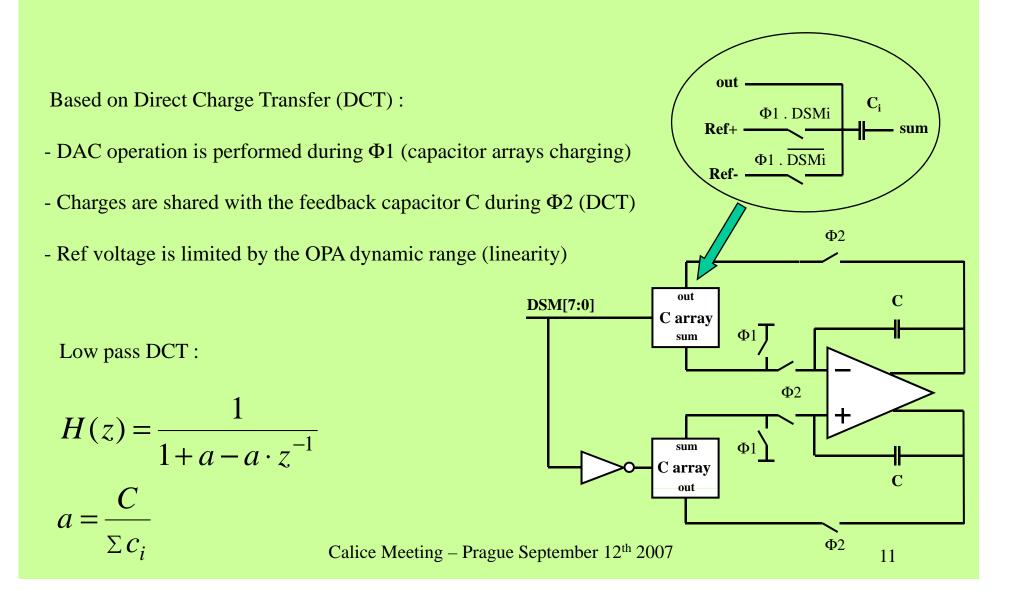

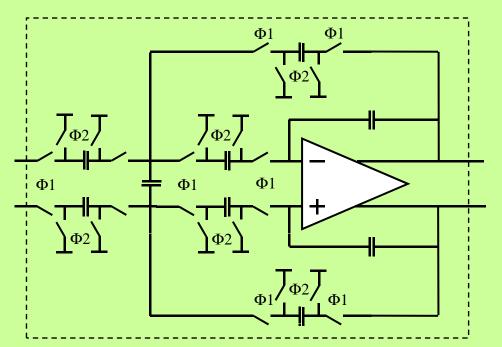

# A 16 bit $\Sigma\Delta$ DAC SC DAC

### A 16 bit ΣΔ DAC SC Filter

4th order, SC direct implementation of a MFB Butterworth Filter (Fc = 2kHz)

- Two 2<sup>nd</sup> order filter cascaded

- Two differential OPA

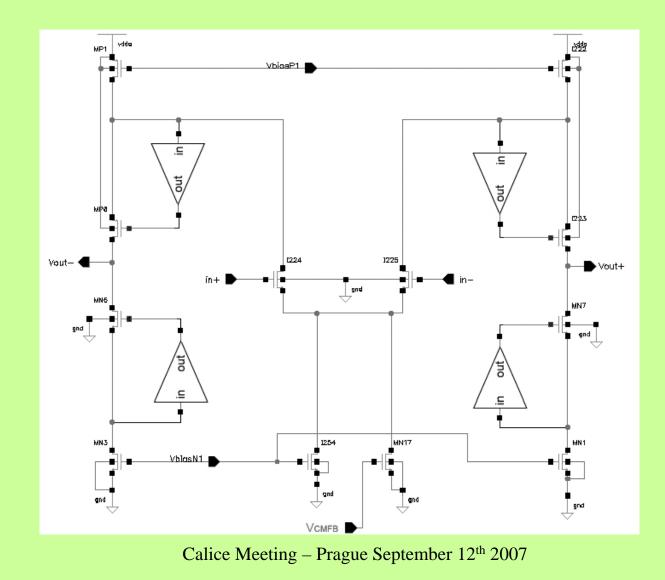

### A 16 bit $\Sigma \Delta$ DAC Differential OPA (1)

The OPA used in the SC DAC and in the SC Filter was designed (D. Dzahini) to be implemented in 12 bit, 25MHz ADCs.

The main features of this OPA are :

- Open loop gain : 100dB

- Gain-band product : 130MHz

- Dynamic range : 1.6V

- Power consumption : 6mW (3 instances required => 18mW)

Simulations have to be carried out to reduce the power consumption.

### A 16 bit ΣΔ DAC Differential OPA (2)

14

### A 16 bit ΣΔ DAC Remaining tasks

Simulations have to be carried out to complete the SC filter design : filter topology & response

OPA power consumption

The output stage has to be designed : differential to single ended converter (if implemented in the 1st proto) CT filter (if implemented in the 1st proto) output buffer (s)

- Pulser & Offset cancellation : ?

Pulser specification and design (who ?) The modulator has an offset cancellation capability, its control depends on the pulser design.

A first prototype will be submitted to the January 2008 run