# **CALICE DAQ Developments**

# DAQ overview DIF functionality and implementation EUDET Prototype development path

Imperial College London

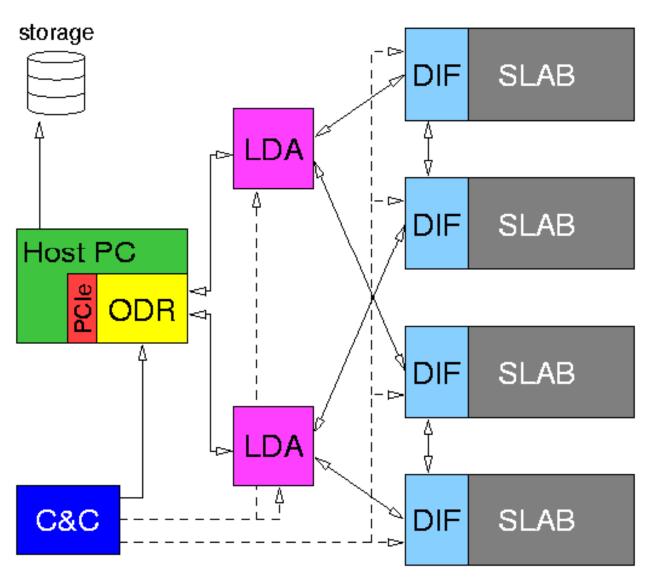

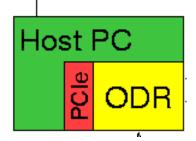

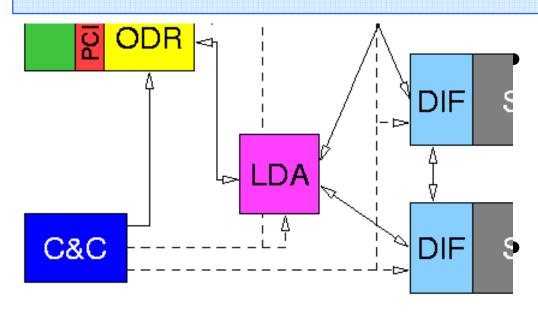

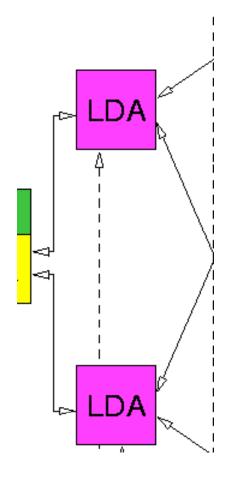

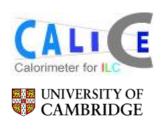

#### **DAQ** architecture

- Slab hosts VFE chips

- DIF connected to Slab

- LDA servicing DIFs

- LDAs read out by ODR

- PC hosts ODR, through PClexpress

- C&C routes clock, controls

ODR is a commercial FPGA board with PCIe interface

(Virtex4-FX100, PCIe 8x, etc.)

- Custom firm- and software

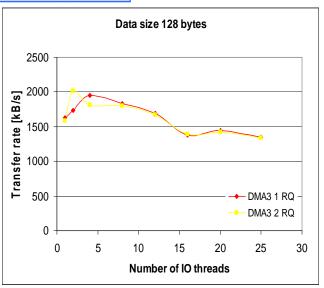

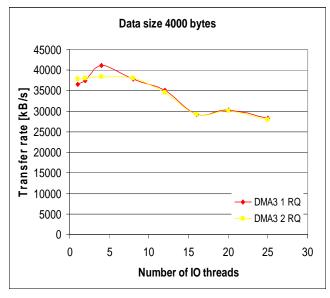

- DMA driver pulls data off the onboard RAM, writes to disk

- Performance studies& optimisation

#### **Clock & Controls Distribution**

C&C unit provides machine clock and fast signals to ODR, LDA (and DIF?)

Clock jitter requirement seems not outrageous (at the moment)

- Fast Controls: encoded through the LDA-DIF link

- Low-latency fast signals: distributed 'directly'

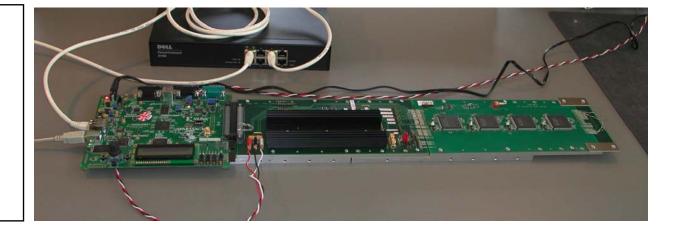

#### LDA and link to ODR

- Enterpoint Xilinx Spartan3 based dev. board

- RAM & lots of I/O (including PCI)

- 1<sup>st</sup> Prototype is again a commercial FPGA board with custom firmware and hardware add-ons:

- Gbit ethernet and Glink Rx/Tx for ODR link -probably optical

- Many links towards DIFs

#### **LDA-DIF link**

#### LDA-DIF link:

- Serial link running at multiple of machine clock

- 50Mbps (raw) bandwidth minimum

- robust encoding (8B/10B or alike)

- anticipating 8...16 DIFs on an LDA, bandwidth permitting

- LDAs serve even/odd DIFs for redundancy

|                           | Gnd            | 2        | 3        | Clk+          | Pair1 (STP) |

|---------------------------|----------------|----------|----------|---------------|-------------|

| Pair2 (STP)               | DL2D+          | 4        | 5        | Clk-<br>Gnd   |             |

|                           | Gnd            | 8        | 7        | DD2L+         | Pair3 (STP) |

| Pair4 (STP)               | SpD2L+         | 10       | 11       | DD2L-<br>Gnd  |             |

|                           | SpD2L-<br>Pow2 | 12<br>14 | 13       | Pow1          |             |

|                           | SpL2D-         | 16       | 15<br>17 | SpL2D+<br>Gnd | Pair5 (UTP) |

|                           | Pow3           | 18       | 19       | Pow4          |             |

| Possible Pinout for HDMI  |                |          |          |               |             |

| (Based on SAMTEC HPDPI    |                |          |          |               |             |

| cable signal designation) |                |          |          |               |             |

clock

data

control

spare data

spare control

#### LDA-DIF link physical form factor:

- Differential signals on shielded twisted pairs

- Few single-ended control lines

- HDMI connectors and cabling: high quality, commercially available

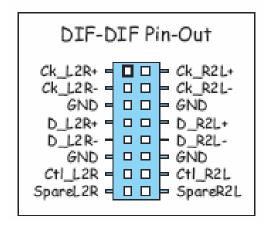

#### **DIF-DIF link**

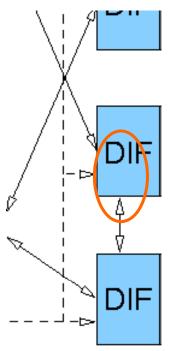

- Redundancy against loss of LDA link

- Provides differential signals:

- Clock in both directions

- Data and Control connections

- Two spares: one each direction

- Plus two single-ended control lines

- Single LDA-DIF link bandwidth sufficiently large for data of two DIFs

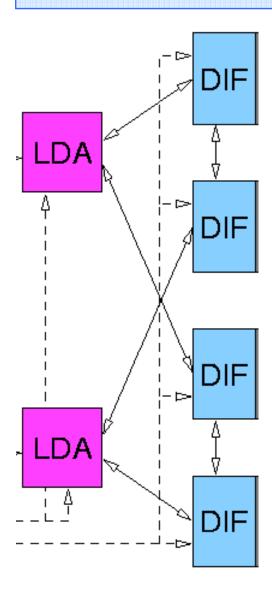

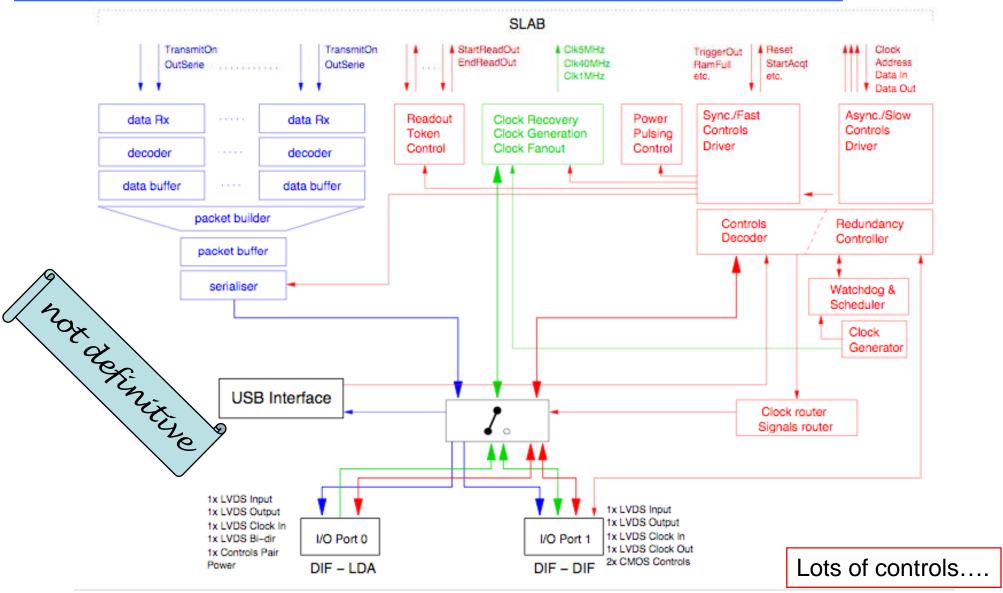

# **Draft DIF block diagram**

## **DIF Functionality**

- Receive, regenerate and distribute clocks

- Receive, buffer, package and send data from VFE to LDA

- Receive and decode incoming commands and issue corresponding signals

- Control the DIF-DIF redundancy connection

- Receive, decode and distribute slow control commands

- Control power pulsing and provide watchdog functionality

- Provide an USB interface for stand-alone running and debugging

- ....on top of that: all the things we did not think of so far

# **DIF** implementation

- The Slab is an integral part of the detector

- The LDA and ODR are transparent wrt detector type

- The DIF and its interface to the slab is detector-specific

- Large parts of the DIF firmware can/should/must be generalised

- DIF hardware should support firmware to profit from common developments

- DIF working group to address common problems and share knowledge, experience, and VHDL code

## Opportunity to memorise the acronyms:

SLAB

C&C

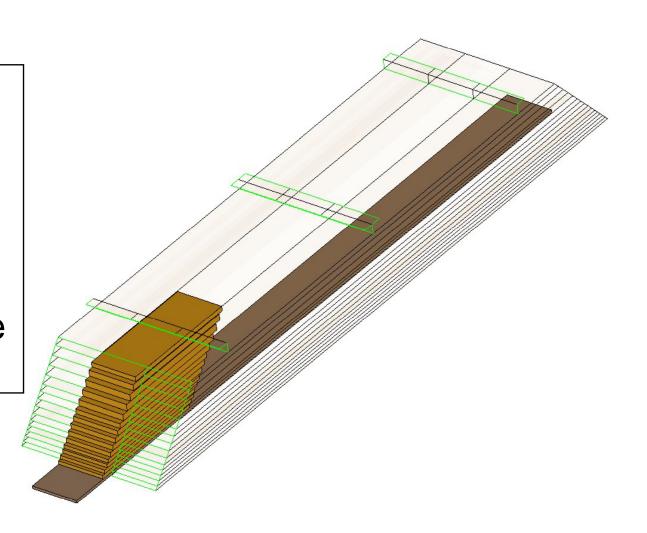

#### The EUDET prototype

UNIVERSITY OF CAMBRIDGE

- Full stack: 15 slabs, instrumented on both sides

- As close to CALICE technology as reasonably possible

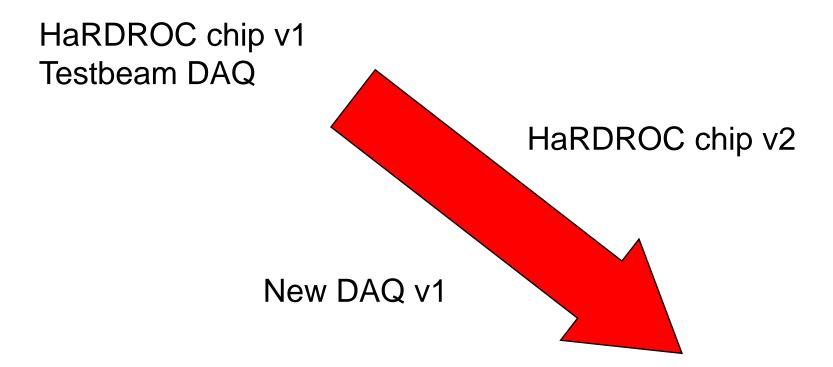

# **Prototype development**

NOW 2008 2009

EUDET proto: detector + DAQ

# Technology prototype for physics results

EUDET module is quite a large and complex object. Keep future production in mind:

- large objects are assemblies of smaller objects

- develop testable objects

Many technology options require even more R&D:

- power consumption

- data rate: speed vs. power

- noise

- etc.

#### **R&D** for the EUDET prototype

- Proto-slab:

- FPGA for VFEs

- provisional 'DIF'for ECAL

- Tests of signal distribution along long PCB lines: signal deterioration, termination options, speed, etc.

- Identification of possible issues with many (pseudo)VFE chips on long transmission paths

- Familiarise with VFE readout architecture

Much more to come.....