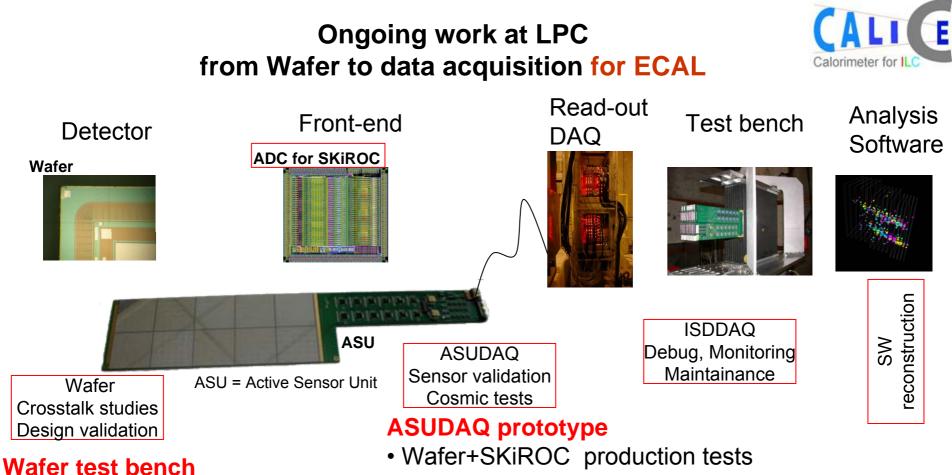

# ASU and standalone test setup for ECAL MAIA BEE project

# Overview DAQ dedicated Sensor test In situ debug and maintenance DAQ on beam

#### LPC LAL LLR

# MAIA BEE

- M aintenance

- A pparatus

- I ncluding (data)

- A cquisition (on)

- B eam (for)

- E UDET

- E CAL

# {ASUDAQ, ISDDAQ} = MAIA BEE

#### ASUDAQ = ASU DAQ

ISDDAQ = In Situ Debug DAQ (of one SLAB)

CALICE – 12/07/07 – Rémi CORNAT (LPC)

# Square event studies

#### **ISDDAQ**

SLAB monitoring

### Towards EUDET,

Validation & Test of the whole chain

- R&D test tools for sensor and electronics

- Validation, debugging and maintenance on beam

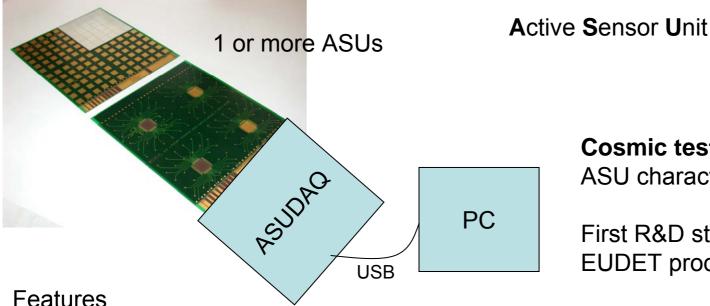

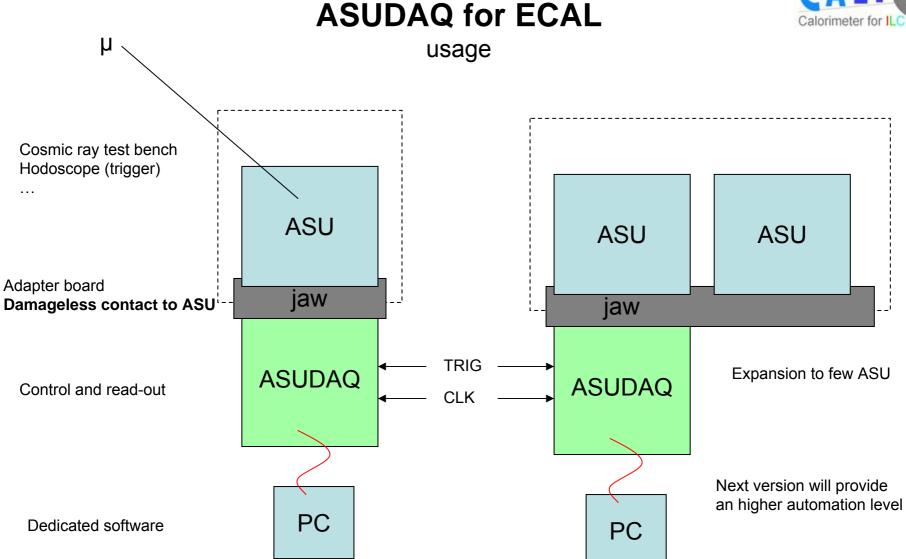

# ASUDAQ for ECAL

# R&D on ASU, Cosmic tests of ASU, Wafer+SKiROC production tests

## Cosmic test bench for ASU characterization.

First R&D step towards EUDET production tests

- full slow control including internal probing system control

- access to analog test points (embedded ADC)

- read out of 4 SKiROC through USB & PC

- cosmic bench environment support (triggers)

- mechanical jaw providing damageless contacts to ASU

A board is being designed

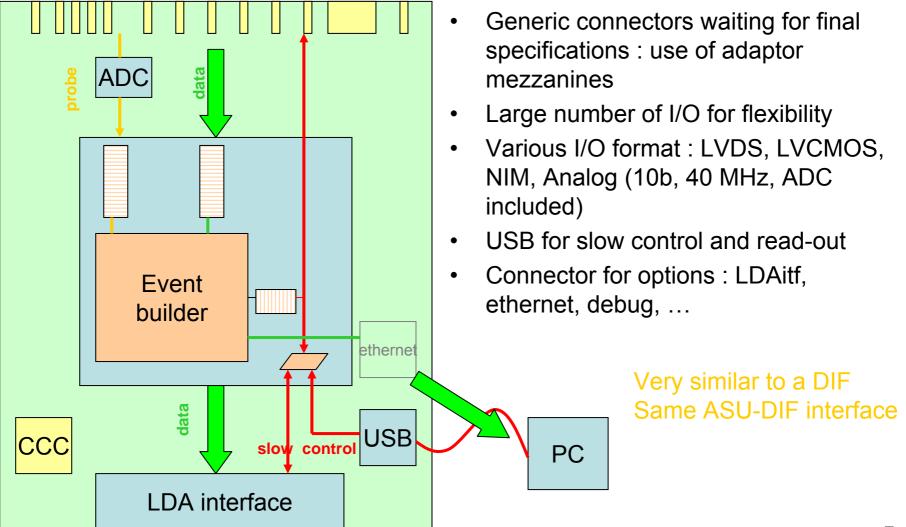

# ASUDAQ for ECAL

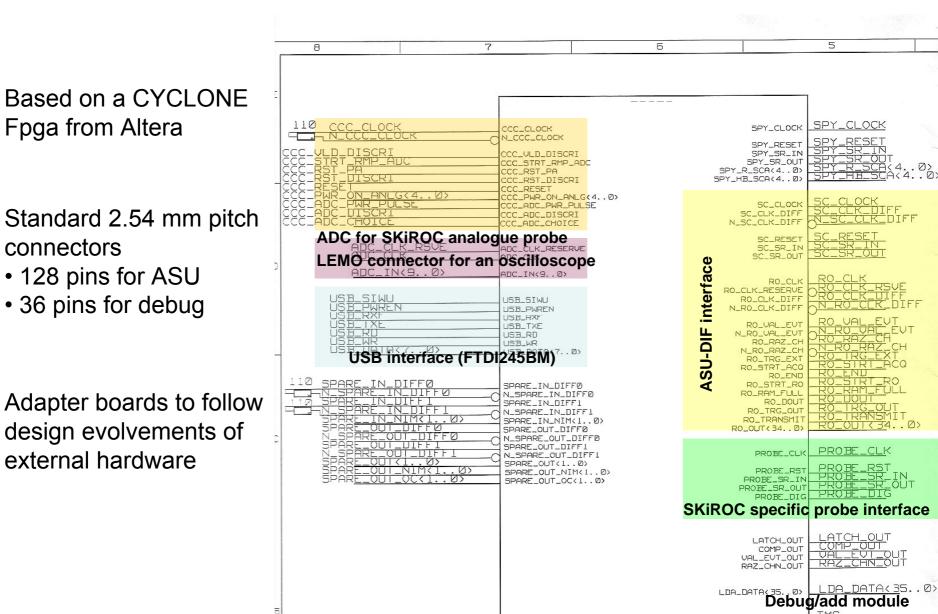

# first prototype schematics are ready

CALICE – 12/07/07 – Rémi CORNAT (LPC)

# **ASUDAQ for ECAL**

First prototype compatible with today and future SKiROC

| ASU/SLAB connector I/O |                          | LPC 22/06/07 |     |           |

|------------------------|--------------------------|--------------|-----|-----------|

| CAT                    | NAME                     |              |     |           |

| <br>HV                 |                          |              |     |           |

|                        |                          |              |     |           |

| <br>POWER              | GND<br>3.3V              |              | 1   |           |

|                        | 0.07                     |              |     |           |

| <br>BIAS               |                          |              | 0   |           |

|                        |                          |              |     |           |

| REFERENCE              |                          |              | 0   |           |

| <br>                   |                          |              |     |           |

| CCC                    | clkp 40MHz<br>clkn 40MHz | 1 LVDS       | 0   |           |

|                        | Reset                    | 1 00         | oc  |           |

|                        | power_on_xxxx            | 5 LVTTL      | 0   | new 22/06 |

|                        | testin                   | analogue     | ŏ   | new 22/06 |

|                        | lesun                    | analogue     | 0   | new 22/00 |

| <br>SC                 | clk_sc                   | 1 LVTTL      | 0   |           |

|                        | rstb_sc                  | 1 LVTTL      | 0   |           |

|                        | sroutscbuf               | 1 LVTTL      | 1   |           |

|                        | srin_sc                  | 1 LVTTL      | 0   |           |

| <br>PROBE              | analogue_probe           | analogue     | Ain |           |

|                        | digital_probe            | 1 LVTTL      | 1   |           |

|                        | · _                      |              |     |           |

| <br>READOUT            | clkp_5MHz / 1 MHz        | 1 LVDS       | 0   |           |

| READOUT                | clkn_5MHz / 1 MHz        | 12000        | 0   |           |

|                        | StartAcq                 | 1 LVTTL      | 0   |           |

|                        | ValEvtp                  | 1 LVDS       | õ   |           |

|                        | ValEvtn                  | . 2. 2. 2.   | Ŭ   |           |

|                        | RazChnp                  | 1 LVDS       | 0   |           |

|                        | RazChnn                  |              |     |           |

|                        | StartReadOut             | 1 LVTTL      | 0   |           |

|                        | EndReadOut               | 1 LVTTL      | ī   |           |

|                        | TransmitOn               | 1 LVTTL      | i   |           |

|                        | Dout (out0)              | 1 LVTTL      | i   |           |

|                        | RamFull                  | 1 00         | oc  |           |

|                        | TriggerExt               | 1 LVTTL      | 0   |           |

|                        | TriggerOut               | 1 LVTTL      | ĩ   |           |

|                        |                          |              |     |           |

# **ASUDAQ** ASU connector

To be discussed : see my next talk

Many I/O more added to current board to follow SKiROC developments

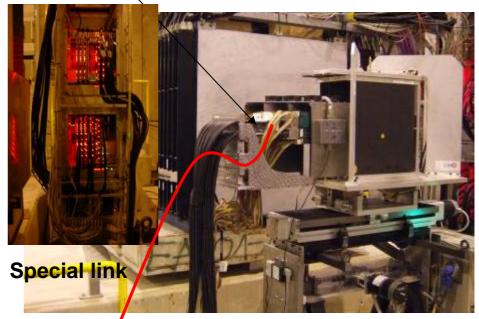

# InSituDebugDAQ

# concept

#### On beam simplified DAQ devoted to monitor and debug a few SI ABs

- chip radiation tolerance

- accurate diagnostic

- of unexpected behavior

- monitoring (internal probes)

- maintenance

Can run alone, eventually with no beam compatible with machine interface or specific trigger and timing

Standard DAQ

PC

#### **Dedicated Software** to ease

debugging

Simultaneous DAQ operations allowed

# **Needs/Replaces DIF !?**

# InSituDebugDAQ

**ISDDAQ**

PC

**SLAB**

eDIF

LDA

ODR

TRIG

ISSDAC.

Extended DIF is needed for VFE probes and mixed data flow mode (probe+DAQ) and replaces DIF when debugging

Direct connection to LDA would avoid risky cabling operations and highest flexibility

## DAQ NI PCI-7811R ?

• FPGA based, 160 I/O to PCI

buffer flush mode (continuous streaming to PC)

Or Ethernet

Dedicated software tools

ASUDAQ prototype is designed to be compatible with ISDDAQ requirements = first prototyping steps are common

# Conclusion

## ASUDAQ

- first developments on prototyping board

- ASU connector issue

## **ISDDAQ** architecture issue

- SKiROC Internal probes read-out

- Simultaneous DAQ

- Flexibility (FPGA based)

# Common "all in one" prototype is being designed

- generic interfaces

- use of additional adapter board to connect to ASU, SLAB, etc...