# High speed 12 bits Pipelined ADC proposal for the Ecal

High speed =>because only config to optimize pipeline power consumption

Full CMOS even if more difficult

Low voltage (3.3V)

High dynamique range (1.2V to 1.5V)

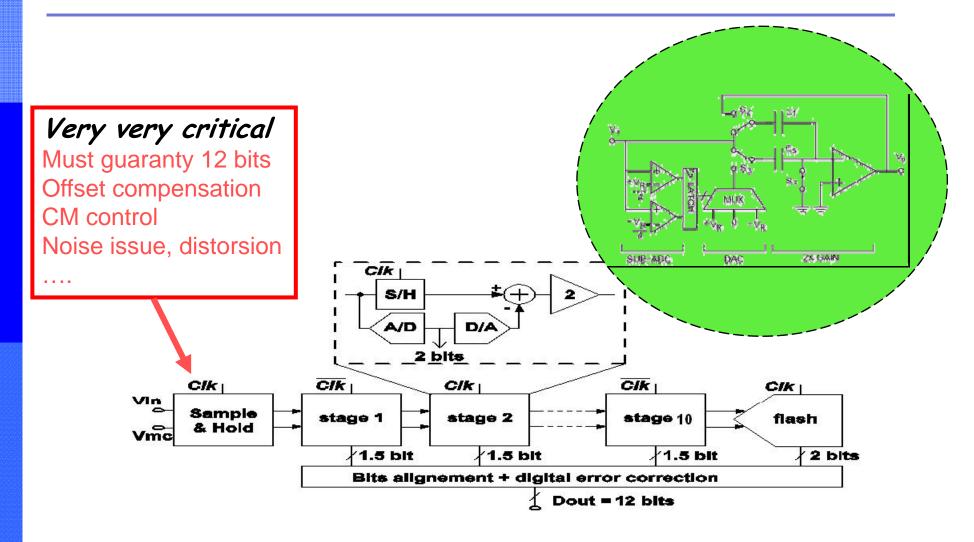

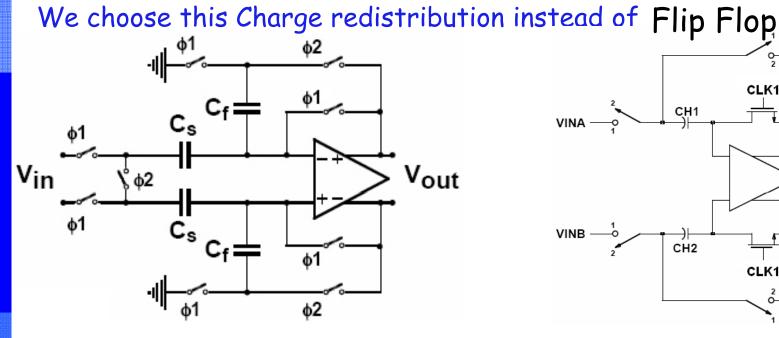

# Pipe line ADC design: the baseline

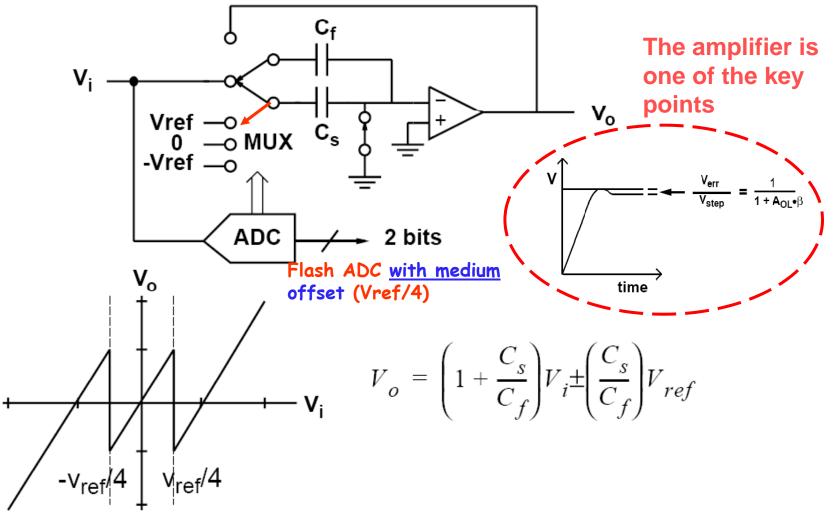

# **MDAC** Function: Multiplier & DAC

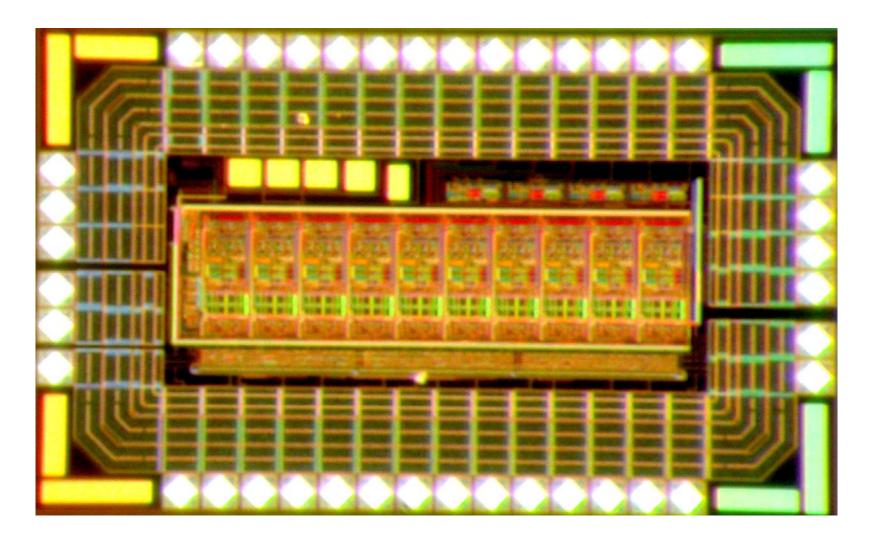

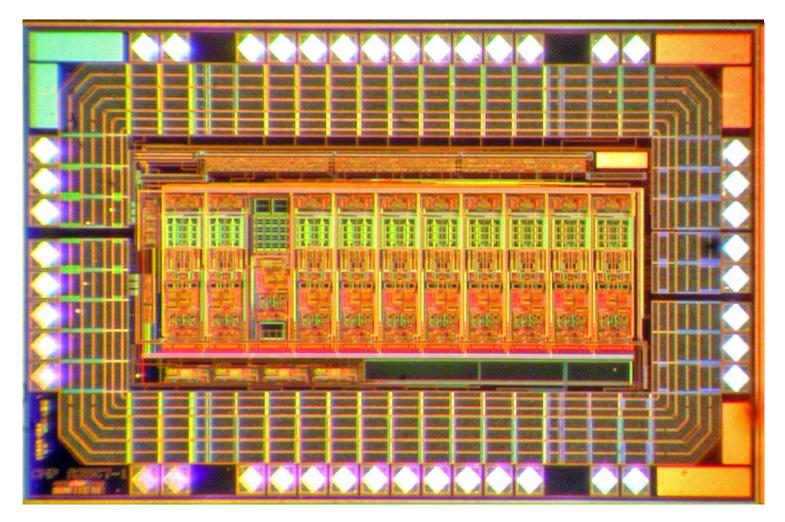

#### First ADC prototype: 10bits basic features extended to 12bits

# Testing results 1

The DC power consumption is exactly fitting with our simulations:

**27mW** for the actual ADC and 3mW for the Bias stages

□ The sampling speed is up to 15Mhz.

□ The very fast power pulsing 1µS, to a ratio better than 1/1000.

No Obvious missing code when averaging, BUT!

□ INL and DNL: depend on how you measure

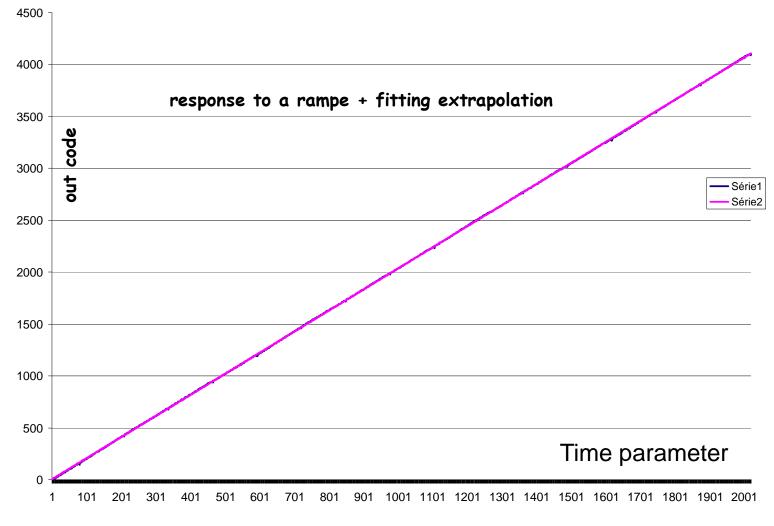

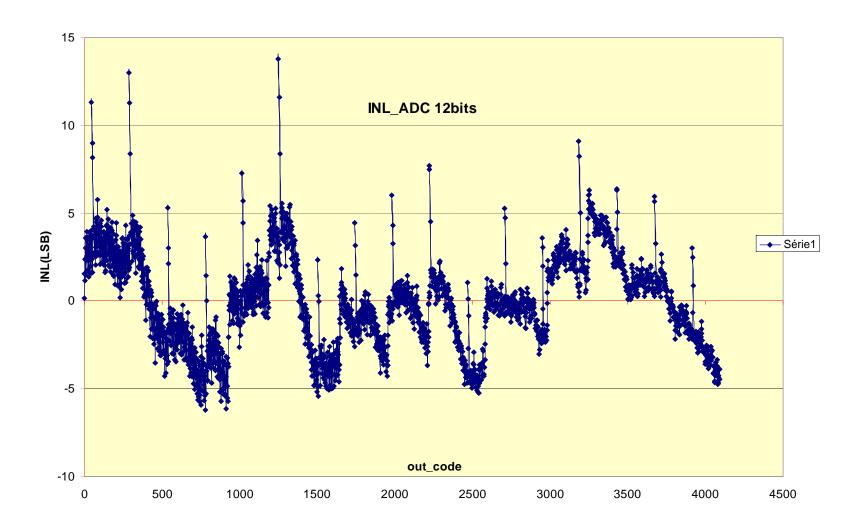

# INL results with an input ramp generated by a 12 bits DAC

D. Dzahini / LPSC Grenoble / Prague 2007

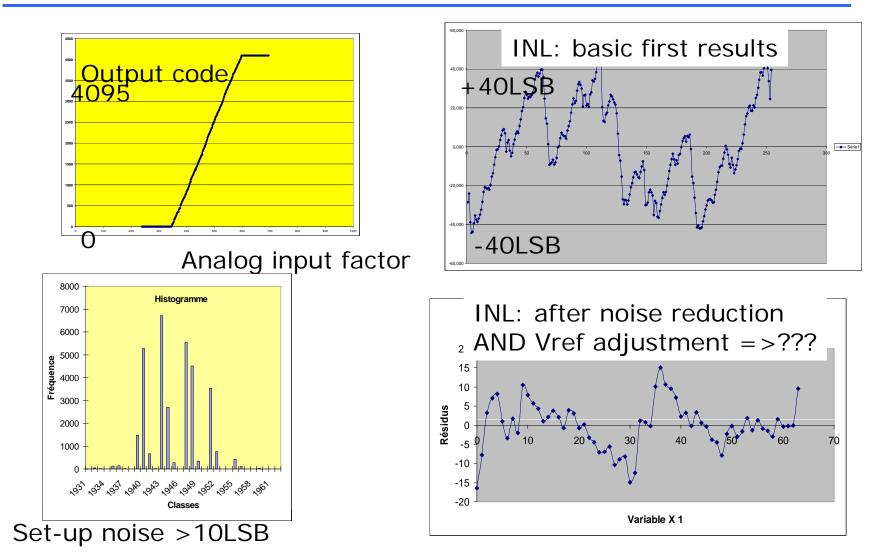

### INL first results with onboard S/H Be careful with the set-up !!!!

# INL results for input ramp and *averaging* => ENOB $\approx$ 9.5 bits ?? Is there a link?

D. Dzahini / LPSC Grenoble / Prague 2007

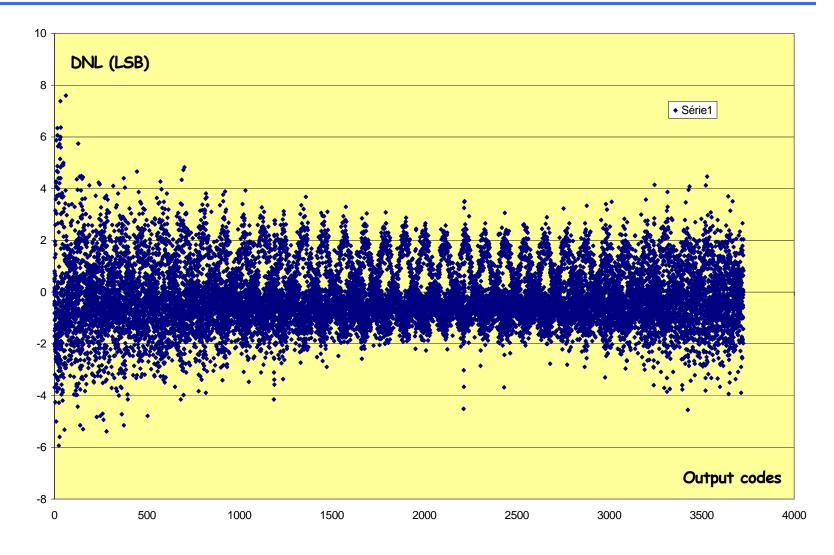

# DNL results when differentiating the averaged output code(n)-code(n+1)

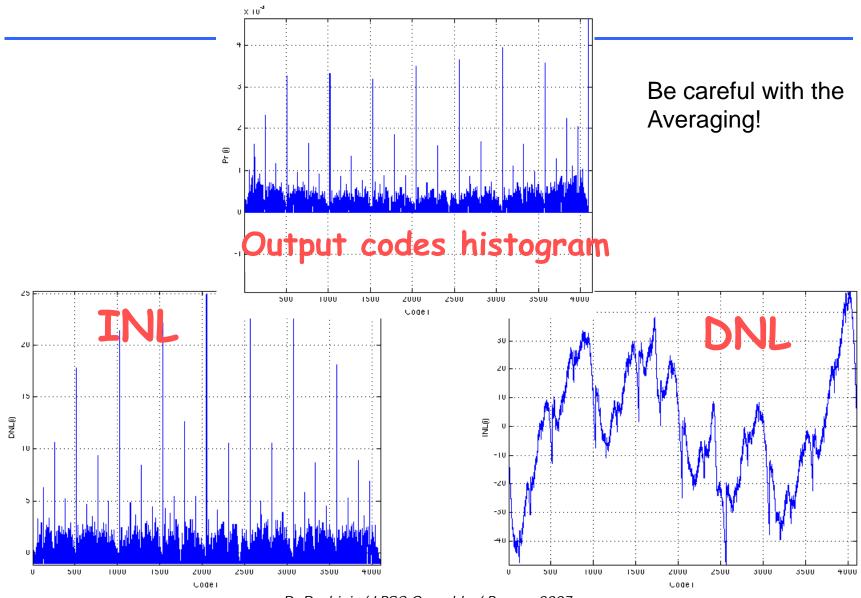

# The same output codes after analysis by a dedicated ADC testing software (IXL -D. Dallet)

D. Dzahini / LPSC Grenoble / Prague 2007

# Second version design features

Include the design of the S/Hold stage

Improving the dynamique range to 1.5V

Extend the speed beyond 30Mhz

Include an LVDS clock input

Improve the capacitors matching.

# THE Sample "Track" and Hold

#### + single ended to differential

- + less sensitive to CM error

- + Offset cancelled (differentially)

- Noise ( $\sqrt{2}$  more)

- Gain mismatch

- + Mismatch insensitive; gain=1

- + Less noise

- + Offset cancelled (differentially)

- Sensitive to CM fluctuations

- Need full differential inputs

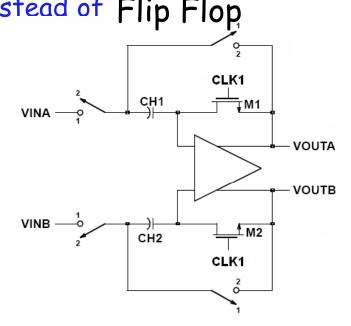

# Sample & Hold Simulations

#### Improved SH Non linearity @ 25Mhz for the 2<sup>nd</sup> version of 12 bits ADC

D. Dzahini / LPSC Grenoble / Prague 2007

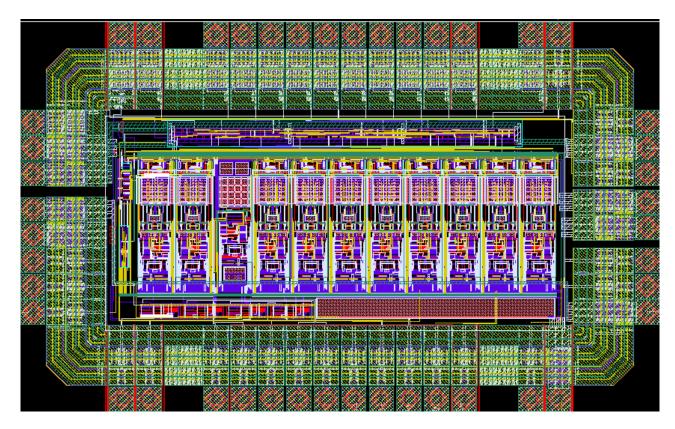

### 2<sup>nd</sup> version of <u>actual</u> 12 bits ADC Submitted in January 07

- 1) Thru 12 bits including a Sample/Hold

- 2) Speed: Beyond 30MHz

- 3) Power: 35mW with fast and efficient standby command

D. Dzahini / LPSC Grenoble / Prague 2007

#### 2<sup>nd</sup> prototype, die received by June 07

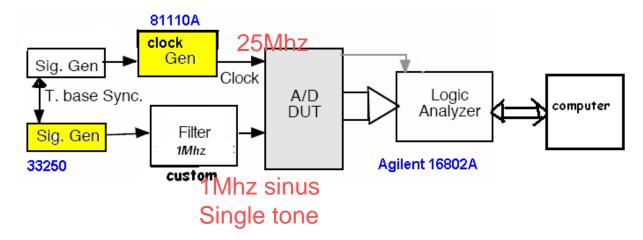

# Accurate ADC test bench

- -Be careful with the synchronization of your clock

- -Pay attention to your input signal spectrum

- We need dedicated software to make sure: the FFT windowing + analysis

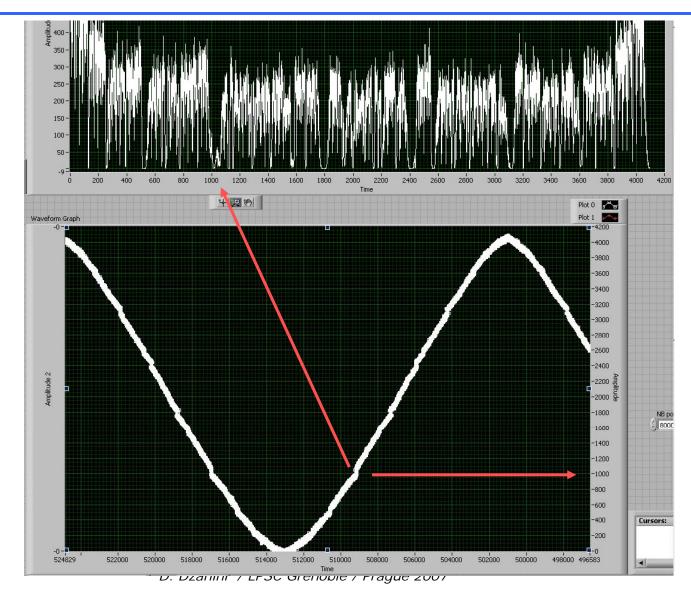

# Testing results=>missing codes

19

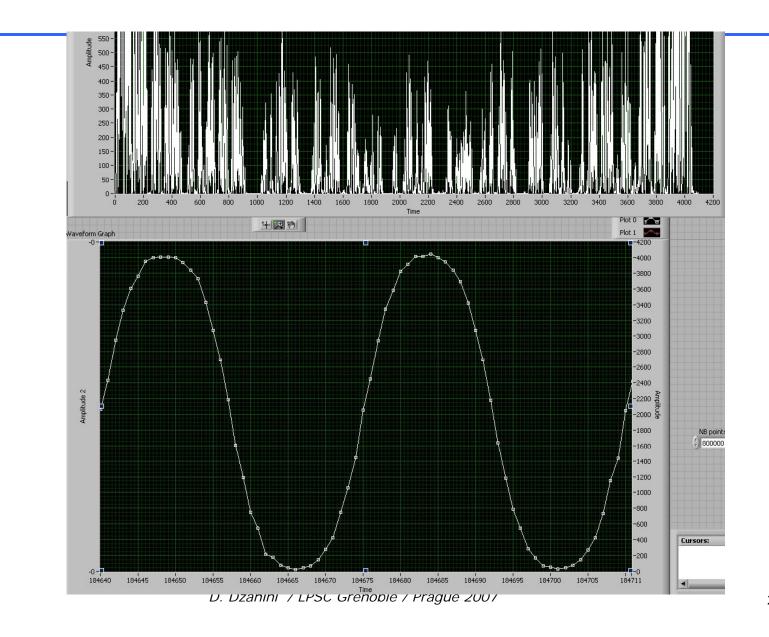

### 1Mhz sinus sampled at 35Mhz + histo

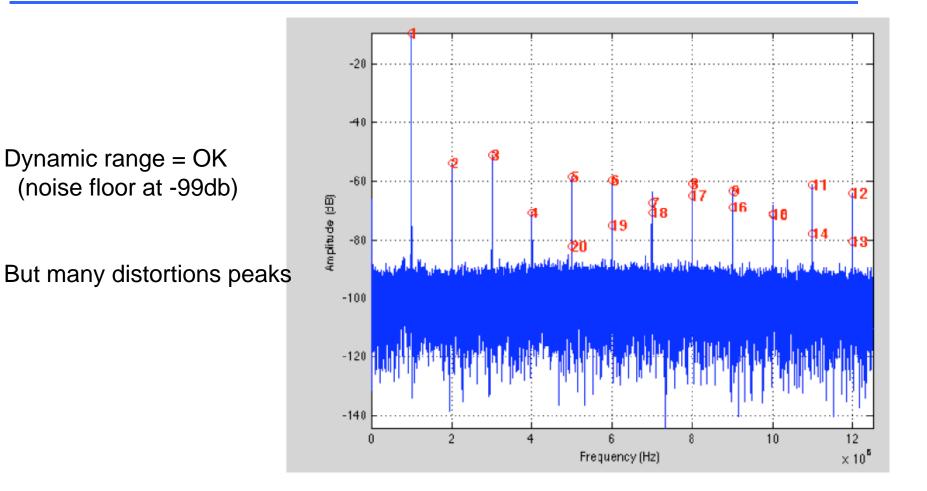

# Spectrum analysis (FFT)

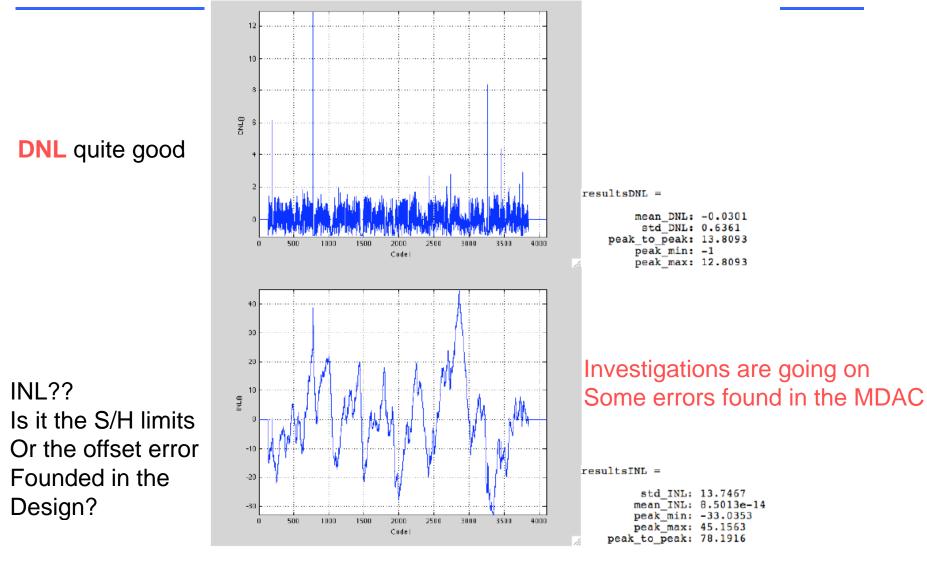

# Linearity still to be understood

#### Summary of the test second proto.

- Speed –OK up to 40Mhz

- □ DNL -> OK

- Power switching -> OK

- Power dissipation 60mW instead of 40mW and this is fixed

- INL ->NO (investigations are going on: S/H limits? Errors found in the layout)

- The third version will be received in two weeks with some improvements

#### NEXT STEPS for the "12" bits ADC design

The test is really a critical task (3 months)

Including a S/H is necessary for accurate test But its test is more critical than the ADC....

Design of a 12bits=>digital control of the gain is absolutly necessary, and we are working on it.

We found some errors in the layout which are fixed (it could have introduce 10LSB errors)