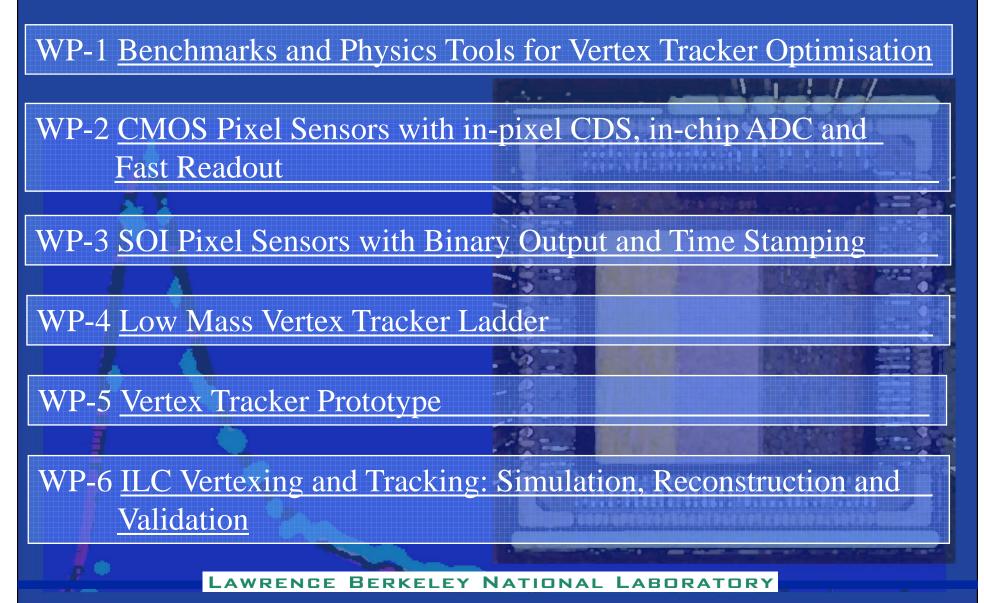

## **ILC Vertex Tracker**

#### **From Instrumentation R&D to Physics Benchmarking**

A LNBL and UC Berkeley Program in collaboration with Purdue U, INFN Padova and INFN Torino

M Battaglia UC Berkeley and LBNL

#### Collaborators

M Battaglia, J-M Bussat, D Contarato, P Denes, L Glesener, L Greiner, B Hooberman, D Shuman, L Tompkins, C Vu UC <u>Berkeley</u> and LBNL, Berkeley, CA

D Bisello, P Giubilato, D Pantano, M INFN and Dip Fisica, <u>Padova</u>, Italy

M Costa, A La Rosa INFN and Dip Fisica, <u>Torino</u>, Italy

G Bolla, D Bortoletto, I Childres <u>Purdue</u> U, West Lafayette, IN

#### **Monolithic Pixel Sensor Development**

#### Analog Pixel Architecture

- Charge Interpolation  $[\sigma \sim a/(S/N)]$

- In-pixel CDS & On-chip Digitisation

- Fast Readout

AMS 0.35μm-OPTO LDRD-1 (2005): 10, 20, 40μm pixels LDRD-2 (2006): 20μm pixels, in-pixel CDS 3T and SB pixels

LDRD-3 (2007): 20µm pixels, n-pixel CDS on-chip 5-bit ADCs

#### <u>Binary Pixel Architecture</u>

- Small Pixels  $[\sigma = \text{pitch}/\sqrt{12}]$

- In-pixel Discr. & Time Stamping

- In-situ Charge Storage

OKI 0.15μm FD-SOI LDRD-SOI-1 (2007): 10μm pixels, analog & binary pixels OKI 0.20μm FD-SOI LDRD-SOI-2 (2008): 10μm pixels, analog & binary pixels (in-pixel time stamp)

#### **WP-2**

Monolithic CMOS Pixel Sensors with in-pixel CDS, in-chip ADCs, Data Sparsification and Fast Readout

## **LDRD-1** Chip

#### LDRD-1 Chip:

First LBNL test structure, simple 3T pixels, analog output, 3 matrices with  $10 \times 10 \ \mu m^2$ ,  $20 \times 20 \ \mu m^2$ and  $40 \times 40 \ \mu m^2$  pixels;

#### AMS 0.35 OPTO process

5.0

5.1

**40**

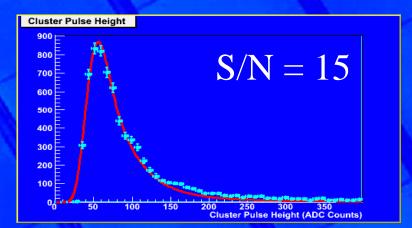

#### m.i.p. response with 1.5 GeV e<sup>-</sup> beam at ALS

#### **Resolution Study** 850 nm Laser Scan, 40×40 μm<sup>2</sup> Pixels ADC Column/ADC Guster 9.0 2.0 80 Guster 1 11111111111111 (focused laser spot) 40 µm ADC counts 10 Pi xel Pitch Laser Sim Scan (µm) 0.5 0.4 10 2.0 1.5 0.3E 0.2 20 3.3 3.2

20 40 60 80 100 120 140

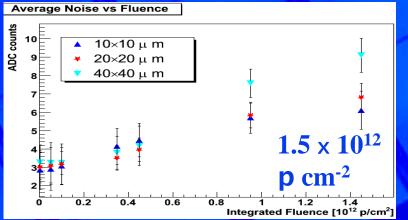

#### Radiation Hardness Test with 30 MeV p and n at 88" Cyclotron

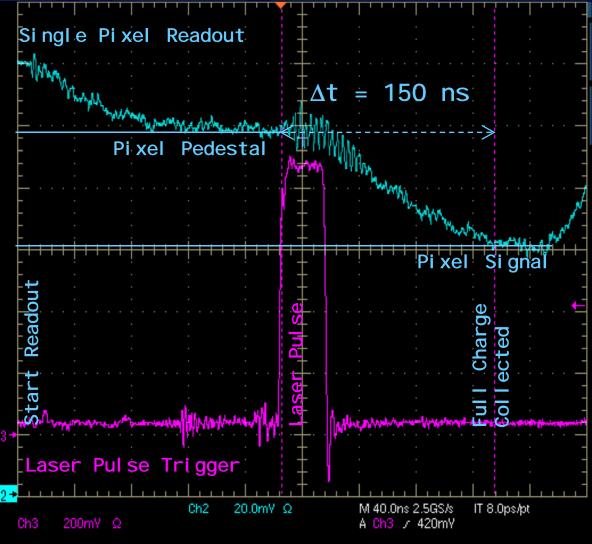

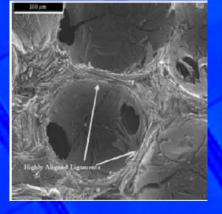

Charge carriers collected by diffusion in almost field-free epitaxial layer;

<u>First measurement</u> of charge collection time in AMS 0.35-OPTO process;

1 ns 1060 nm Laser pulse collimated on  $20 \times 20 \mu m$  pixel, charge = 1 m.i.p.

Charge collection time  $\Delta t \sim 150 \text{ ns}$

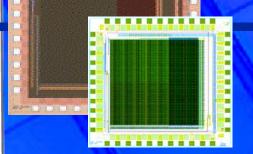

## LDRD-2 Chip

#### LDRD-2 Chip:

Second generation chip features more complex pixel architecture (20 transistors) with in-pixel CDS, power cycling, different bias options and diode sizes, two parallel outputs of 48 x 96 pixels.

Size: 1.5x1.5 mm<sup>2</sup> 6 matrices of 20x20 μm<sup>2</sup> pixels;

AMS 0. 35-0PT0 process, received October 2006

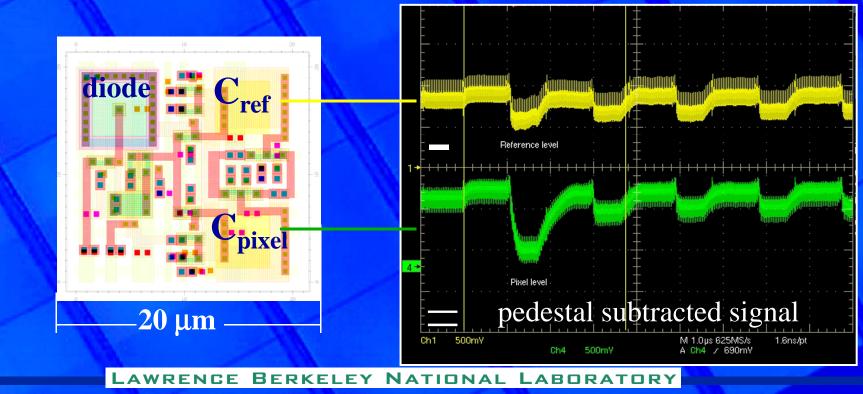

## **LDRD-2** Chip: In-Pixel CDS

Digitisation at end of pixel column limited in precision by speed and power dissipation: advantageous to subtract pedestal level in-pixel with correlated double sampling.

## **Stored reference** and **pixel level** with pulsed laser light:

BERKELEY

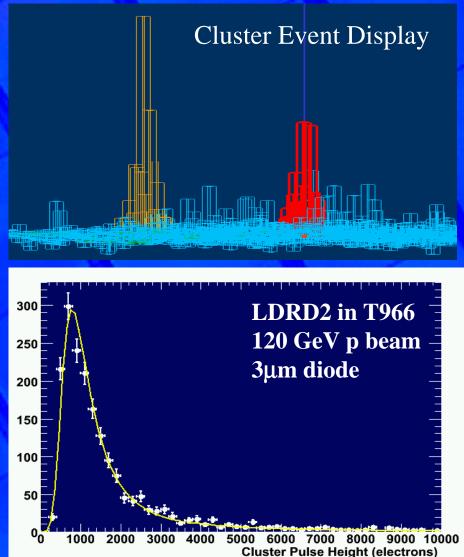

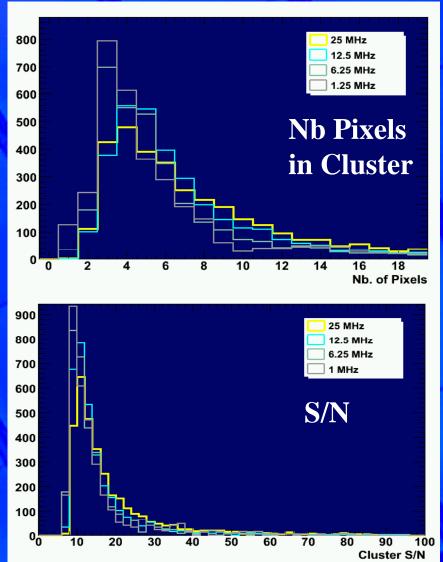

LDRD-2 tested on ALS 1.3 GeV e<sup>-</sup> and MTest 120 GeV p beams;

Operated in rolling-shutter mode, CDS from in-pixel stored ref. charge, 1.25 - 25 MHz r/o speed, noise stable up to 25 MHz and limited by r/o board:

Preliminary results @ 21°C at 1.25 MHz

> <Nb. of Pixels 4-5 in Cluster>

> > <<u>S/N></u>

~16

\*\*\*

BERKELEY LA

# Chip: 25 MHz readout

#### ALS BTS 1.35 GeV e<sup>-</sup> beam

Operate LDRD-2 at different r/o frequencies under same beam conditions;

Results show no appreciable degradation of response up to maximum tested frequency of 25 MHz (integration time 184 µs)

BERKELEY LAP

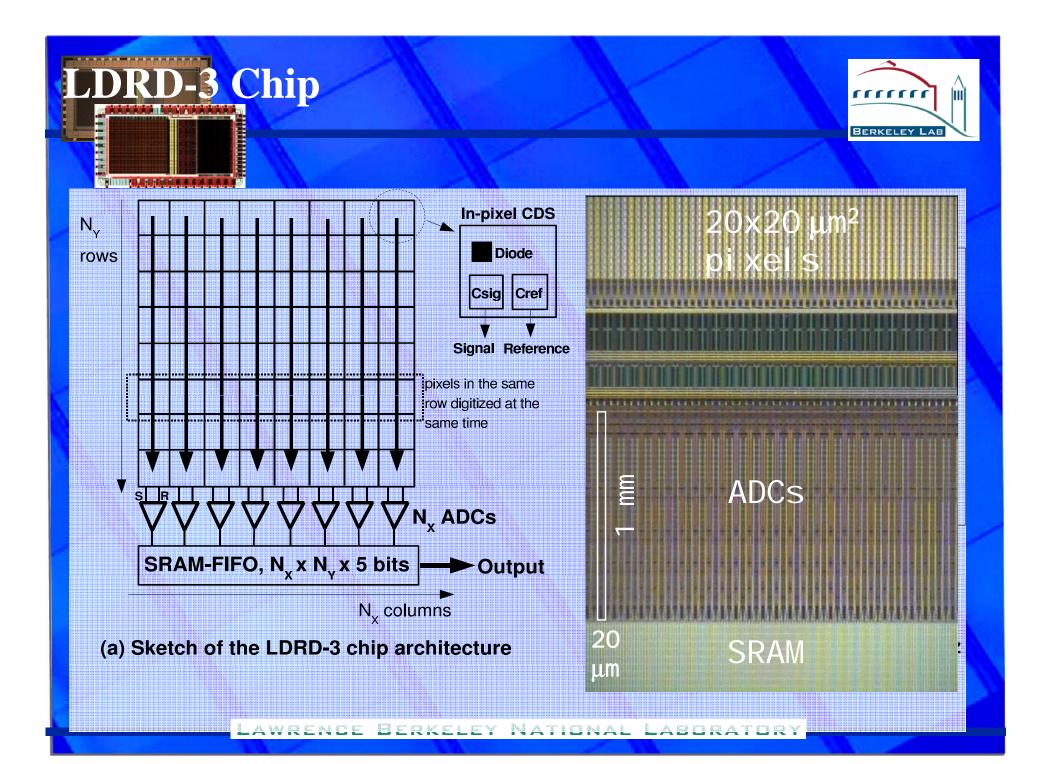

## LDRD-3 Chip

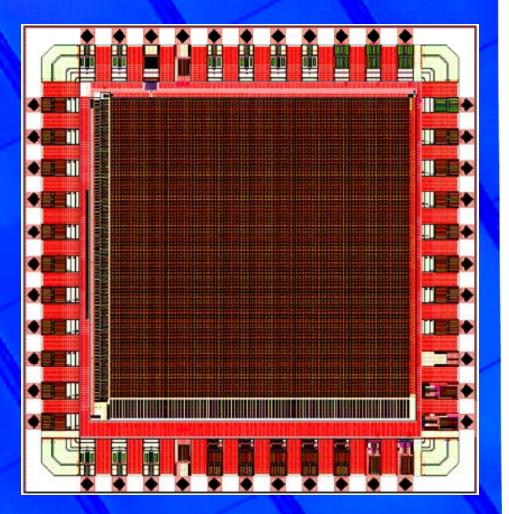

#### LDRD-3 Chip:

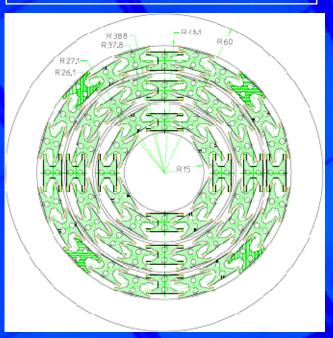

Third generation chip features same pixel cell as LDRD-2 with in-pixel CDS and 5-bit successive approximation fully differential ADCs at end of columns. CDS subtraction performed at digitisation level;

Size:  $4.8 \times 2.4 \text{ mm}^2$ matrix of 96×96 of  $20 \times 20 \ \mu\text{m}^2$  pixels;

AMS 0. 35-0PT0 process, received October 2007

AWRENCE BERKELEY NATIONAL LABORATORY

88

100

LDRD-2-RH Chip

Radiation-hard test version of LDRD-2 chip;

Enclosed transistors, various diode designs (standard, extended thin oxide, same with poly guard ring, ...)

Chip submitted in October 2007 in AMS 0.35 OPTO process, to be characterised and irradiated with 200 keV e<sup>-</sup> (NCEM), 30 MeV p and 14 MeV n (88" cyclotron)

## WP-3 SOI Monolithic Pixel Sensor with Binary Output and Time Stamping

## **LDRD-SOI** Chip

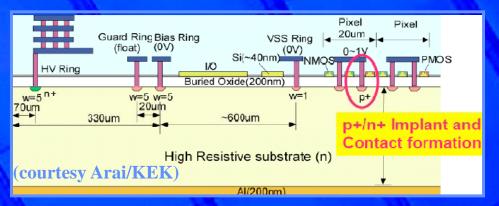

SOI process offers appealing opportunity for monolithic pixel sensors, removing limitations from commercial CMOS;

SOI appealing to industry for low-power devices, ultra-low power stand-by;

**Specialized 0.15µm FD SOI process** with high resistivity bulk and vias offered through KEK within R&D collaborative effort;

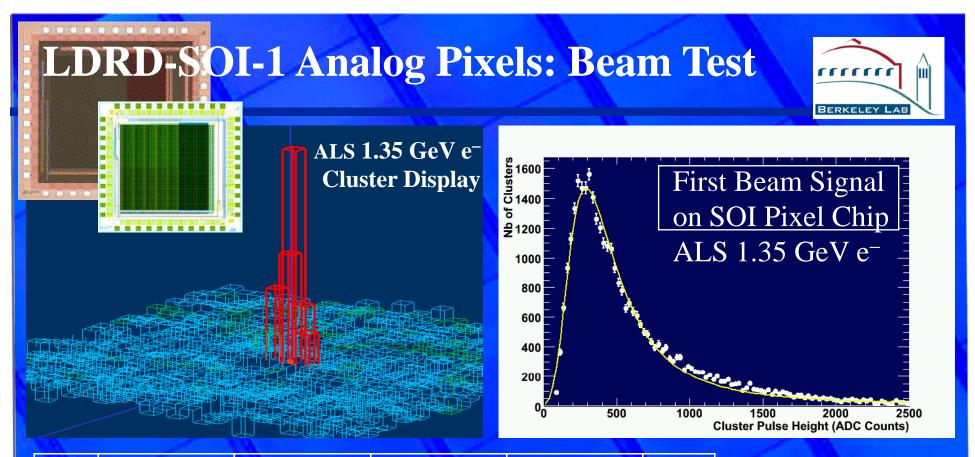

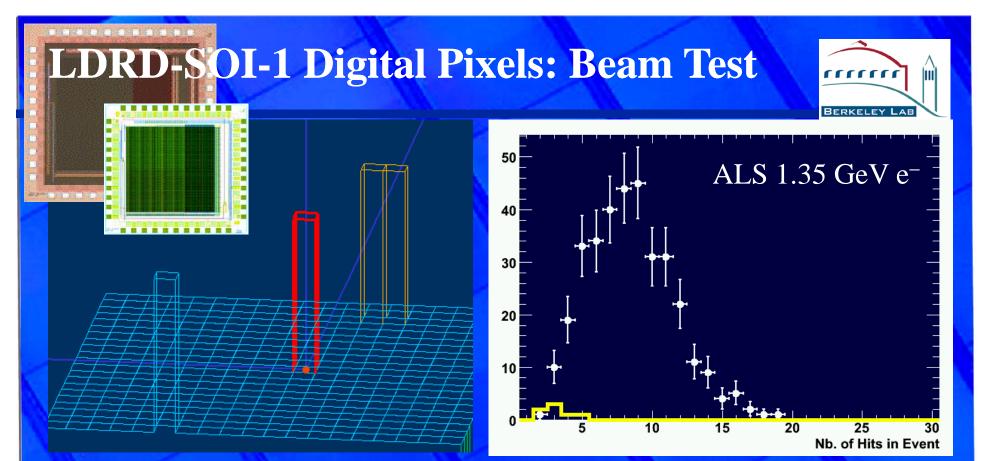

Chip with  $10 \times 10 \ \mu m^2$  pixels, both **3T analog** and **digital** architectures;

## **LDRD-SOI-1:Tests and Irradiation**

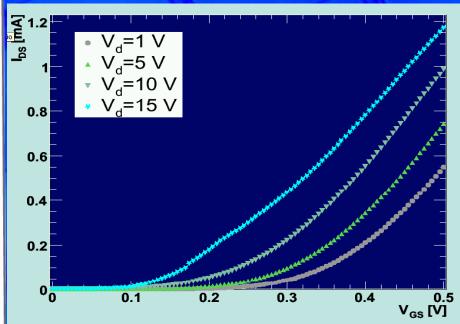

Significant backgating effect observed in single transistor test, expect analog chip section functional for  $V_d < 20$  V

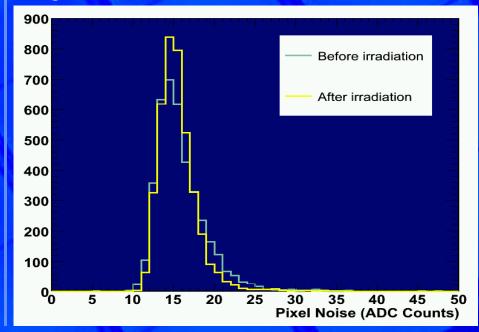

First irradiation performed with 30 MeV protons (2.5 x 10<sup>12</sup> p/cm<sup>2</sup>) show evidence of charge build-up in BOX;

Exposure to 1-20 MeV neutrons (10<sup>11</sup> n/cm<sup>2</sup>) shows no appreciable degradation of noise:

| V <sub>d</sub><br>(V)                 | Clusters/Evt<br>w/ beam | Clusters/Evt<br>w/o beam | <nb pixels=""></nb> | Signal MPV<br>(ADC) | S/N  |  |  |

|---------------------------------------|-------------------------|--------------------------|---------------------|---------------------|------|--|--|

| 1                                     | 9.7                     | 0.05                     | 3.31                | 132                 | 8.9  |  |  |

| 5                                     | 14.0                    | 0.12                     | 3.39                | 242                 | 14.9 |  |  |

| 10                                    | 7.8                     | 0.20                     | 3.31                | 316                 | 15.0 |  |  |

| 15                                    | 3.9                     | 0.01                     | 2.45                | 301                 | 13.6 |  |  |

| LAWRENCE BERKELEY NATIONAL LABORATORY |                         |                          |                     |                     |      |  |  |

to appear in NIM A (2007)

| Clusters/Evt<br>w/ beam | Clusters/Evt<br>w/o beam        | <nb pixels=""></nb>             |

|-------------------------|---------------------------------|---------------------------------|

| 3.62                    | 0.04                            | 1.78                            |

| 5.81                    | 0.04                            | 1.32                            |

| 8.31                    | 0.04                            | 1.26                            |

| 1.60                    | 0.01                            | 1.14                            |

|                         | w/ beam<br>3.62<br>5.81<br>8.31 | w/ beam3.620.045.810.048.310.04 |

Digital pixel consists of 3T + comparator and latch, no internal amplification for minimum power dissipation, total 15 transistors in 10×10µm<sup>2</sup>

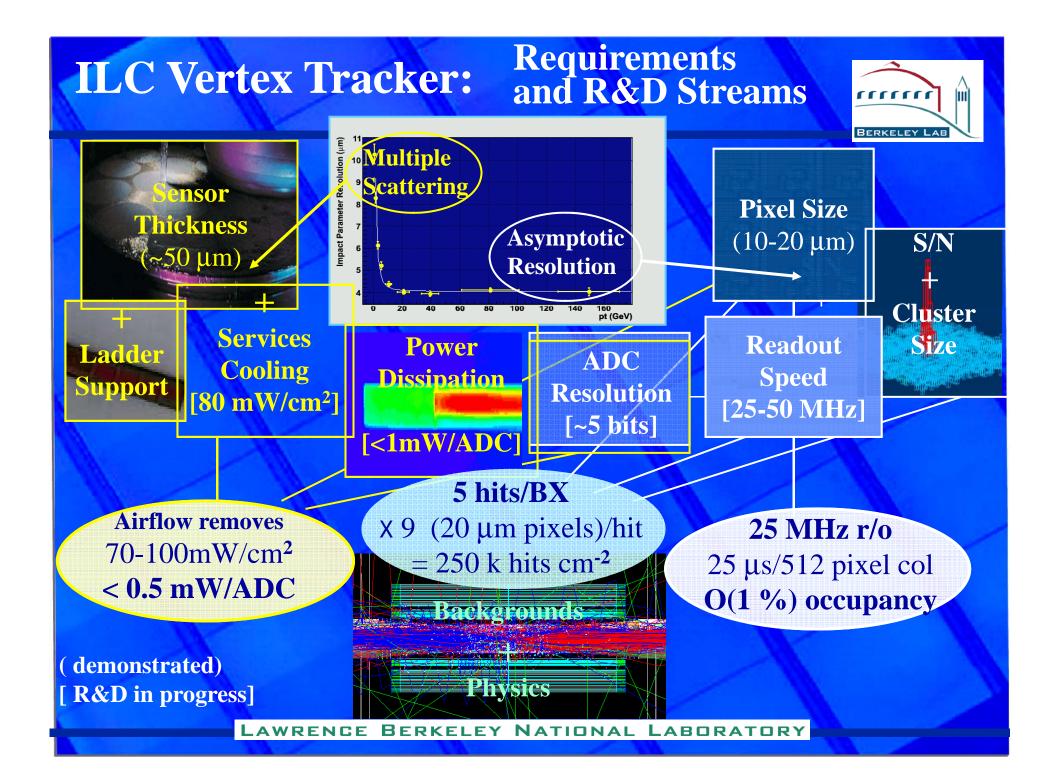

#### WP-4 Low Mass Vertex Tracker Ladder based on Thin Pixel Sensors

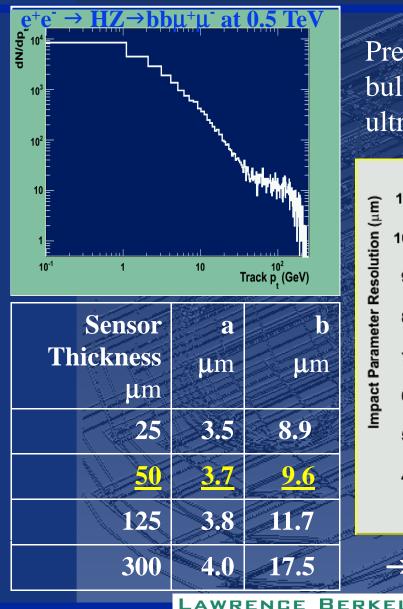

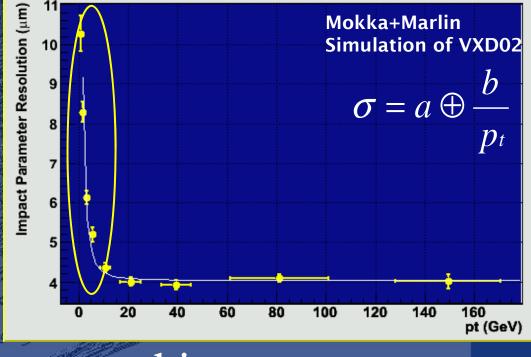

#### **Multiple Scattering and Sensor Thickness**

Preserving track extrapolation accuracy to bulk of particles at low momentum requires ultra-thin sensors and mechanical support:

$\rightarrow$  need thin monolithic pixel sensor.

LAWRENCE BERKELEY NATIONAL LABORATORY

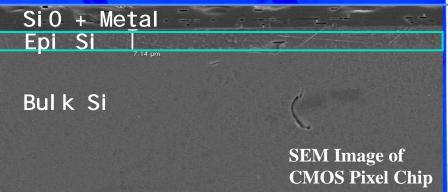

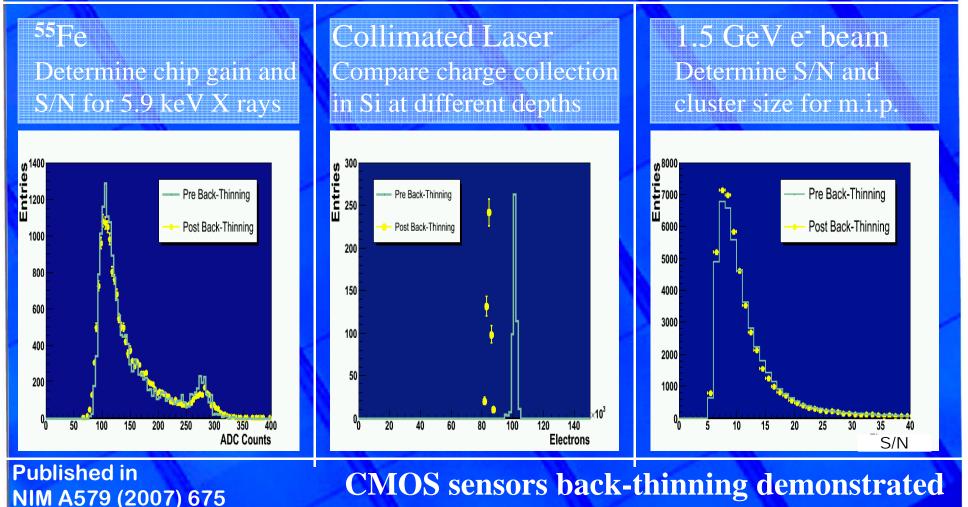

## **CMOS Sensor Back-thinning**

Thin sensitive epi-layer makes CMOS Pixel sensors in principle ideally suited for back-thinning w/o significant degradation of performance expected (especially S/N), but questions arise from earlier results;

Back-thinning of diced CMOS chips by partner Bay Area company: Aptek. Aptek uses grinding and proprietary hot wax formula for mounting die on grinding plate: Backthinning yield ~ 90 %, chip thickness measured at LBNL after processing: "50  $\mu$ m" = (50 ± 7) $\mu$ m, "40  $\mu$ m" = (41±6) $\mu$ m; three chips fully characterised:

#### 40 µm Back-thinned Sensor Tests

Study change in charge collection and signal-to-noise before and after back-thinning: Mimosa 5 sensors (IPHC Strasbourg), 1 M pixels 17 µm pitch, 1.8x1.8 cm<sup>2</sup> surface

Program of engineering design, construction and characterization of full ladder equipped with back-thinned CMOS pixel sensors based on experience from STAR HFT project and in collaboration with them;

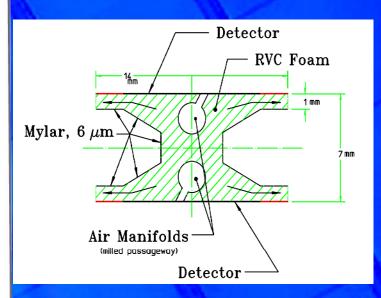

• STAR Low mass carrier: 50µm CFC+3.2mm RVC+50µm CFC (=0.11% X<sub>0</sub>);

| Ladder prototype with 50 µm |      | <u>Component</u> | Thickness (% X <sub>0</sub> ) |

|-----------------------------|------|------------------|-------------------------------|

| thin MIMOSA-5 chips         |      | Pixel Chip       | 0.054                         |

|                             |      | Adhesive         | 0.014                         |

|                             |      | Kapton Cable     | 0.090                         |

| 0.282% X <sub>0</sub> APS   |      | Adhesive         | 0.014                         |

|                             |      | Carrier          | 0.110                         |

| Carrier                     |      | <u>Total</u>     | <u>0.282</u>                  |

| LAWRENCE BERKELEY NA        | TION | AL LABORATO      | IRY                           |

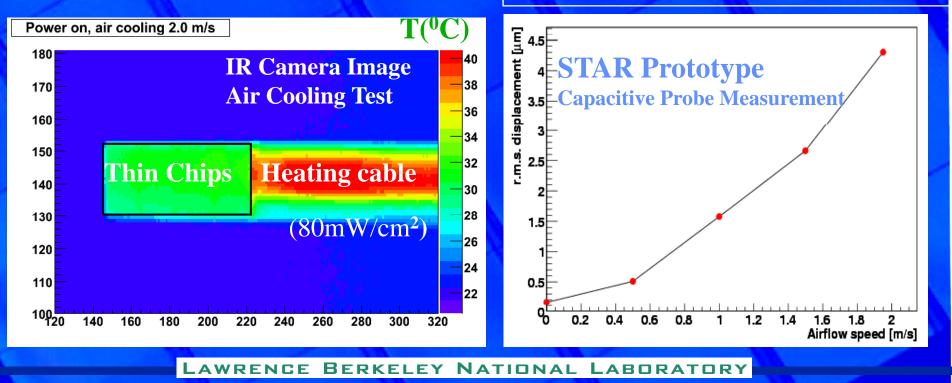

Mechanical and thermal characterization of STAR prototype,

# study of heat removal using low-speed airflow;

r.m.s displacement on unsupported end of ladder mounted at one end, w/ quasi-laminar airflow at 20° angle

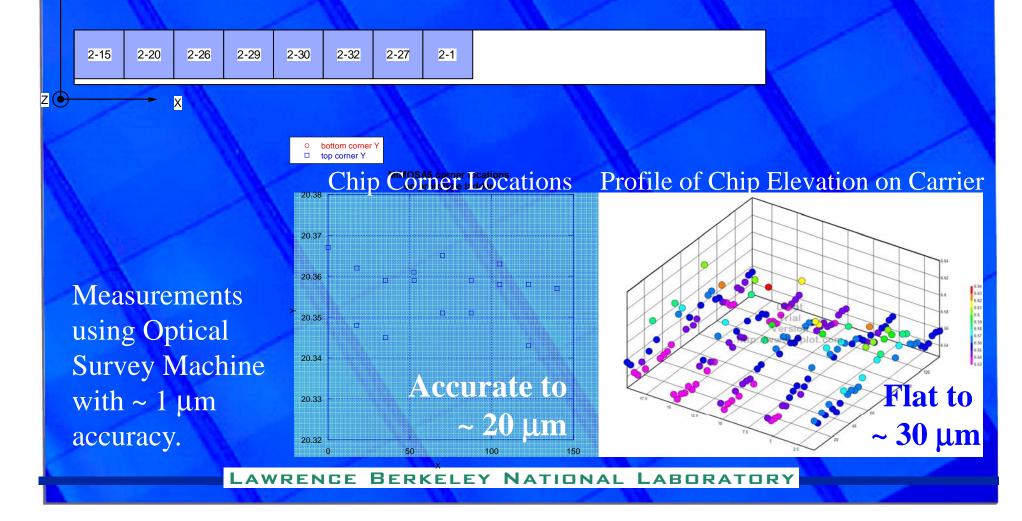

STAR study of accuracy of chip positioning on carrier:

50 μm back-thinned MIMOSA5 are positioned using a vacuum chuck with alignment bump edge and individual vacuum chuck valves;

**FEA stress analysis**

of flattened 50 µm chip

• Performed surveys of 40  $\mu$ m and 50  $\mu$ m thin chips and FEA analysis of stress on flattened chip, results suggest sandwich ladder design;

#### Measured Surface Map of 50 μm thin chip

#### ANS ΛN NODAL SOLUTION BODAT SOLVING DEC 19 2006 JAM 19 2901 STEP=1 17767+1 13:08:57 14:40:53 SUB =1 SIR = 1 TIME=1 TIME-1 (AVG) DOCTION ( 120001 DMX =.001681 \$13Y8=1 SEN =-52408 DHD( =\_011581 SMX =.110E+09 am =.01514 mpx = .211165 .151522 -142857 10384 2 mm 108323 165690 121616 211165 .243E+D8 .487E+08 .731E+08 .974E+08 121E+08 .365E+03 .6093+08 .852E+08 .110E+09 BERKELEY NATIONAL LABORATOR AWRENCE

FEA of prototype structures: (core-cooled Si/CF/RVC sandwich, Si/Al/RVC sandwich, CVD coated CF);

Core-cooled ladder concept is promising, optimisation in progress to move to prototyping in 2008;

Concept for Symmetric Ladder Sandwich Support with Air Cooling through Core

Low density (0.2-0.6 g/cc) high thermal conductivity (40-180 W/m K) foam Vertex Tracker Design with core-cooled ladders

## WP-5 Vertex Tracker Prototype

#### **Vertex Tracker Prototype**

Study tracking and vertexing over full momentum range relevant to ILC physics with small trackers updated through progress of sensor development and low mass ladder prototyping;

Use combination of accelerators at LBNL and FNAL for beam tests.

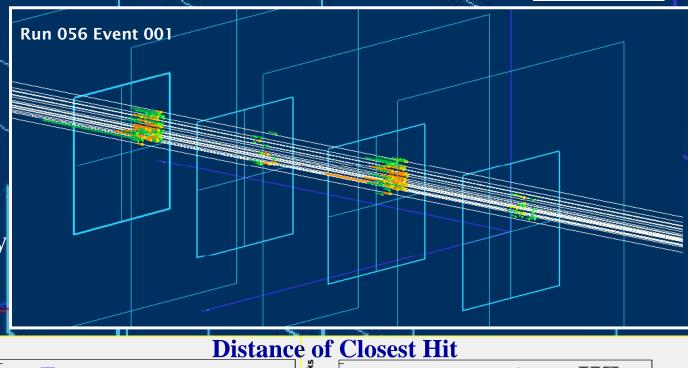

#### **Thin Pixel Pilot Telescope**

beam

Layout: 3 layers of thin Mimosa 5 sensors (17µm pixels) (40µm + 50µm + 50µm) + reference detector;

3

Sensor spacing: 1.7 cm

First beam telescope based on thin pixel sensors;

• System test of multi-layered detector in realistic conditions.

Beam: 1.5 GeV e<sup>-</sup> from ALS booster at BTS

## **Thin Pixel Pilot Telescope**

BERKELEY LAB

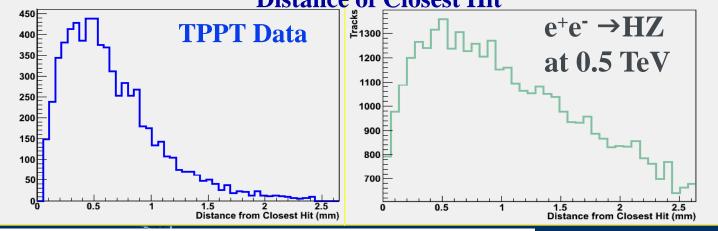

TPPT allows us to perform detailed studies of ILC VTX particle tracking with various, controllable, levels of track density (0.2-10 tracks mm<sup>-2</sup>) under realistic conditions;

TPPT layout chosen to closely resemble ILC VTX.

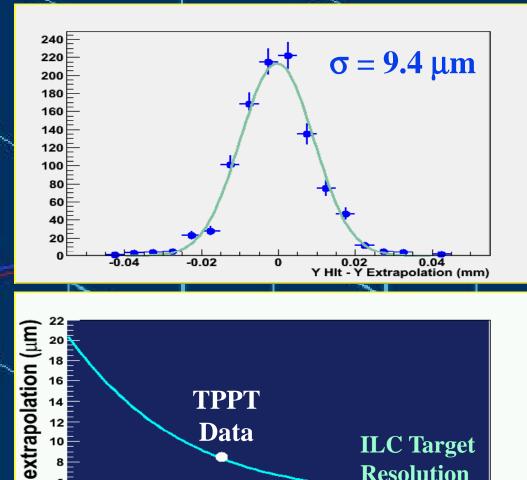

## **Thin Pixel Pilot Telescope**

Alignment performed using ATLAS optical survey machine and track alignment;

|          |          | 10 million (10 million) |      |   |

|----------|----------|-------------------------|------|---|

| Track S  | ample    | Residual                |      |   |

|          |          |                         | (µm) |   |

| 2+3 Hit  | s Tracks |                         | 9.4  |   |

| 3 Hits T | racks    |                         | 8.9  |   |

| High D   | ensity   | D                       | 9.5  |   |

| Low De   | nsity    |                         | 9.2  | ~ |

**Extrapolation Resolution** on Layer 1:  $\sigma = 8.5 \,\mu m$ meets ILC requirements.

Published on NIM A579 (2007) 675

Resolution

pt (GeV) 10

LAWRENCE BERKELEY NATIONAL LABORATORY

1

ь

#### **T-966 Beam Test Experiment at Fermilab**

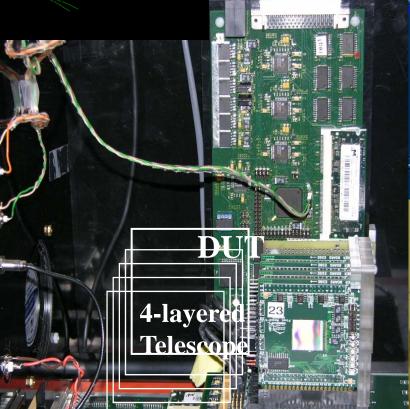

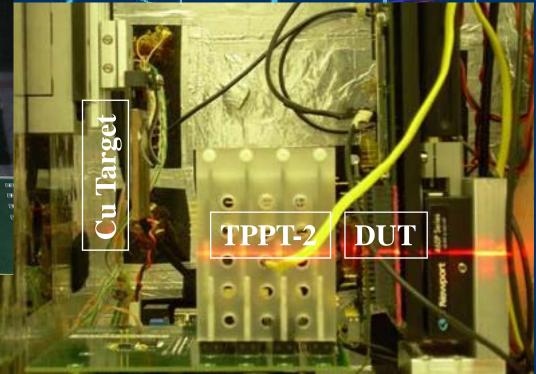

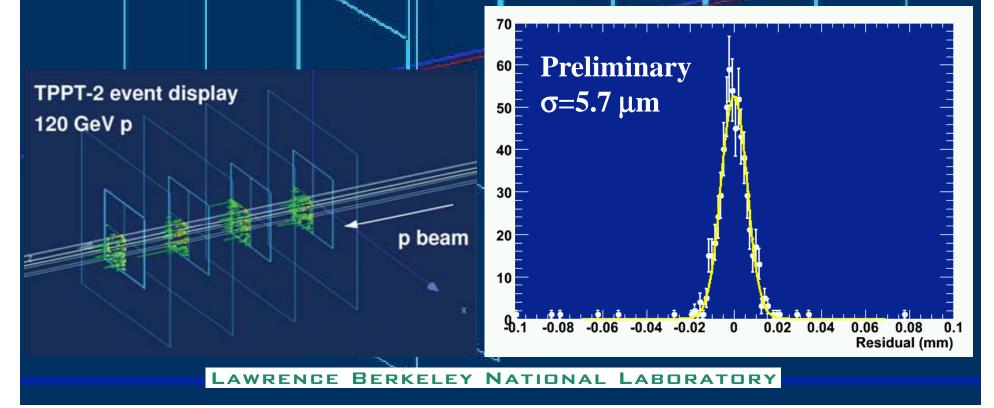

Beam Test at FNAL MBTF 120 GeV p beam-line (T-966) (UC Berkeley + LBNL + INFN, Padova + Purdue U. Collaboration)

<u>TPPT-2 telescope</u>: 4 layers of 50 $\mu$ m thick MIMOSA-5 sensors, ILC-like geometry, extrapolation resolution on DUT ~ 2-3  $\mu$ m

Study LDRD-1, LDRD-2 and LDRD-SOI sensors:

- single point resolution & sensor efficiency,

- response to inclined tracks,

- tracking capabilities in dense environment,

- vertex reconstruction accuracy with thin target,

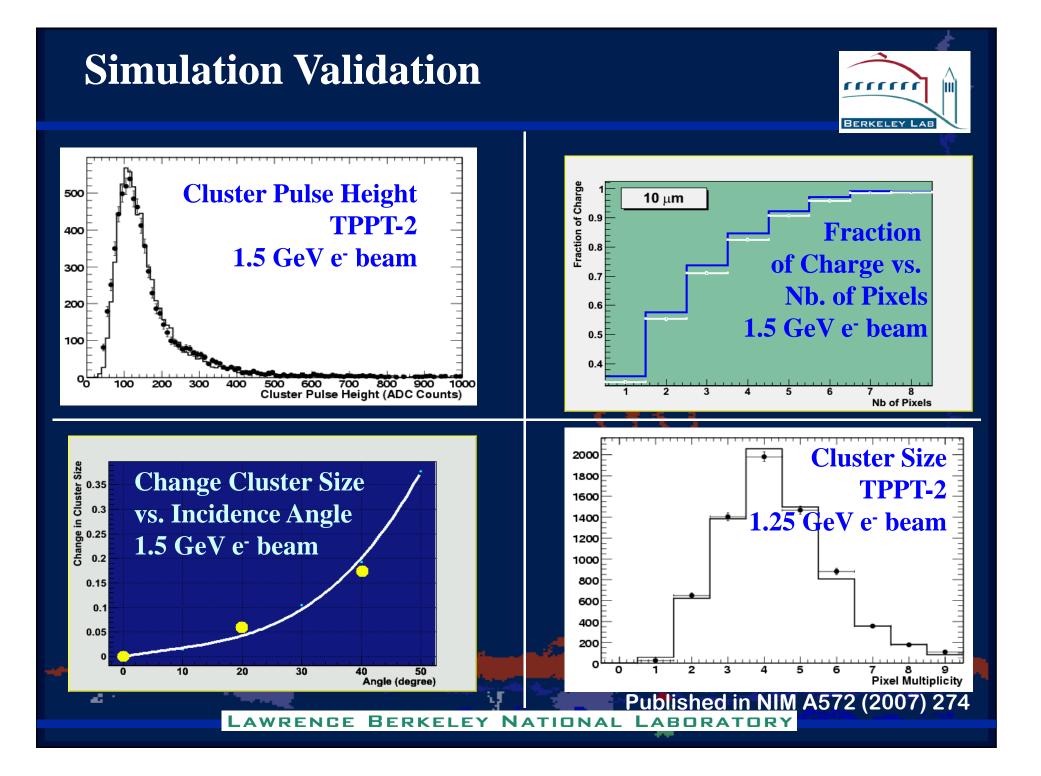

Validate simulation, test patrec and reco algorithms.

#### **T-966 Beam Test Experiment at Fermilab**

#### **Experimental Setup**

4 layers of 50µm thick MIMOSA-5 chips precisely mounted on PC boards with cut through below chip, DUT on XY stage, finger scintillator coincidence for trigger

#### **T-966 Beam Test Experiment at Fermilab**

First run June-July 2007: collected good statistics in various configurations: TPPT only for alignment & tracking studies, w/ LDRD-2 as DUT, w/ target; Operated at 20°C through forced cold air cooling, significant day/night temperature effects, need repeat track alignment daily, data analysis in progress, first preliminary results on TPPT performance:

## Thin Pixel Pilot Telescope: DAQ

Development of new DAQ system based on commercial Xilinx Virtex-5 development board with Ethernet and USB-2 ports, 64 MB SRAM + custom ADC card with 5 14-bit ADCs 100 MS/s (developed by INFN Padova);

ADC board under test, obtained  $< 100 \,\mu V$  noise over twisted pairs;

USB driver developed for data bandwidth 50 Mb/s; Firmware under development in collaboration with STAR; Linux/ROOT based online sw.

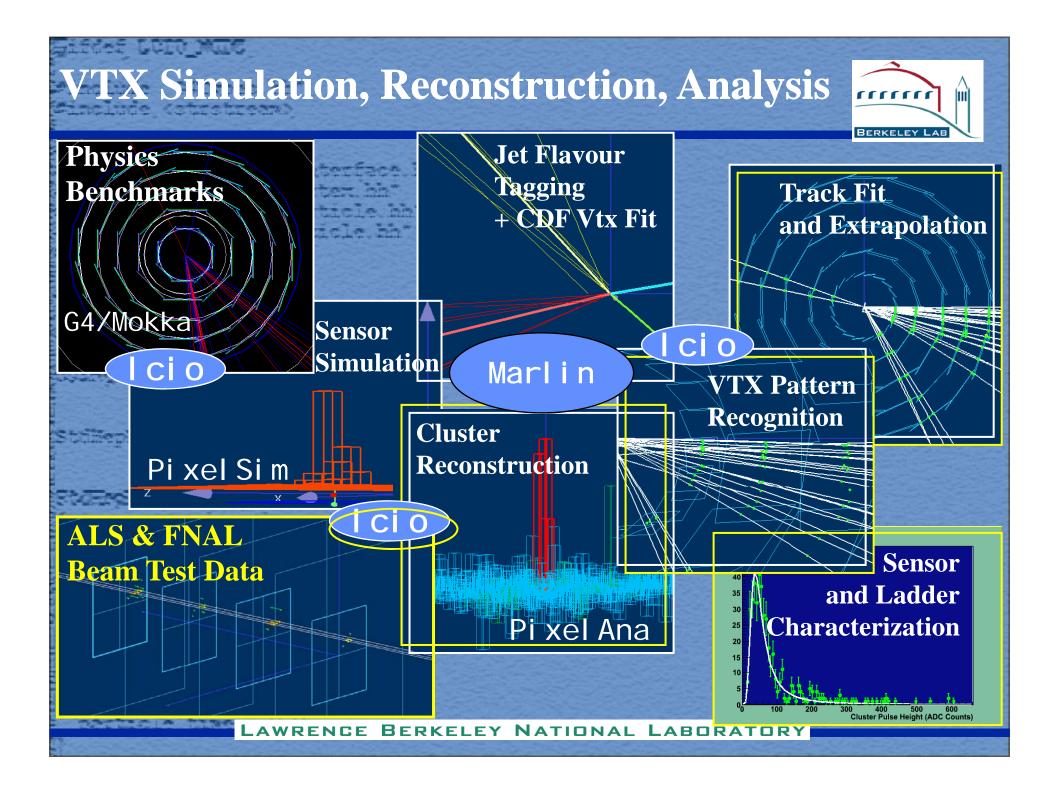

#### WP-6 Tracking and Vertexing for the ILC: Simulation, Reconstruction and Validation

#### **From Sensor Simulation to Physics Analysis**

Developing full suite of simulation and recontruction from pixel response to analysis of ILC events at highest energy;

Implemented **sensor simulation** (Pi xel Si m) & **cluster analysis** (Pi xel Ana) in Marl i n and interface to LCI 0 for beam test data (Pi xel Reader)

Marl i n Processors to analyze beam test data and validate simulation response, estimate effect of changes in sensors response and detector geometry and obtain realistic digitized simulation of full physics events and overlayed backgrounds;

CDF Vertex Fit and b-tagging ported to Marl i n framework, being tested;

**Jet Flavour Tagging** and **Physics Analysis** of Dark Matter-motivated SUSY scenarios with <u>fully simulated and digitized VTX</u> currently in progress: physics benchmarking to provide guidance to sensor R&D.

MINTERVECTOR CERCA

If woind version

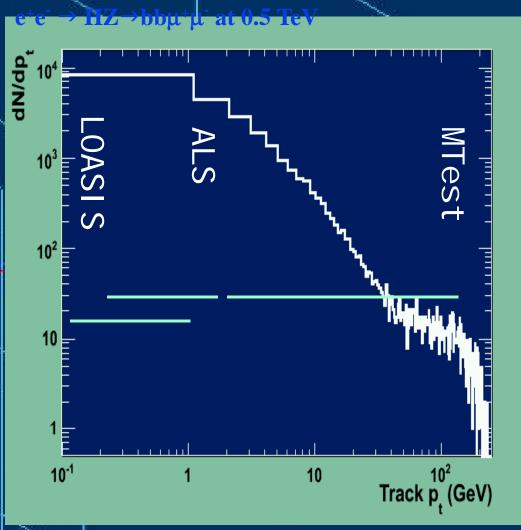

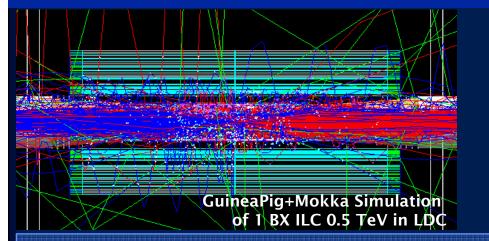

#### **Pair Background Studies at LOASIS**

Beam tests using 0.05 - 1.0 GeV e<sup>-</sup> beams at LOASI S and ALS to validate simulation.

Developing design of dedicated user test facility at exit of LOASIS magnetic Spectrometer: dedicated beamline w/ defocusing quad + beam monitor and detector cold box.

Generate library of background pair hits to overlay to hits from physics event and perform detailed simulation of occupancy, rejection and effect on event reconstruction.

LAWRENCE BERKELEY NATIONAL LABORATORY

LDRD-2 response

to ALS beam halo

#### **Project Funding Sources and Spin-offs**

**Project Funding**

LBNL LDRD Grant: Advanced Pixel Detectors for the ILC (FY05-07) DOE LCRD Grant: Design of a Monolithic Pixel Detector Ladder (FY06-07) PD Core Budget allocated to ILC Project (Sw, Mechanics, CMOS from FY08) LBNL Strategic Grant: Detector Test Infrastructures at LOASIS and ALS (FY08)

**External Collaborative Funding**

Collaborative effort on SOI and DAQ with INFN Padova, open to other groups

Spin-off Projects

LBNL LDRD Grant: Advanced Detectors for Beam Monitoring and Imaging at Short Pulse X-Ray and FEL Facilities. (FY08-FY10)

Comparative Study of Performance of LDRD-series CMOS chips and Conventional Film for Electron Microscopy at NCEM (w/ EG, NCEM)