- Introduction of the DEPFET collaboration and MPI Semiconductor Laboratory

- DEPFET in a nutshell

- Current achievements

- Future Plans

|           | DEPFET/Ladder<br>Sim. and Irrad. | Auxiliary ASICs<br>Development | System<br>Development | System Tests and<br>Test Beams |

|-----------|----------------------------------|--------------------------------|-----------------------|--------------------------------|

| Aachen    |                                  |                                | Х                     |                                |

| Bonn      |                                  | Х                              | Х                     | Х                              |

| Karlsruhe | Х                                |                                |                       |                                |

| Mannheim  |                                  | Х                              | Х                     | Х                              |

| Munich    | Х                                |                                |                       | Х                              |

| Prague    |                                  |                                | Х                     | Х                              |

| Valencia  |                                  |                                | Х                     | Х                              |

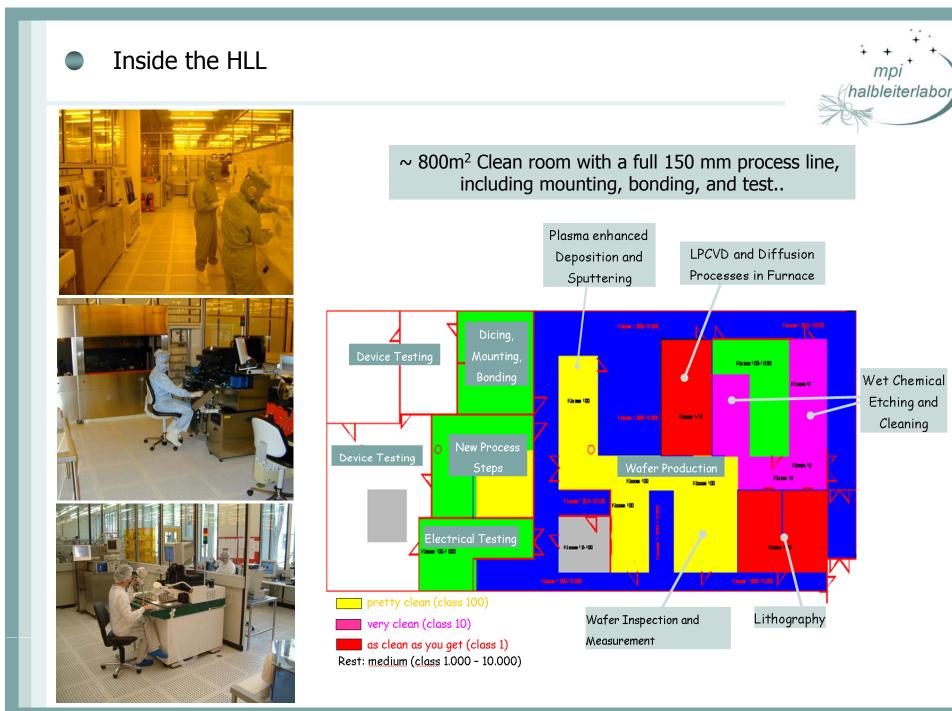

- Founded in 1992, since 2000 at the Siemens Campus in Munich

- ~60 Scientists, Engineers, Technicians, Students .... design, produce, and test ...

- ...silicon detectors (CCD, APS, SiPM..) for experiments in HEP, X-ray astronomy, synchrotron radiation ...

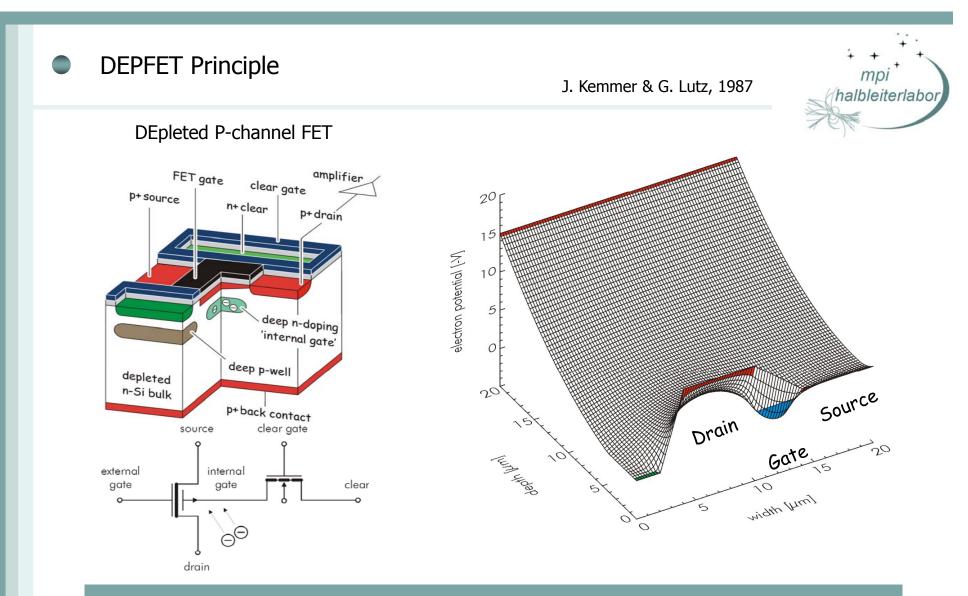

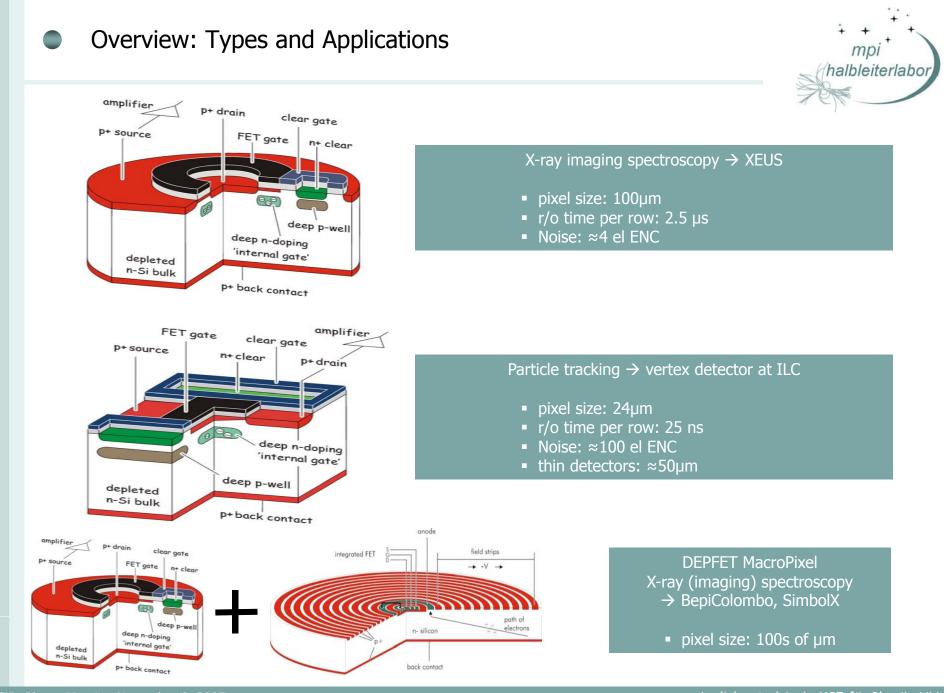

- fully depleted sensitive volume, charge collection by drift

- Charge collection in "off" state, read out on demand

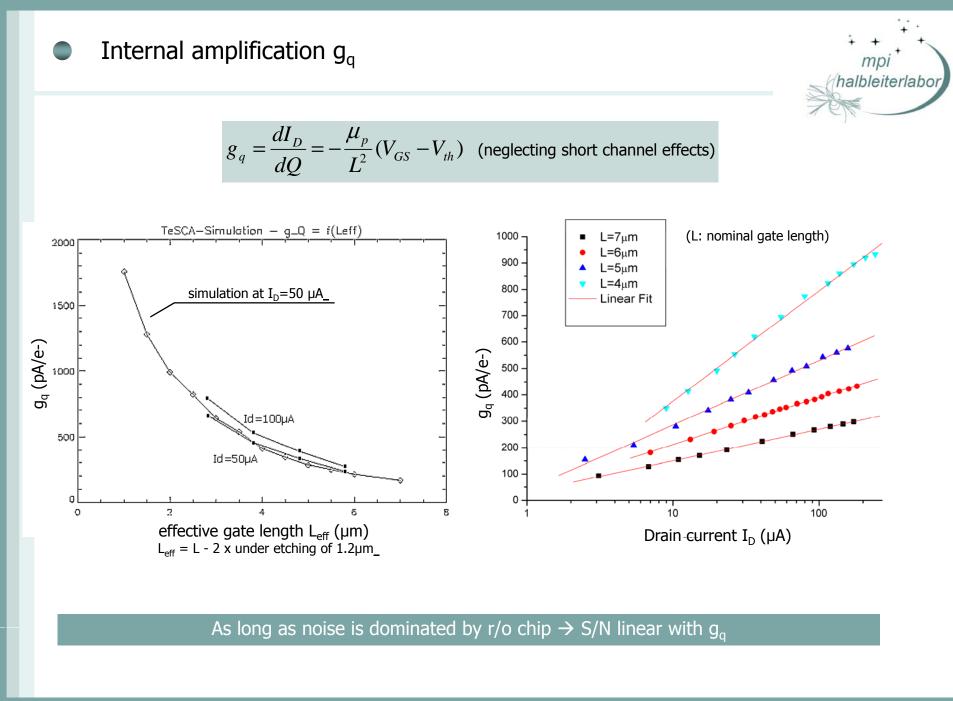

- internal amplification  $\rightarrow$  q-I conversion, scales with gate length and bias current

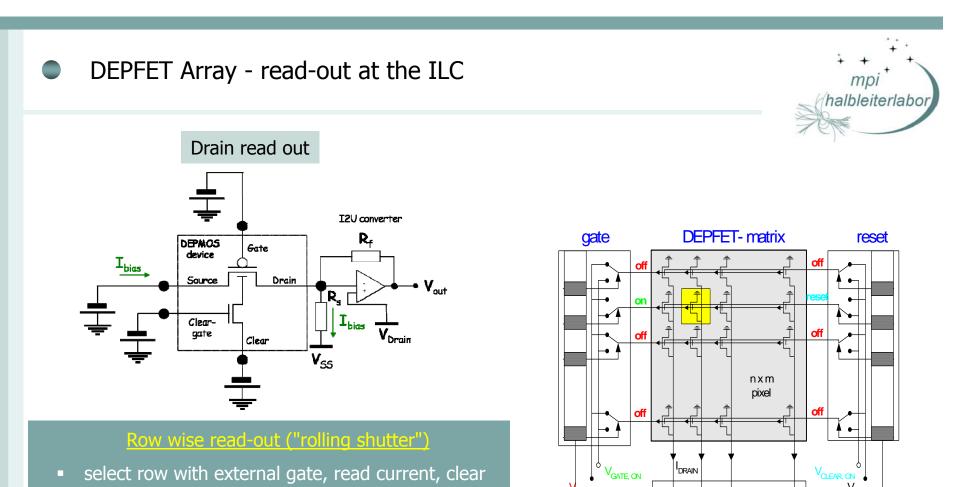

- select row with external gate, read current, clear DEPFET, read current again  $\rightarrow$  the difference is the signal

- Low power consumption

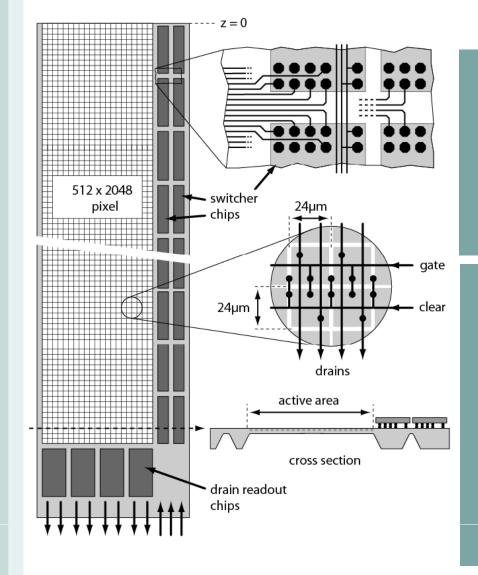

- two different auxiliary ASICs needed

- limited frame rate

SiD, Phone Meeting November 9, 2007

cap. load at the f/e adds noise

V<sub>CLEAR, ON</sub>

V<sub>CLEAR-Control</sub>

drain 🕁

0 suppression

$V_{\text{CLEAR, OFF}}$

DRAIN

GATE OFF

# ILC VXD baseline design

## Just as a starting point for the R&D!

- 5 layer, old TESLA layout

- 10 and 25 cm long ladders read out at the ends

- 24 micron pixel

- design goal 0.1% X<sub>0</sub> per layer in the sens. region

## Strategy to cope with the background:

- read ~20 times per train

- store data on ladder

- transfer the data off ladder in the train pause

→ row rate of 40 MHz

- read two rows in parallel, doubles # r/o channels but:

$\rightarrow$  row rate 20 MHz  $\odot$

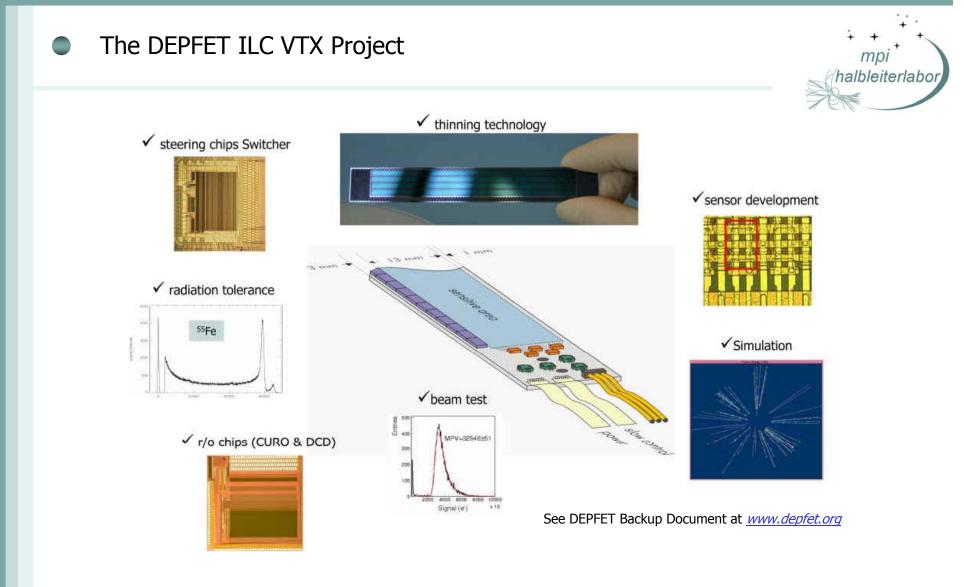

# In Summary: Achievements

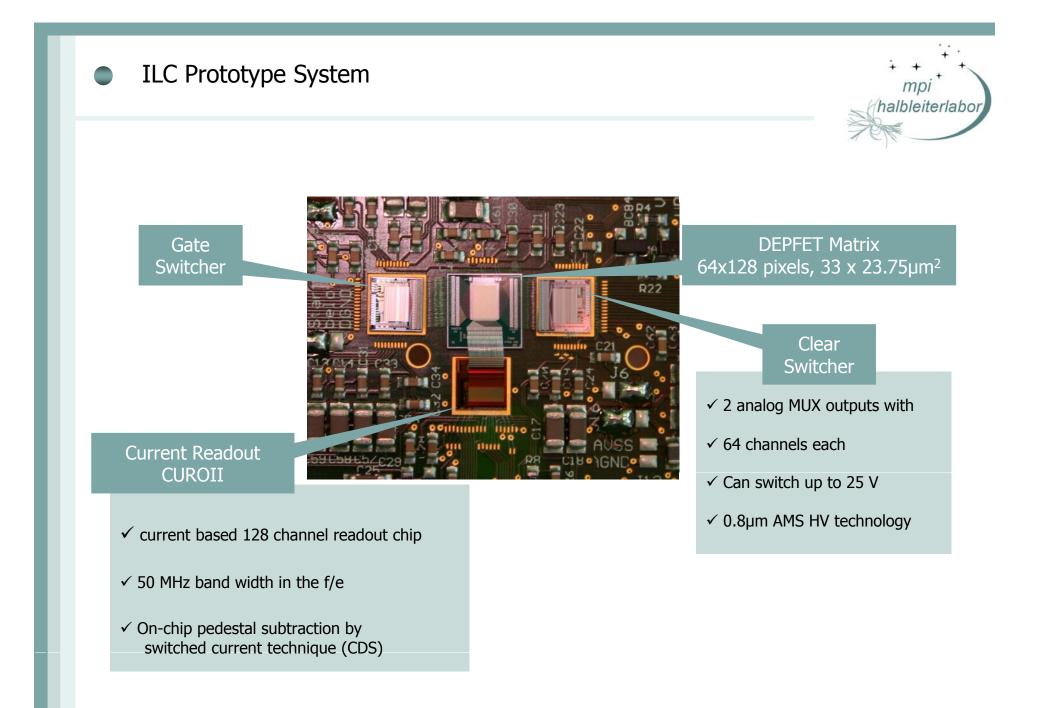

- ✓ Prototype System with DEPFETs (450µm), CURO and Switcher

✓ test beam @ CERN:

- ✓ S/N≈110 @ 450  $\mu$ m  $\leftarrow$  → goal S/N ≈ 20-40 @ 50  $\mu$ m

- ✓ sample-clear-sample 320 ns  $\leftarrow$  → goal 50 ns

- ✓ s.p. res. 1.3  $\mu$ m @ 450  $\mu$ m  $\leftarrow$  → goal ≈ 4  $\mu$ m @ 50  $\mu$ m

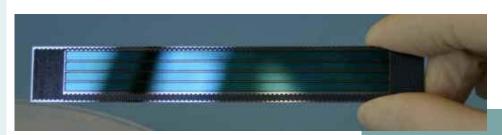

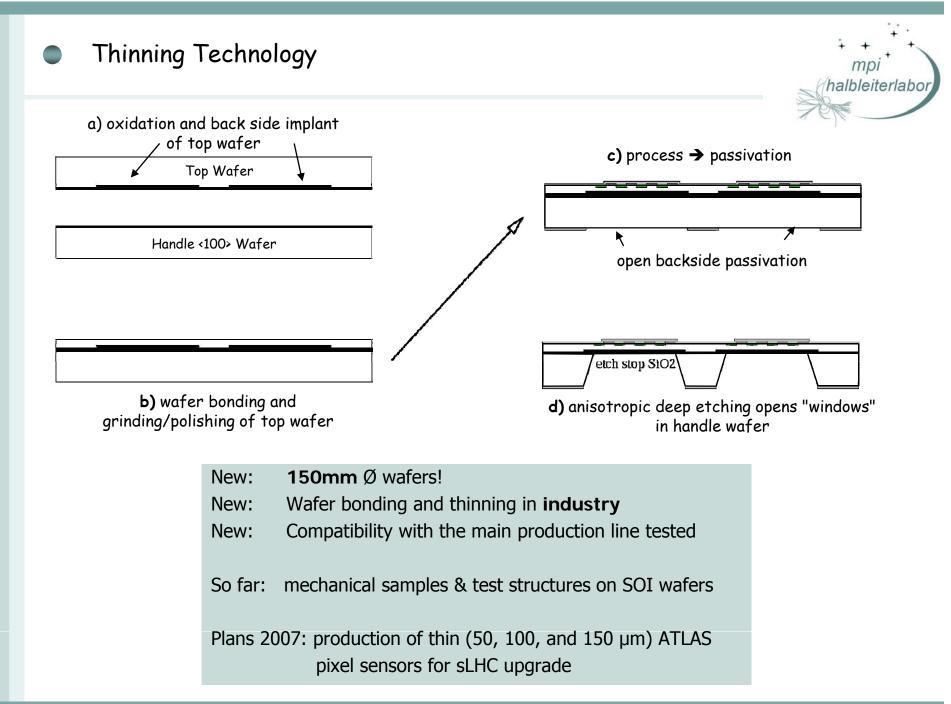

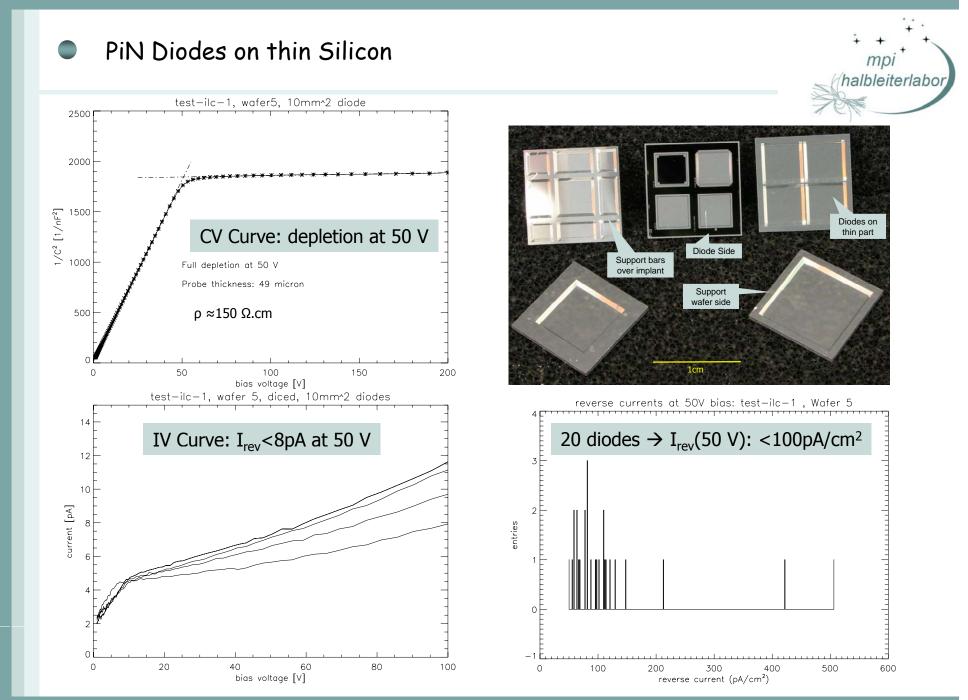

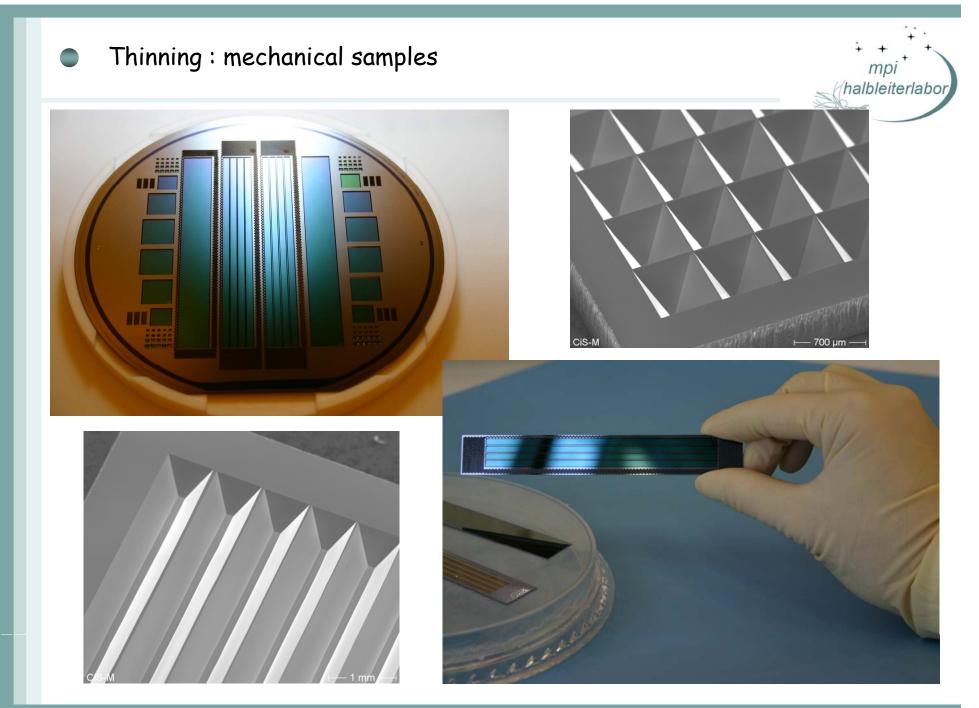

- $\checkmark$  Thinning technology established, thickness can be adjusted to the needs of the experiment (~20  $\mu m$  ... ~100  $\mu m$ )

- $\checkmark~$  radiation tolerance tested with single pixel structures up to 1 Mrad and  ${\sim}10^{12}~n_{eq}/cm^2$

- ✓ Simulations show that the present DEPFET concept can meet the challenging requirements at the ILC VXD.

- ✓ Production of 2nd iteration of DEPFETs was finished summer 2007

- ✓ New Switcher3 chips tested and functional

- ✓ New r/o chips DCD designed for read-out of large matrices are under test

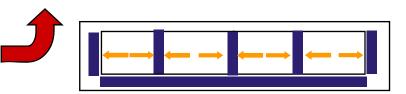

# The challenge: read-out speed in long ladders!

### 1. Row wise read-out

row wise CDS with the r/o chips at the short side of the ladder

#### <u>Advantage</u>

- Low power consumption!

- No advanced interconnection technologies needed

#### <u>Disadvantage</u>

- limited frame rate

- high capacitive load (long drain lines) at the input

### 3. Combination of those two

- subdivide large arrays into smaller units

- $\rightarrow$  smaller cap. load

- $\rightarrow$  more relaxed row rate

- challenging interconnection ( $\rightarrow$ "3D"?)

- → find optimum for a specific application balancing the pros and cons under consideration for the ILC VXD

2. Hybrid-pixel-like approach: one amp. per pixel

#### <u>Advantage</u>

fast! (~ns), frame rate comparable with hybrid pixels

### <u>Disadvantage</u>

- challenging interconnection between sensor and r/o chip

- high power consumption

intended for the focal plane at the XFEL

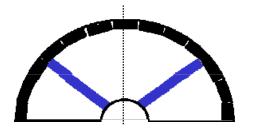

#### Why SiD VXD layout for the DEPFET?

- Main difference is long barrel  $\leftarrow \rightarrow$  short barrel with endcap

- in layers 2..5: 25 cm ladder  $\rightarrow$  12.5 cm ladder

- lower C<sub>load</sub> at the input, relaxed speed requirements in these layers

$R_{in}$ = 14 mm,  $R_{out}$  =71mm

### Why DEPFET for the SiD?

- wafer scale sensors (150 mm) in barrel and discs

- 1 ladder/wafer or 1/2 or 1/4 disc per wafer, no stiching needed

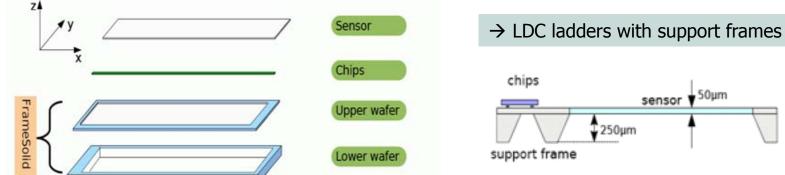

- thinned all-silicon ladders or discs with or without supporting frames

- DEPFET is an active pixel sensor, first amplification in pixel → good candidate for 3D integrated detector systems.

- MacroPixels (DEPFET + Drift Detector) could be a natural extension of the VXD technology into a pixelated tracker...

Potential Issues .....

- insensitive area at the end of the ladder needed for the r/o and data transmitting ASICs  $\rightarrow$  3D integration could help here

- additional material at the end of barrels (services)

- concerning the discs: it is just an idea so far, we need a design study to come to sound proposal...the layout is pretty tricky!

- ✓ MC studies: short barrels and discs  $\leftarrow$  → long barrels

- Mechanics and all-silicon VXD: We can certainly make some mechanical samples for the construction of a mechanical model.

- ✓ We started already a project to see the feasibility of the 3D integration approach. Sharing the experience and results with the group at FNAL could be very helpful.

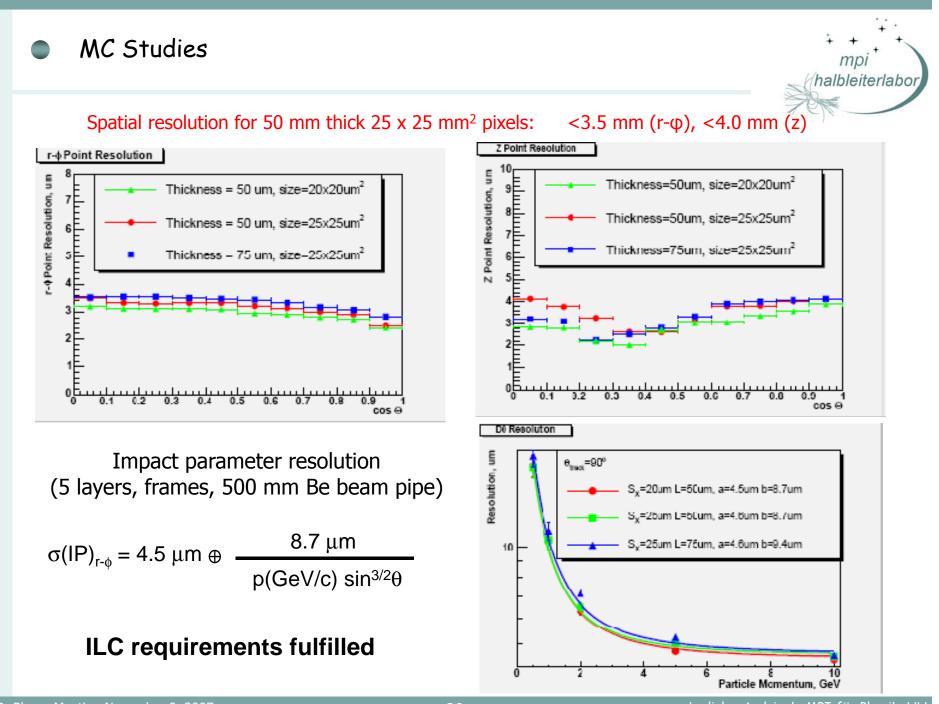

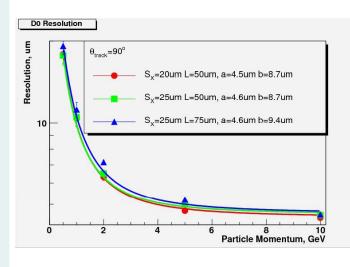

# Simulation: LDC Geometry description

Sensitive layer thickness =  $50 \ \mu m$ Pixel size =  $25 \times 25 \ \mu m^2$

|   | Radius<br>(cm) | Ladders | Length<br>(cm)  |

|---|----------------|---------|-----------------|

| 1 | 1.5            | 8       | 10.0            |

| 2 | 2.6            | 8       | $2 \times 12.5$ |

| 3 | 3.8            | 12      | $2 \times 12.5$ |

| 4 | 4.9            | 16      | $2 \times 12.5$ |

| 5 | 6.0            | 20      | $2 \times 12.5$ |

sensor y 50µm

Material up to first layer : beam pipe (500 µm beryllium)