## **SiD KPiX Electronics**

David Strom – University of Oregon

- Electronics requirements

- KPiX concept

- Performance

- Plans

#### Si-W work – personnel and responsibilities

| Y. Karyotakis | V. Radeka   | B. Holbrook<br>R. Lander<br>M. Tripathi | J. Brau<br>R. Frey<br>D. Strom          | M. Breidenbach,<br><b>D. Freytag</b> , N. Graf<br><b>G. Haller</b> , <b>R. Herbst</b><br>T. Nelson |

|---------------|-------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------|

| Annecy        | BNL         | UC-Davis                                | Oregon                                  | SLAC                                                                                               |

| Mechanics     | Electronics | Bump Bonding<br>Cabling<br>Mechanics    | Si Detectors<br>Mechanics<br>Simulation | Electronics<br>Mechanics<br>Simulation                                                             |

| SID           |             | 1                                       | 29 January– David Strom – UO            |                                                                                                    |

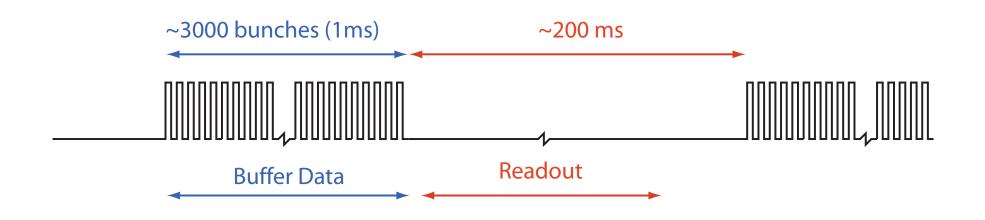

# Bunch Structure at the ILC

- $\bullet$  Duty cycle of bunches is low,  $~\sim 1/200$

- ⇒ Only provide high current to front end during bunch train Reduces power

- In the high granular SiD concept, occupancy is low

- $\Rightarrow$  Buffer data during the bunch train

Potential to minimize digital interference to analog signals

2

How many buffers are needed?

Study<sup>\*</sup> with Luminosity =  $3 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, 2820 bunches/train

The following processes were simulated:

- $e^+e^- \rightarrow hadrons \ e^+e^-$

- $e^+e^- \rightarrow \mu^+\mu^-e^+e^-$

- $e^+e^- \rightarrow e^+e^-e^+e^-$

- Bhabhas

- Radiative bhabhas

showed that with 4 buffers, we have less than 1% dead time, everywhere in the ECAL (down to  $\theta = 120 \, mrad$ ).

HCAL occupancy should be lower.

\* Ron Cassel, SiD LCWS mini-workshop 17 March 2005.

SID

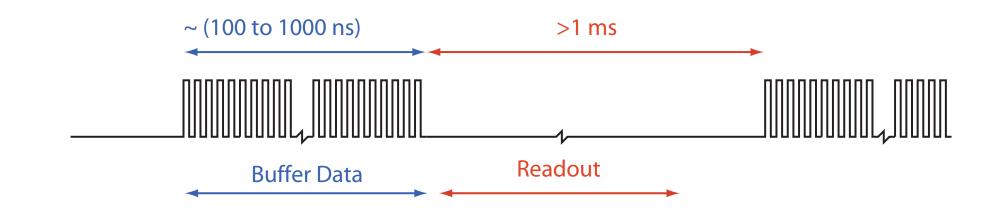

### Bunch structure in warm machines

- Requires faster power pulsing for electronics:

- $\Rightarrow$  10µs possible in simulation (but not yet demonstrated)

- $\Rightarrow$  100 $\mu s$  would give < 1.25% duty cycle

- Faster clock needed for better timing resolution

- At 50 MHz clock rate, could transfer 400kbits/train in 8msec  $\Rightarrow$  Need  $\sim$  25kbits/train for one buffer

- $\Rightarrow$  Zero suppression possible could readout in less than 1ms

#### Dynamic range

- Electromagnetic Calorimeter (300  $\mu m$  silicon sensors)

- smallest signals 1MIP (1MIP = 24,000 electrons = 3.8 fC)

- largest signals 2000 MIPs (8.0 pC) at 1 TeV

- GEM based HCAL

- typical signals 5 to 30 fC (depends on gain used)

- RPCs

- typical signals  $\sim$  0.2 to 10pC avalanche mode

- (more than 100 pC for streamers, depending on gas)

- Tracker requires noise less than 1000 electrons

$\Rightarrow$  Design electronics for  $\sim 0.16\,fC$  to  $\sim 10\,pC$

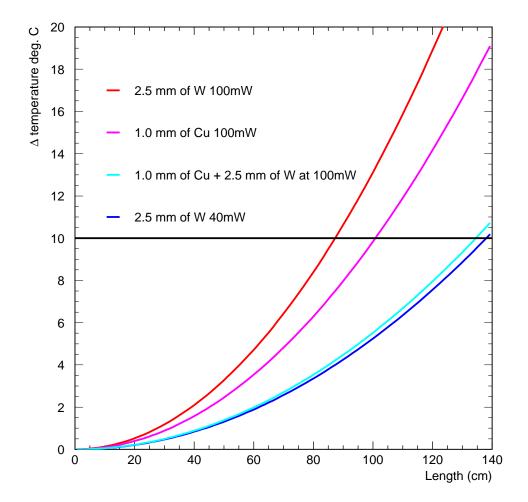

### Power requirement – Can we get the heat out?

Back of the envelope calculation of  $\Delta$  temperature in ECAL

Thermal Conductivity:

- W alloy 120W/(K-m)

- Cu 400W/(K-m)

Need to reduce heat to below  $100mW/wafer (\sim 1mW/cm^2)$ .

HCAL will be easier

⇒ lower channel density

⇒ thicker absorber

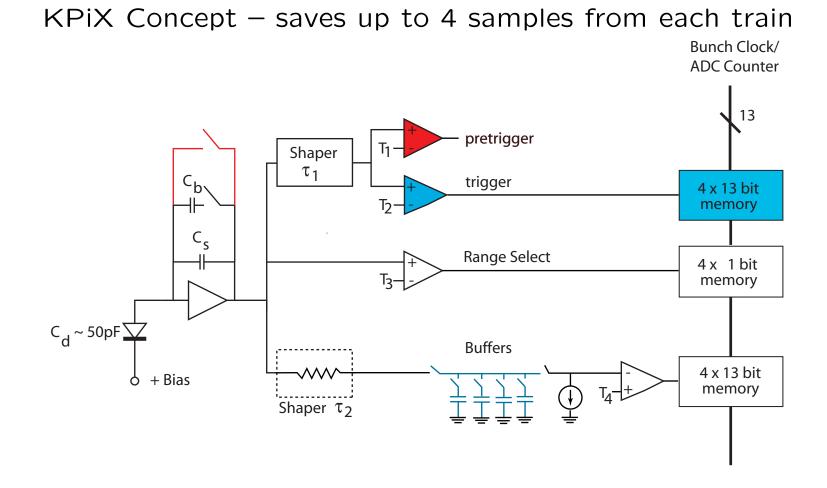

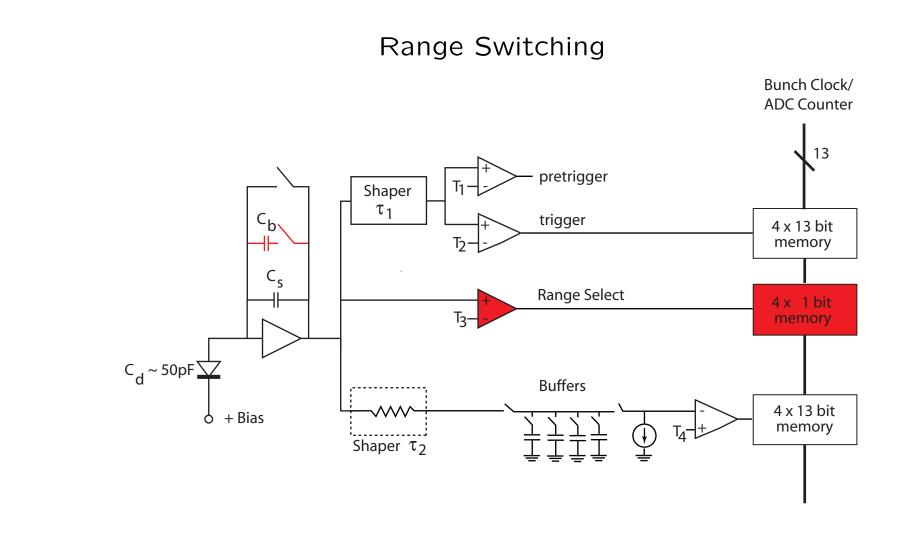

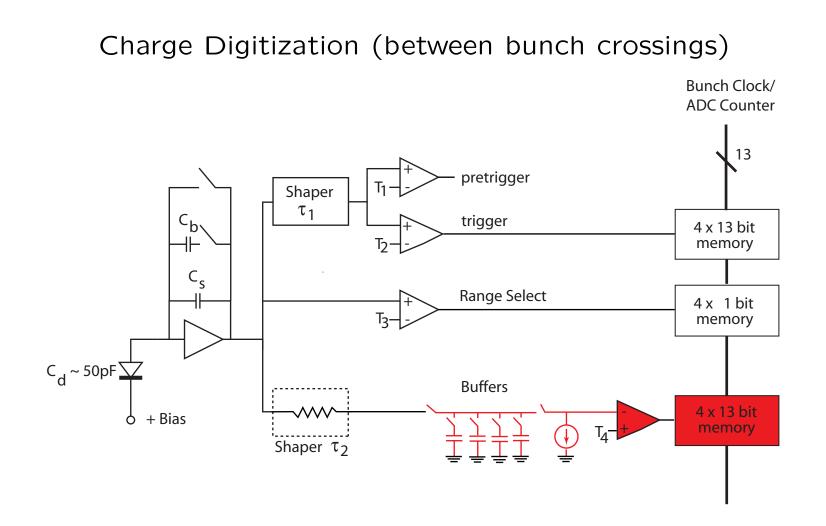

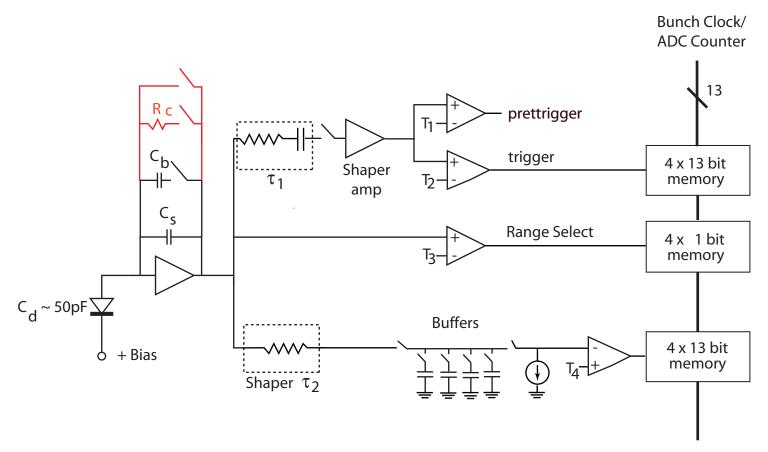

- Threshold  $T_1$  is used to inhibit resets

- Threshold  $T_2$  is used to enable data storage

- Bunch clock (time) is stored in SRAM

- Analog charge is stored on capacitors

(set at 2 × noise)

(set at 4 × noise)

(13 bit precision)

(13 bit precision)

- Dynamic range switching (driven by threshold  $T_3$ ) selects  $C_s$  or  $C_b || C_s$

- $\Rightarrow$  Feedback capacitor  $C_b = 10 \, \mathrm{pF}$  stores up to  $10 \, \mathrm{pC}$

- $\Rightarrow$  Feedback capacitor  $C_s = 400 \, \text{fF} \, (0.3 \, \text{fC gives } 0.7 \, \text{mV})$

- $\Rightarrow$  Feedback capacitor  $C_s = 200 \, \text{fF}$  for tracker (0.16fC gives 0.8 mV)

- N.B. Switches to capacitors closed for several RC times so signals settle

- Time needed to discharge each capacitor stored in 13 bit memory

- Time is combined with range bit to correct amplitude

Additional features not shown in simple schematic:

- Built-in calibration system with 2 calibration ranges and up to 4 injections per bunch train

- Choice of two values for pretrigger and trigger thresholds

- Bias current servo system for DC coupled detectors

Additional features added in prototype versions 3 or 4:

- Polarity selection (mainly for GEMs)

- External trigger for test beam

- Nearest neighbor trigger logic

- Staticly selectable feedback capacitor for tracker

#### All these features are tested and working

# Chip Size

- Chip is implemented in TSMC 0.25 $\mu$ m CMOS

- Single analog channels comfortably fits into  $200\mu m$  by  $500\mu m$  cell

- Overall chip size (1024 channels) approximately:

$18\,mm\times 6.5\,mm\sim 1.2\,cm^2$

- Aspect ratio helps in routing traces on silicon sensors

- Could not reduce chip size without making bump bounding more difficult

## Overall chip size close to optimal

#### Performance – 64 channel prototype

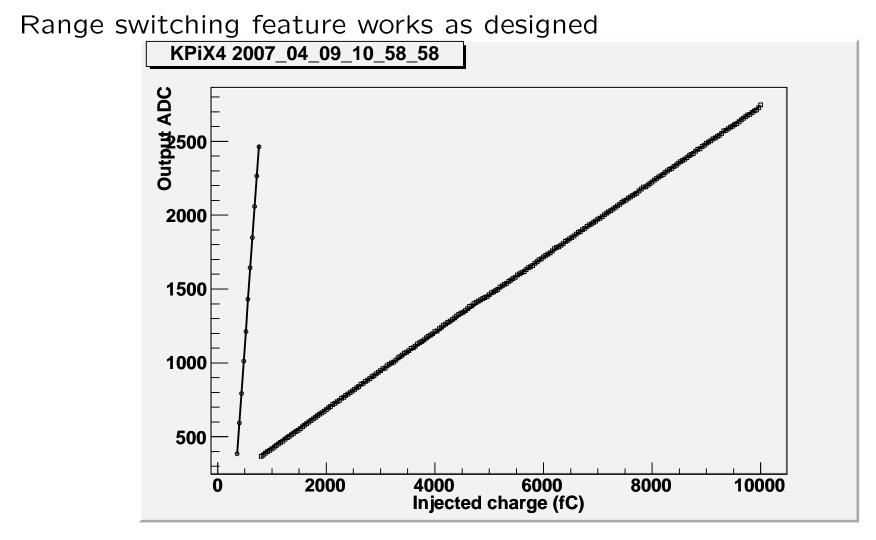

Linear behavior extends beyond 10 pC (Nonlinear behavior extends range by 50% or more)

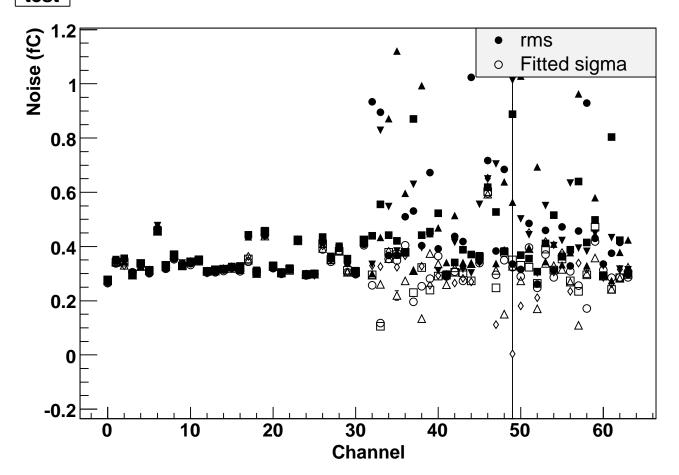

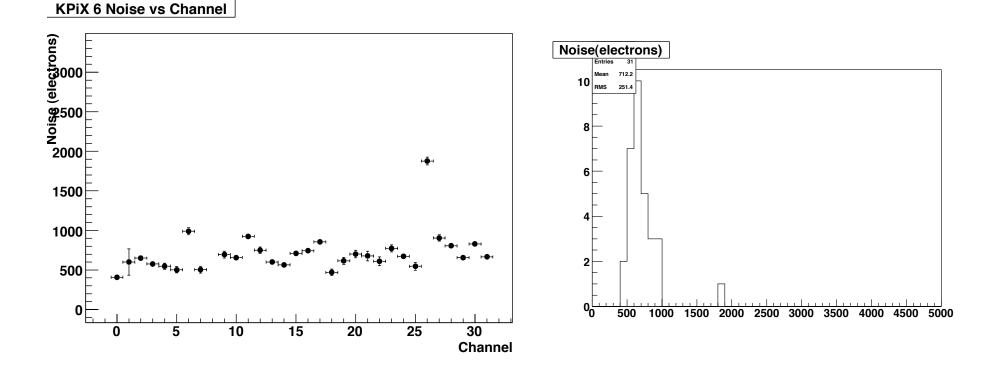

KPiX 6 noise in the digitized charge value similar to 5 and 4. test

Bit errors observed in KPiX5 and 6 in upper 32 channels.

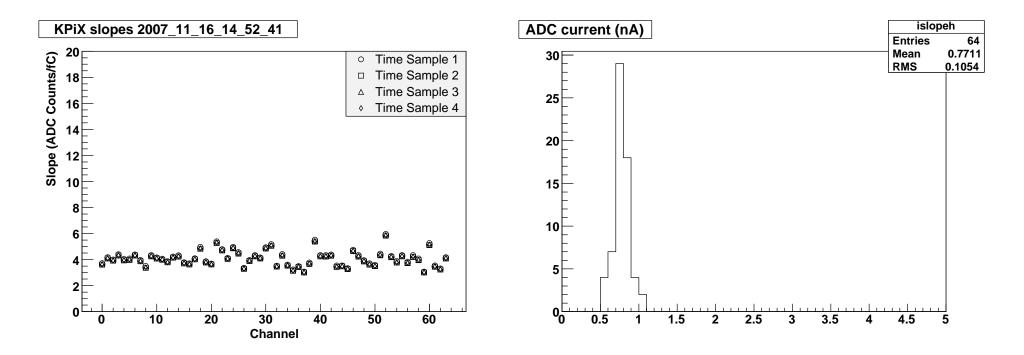

Different symbols correspond to the four buffers on each channel

- Meets spec of signal noise 8:1 for MIPs in ECAL, but not yet at full capacitive load

- Tracker would like signal to noise of 20:1 29 January- David Strom UO

#### Performance adequate for externally triggered ECAL test beam

SID

Improvements in KPiX 5 and 6

- Many layout changes to reduce coupling

- Improved isolation of digital and analog sections

- Improved current mirrors for equalization of gains

- Improved shaper in trigger branch disconnect when threshold is reached

- Improved threshold in trigger branch

## Noise in trigger branch is now very reasonable in KPiX 6.

•First 32 channels only, second 32 have possible bit errors in KPiX 5&6

- should be fixed in next version

- ADC noise is similar to KPiX4

- Noise versus capacitance is still under investigation

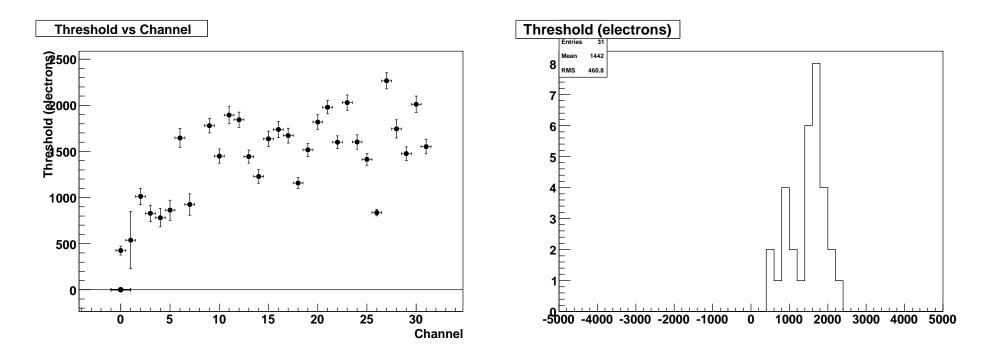

## Trigger Threshold are very consistent for channels

• RMS is only 460 electrons!

• We will need to control and understand the thresholds at the level of 5% of MIP (1200 electrons) or better to keep the constant term in the calorimeter energy resolution below 1%.

### ADC gain is more equal

Inferred current in current source agrees with simulation.

(We will effectively lose about 1 bit of granularity from this spread. This is not expected to be a problem  $\Rightarrow$  still have 16.6 bits of dynamic range.)

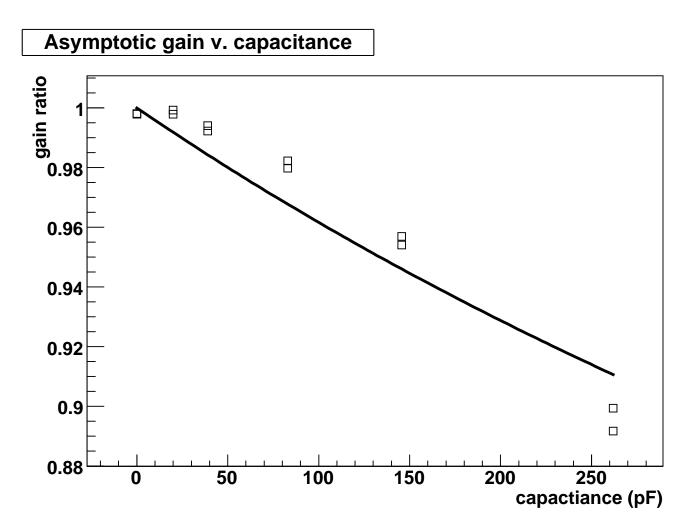

Cross talk – depends on "dynamic capacitance" of charge amplifier Asymptotic gain versus capacitance between two channels

Dynamic capacitance is  $\sim$  2.4nF implies very small cross talk from pF stray capacitances.

SID

## Main architectural change for KPiX 7

- Use continuous reset provided by  $R_c \sim 10 M \Omega$ .

- Remove when trigger or prettrigger occurs

- can accommodate almost any linear collider bunch spacing.

- old functionality available under register control

- Will still need low resistance reset after a DAQ cycle.

SID

29 January– David Strom – UO

#### Plans

- Broad overview in this talk doesn't do justice to all of the detail changes that are desired for KPiX (Dieter has a list of 36 proposed changes of which 9 are completed)

- Changes to digital core are needed to accommodate a flexible number of bunches, etc.

- At least one intermediate submission is needed with more than 64 channels (e.g. 128 or 256)

- Submissions will be at least four month apart

- Earliest date for 1024 channel chip is eight months from now