# Status Report on ADC developments @ LPC Clermont-Ferrand

### Laurent ROYER, Samuel MANEN

Institut National de Physique Nucléaire et de Physique des Particules

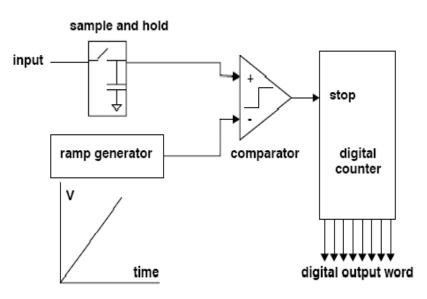

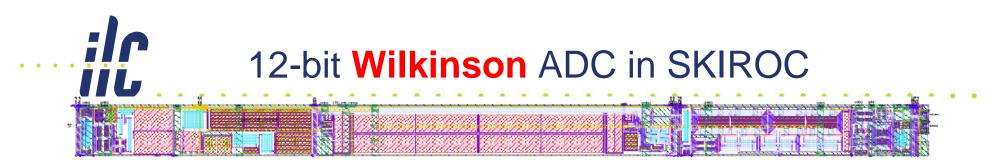

## A 12-bit 3.5V Wilkinson ADC

<u>Characteristics:</u>

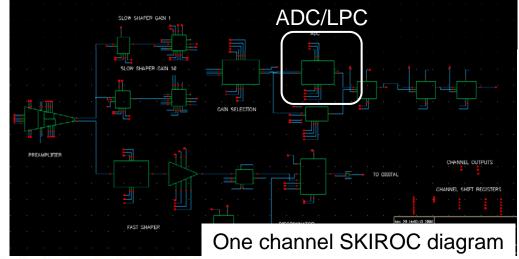

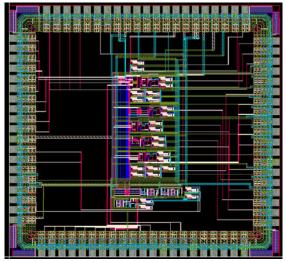

Layout of the ADC

- Techno: BiCMOS SiGe 0.35µm

- Power consumption: 3 mW @ 3.5V

- Power pulsing

- Conversion time : 80µs @50MHz

- Differential architecture

- Open loop ramp generator

- Die area: 0.12 mm<sup>2</sup>

#### Status:

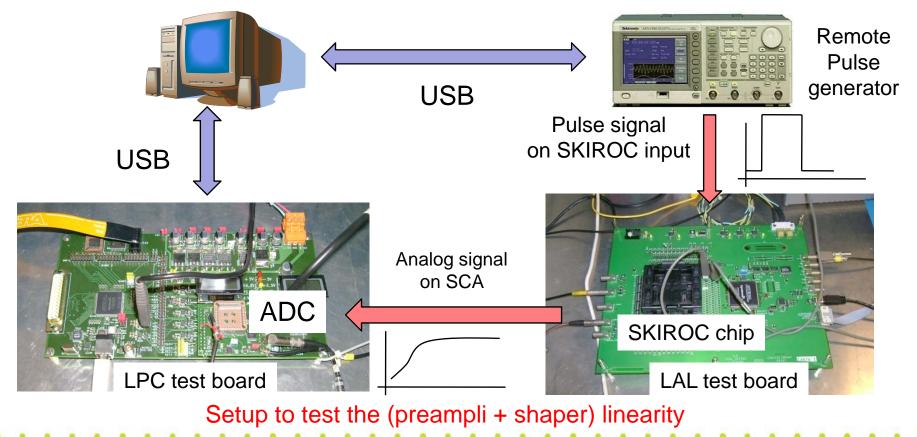

- One test board given by LAL @ LPC to test ADCs

- LabView Control program developed by LAL used to configure SKIROC through USB interface

- Several bugs found in the digital part (in FPGA)

- Fixed by LAL

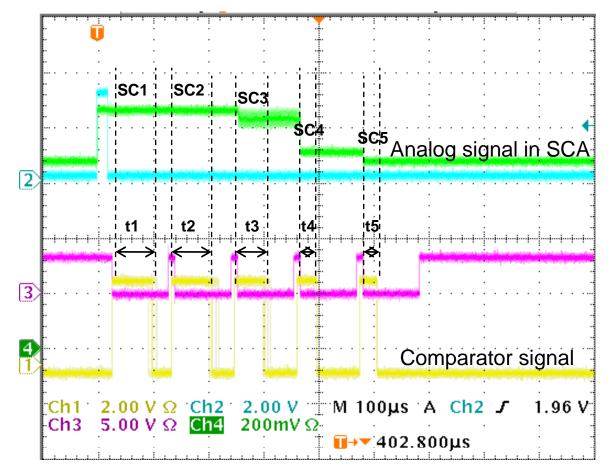

- ADC functionality checked with scope

- To measure ADC performance, the automatic transfer of the ADC digital data from FPGA to PC via USB is required

- under devpt @ LAL

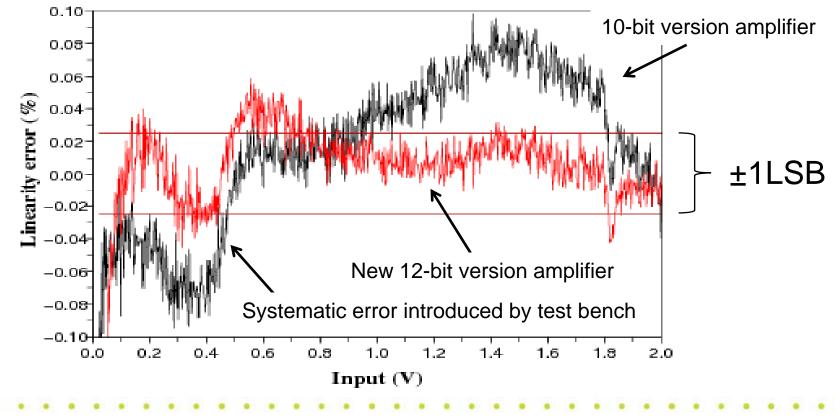

- We have adapted the setup of the test bench @ LPC to measure linearity of the analog channel (preamp + shaper) and to compare results with those obtained @ LAL

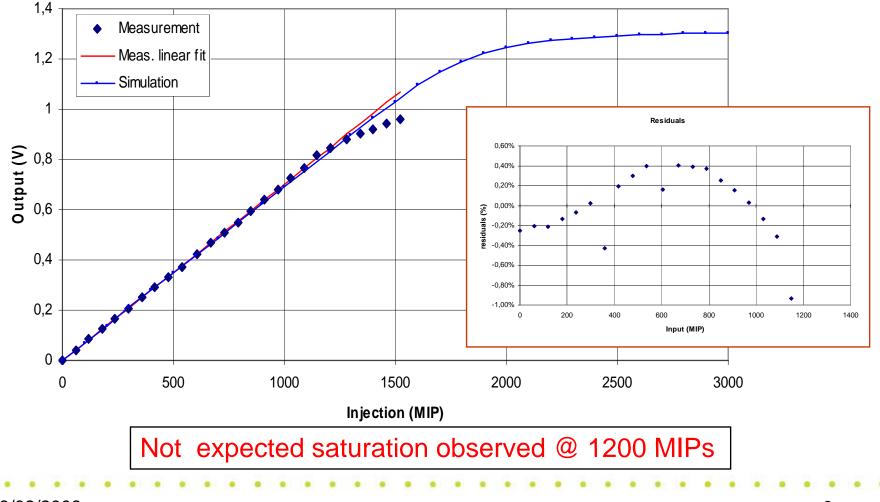

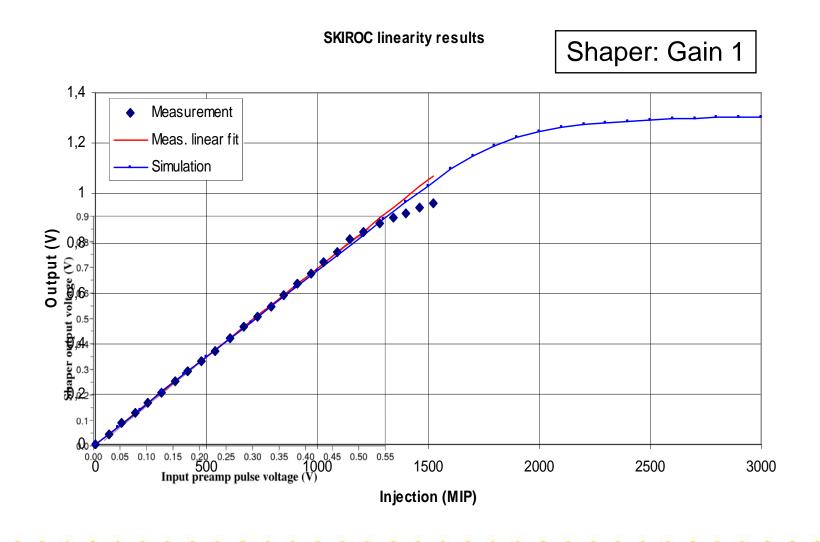

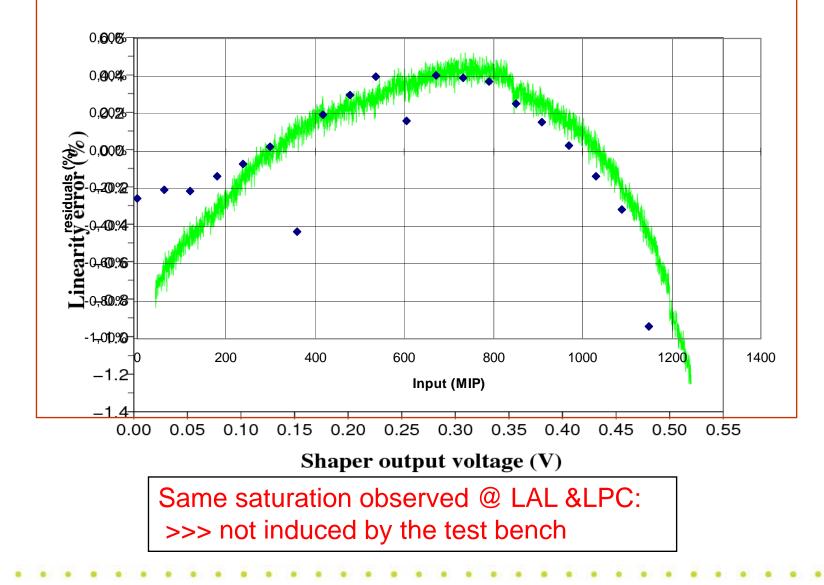

#### SKIROC linearity results

Linearity measurements @ LPC

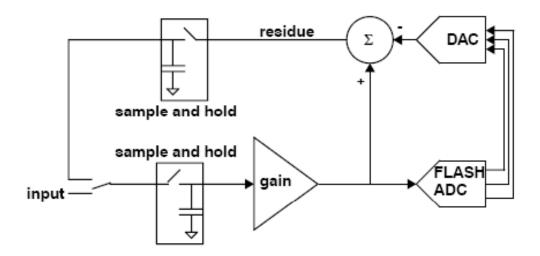

## A 12-bit 3.5V Cyclic ADC

- Objective :

- Design a 12-bit cyclic ADC with 3.5V power sup. based on the buildings blocks of the pipeline ADC but with a lower power supply (5V→ 3.5V)

- Gain 2 accuracy required for a 12-bit ADC is multiplied by 4 compare to a 10-bit ADC

- 10 bits ADC accuracy is 1/1000

- 12 bits ADC accuracy is 1/4000

- Two chips designed to characterize two main elements of 12-bit cyclic ADC

- Comparator (July 06)

- Gain-2 amplifier (July 07)

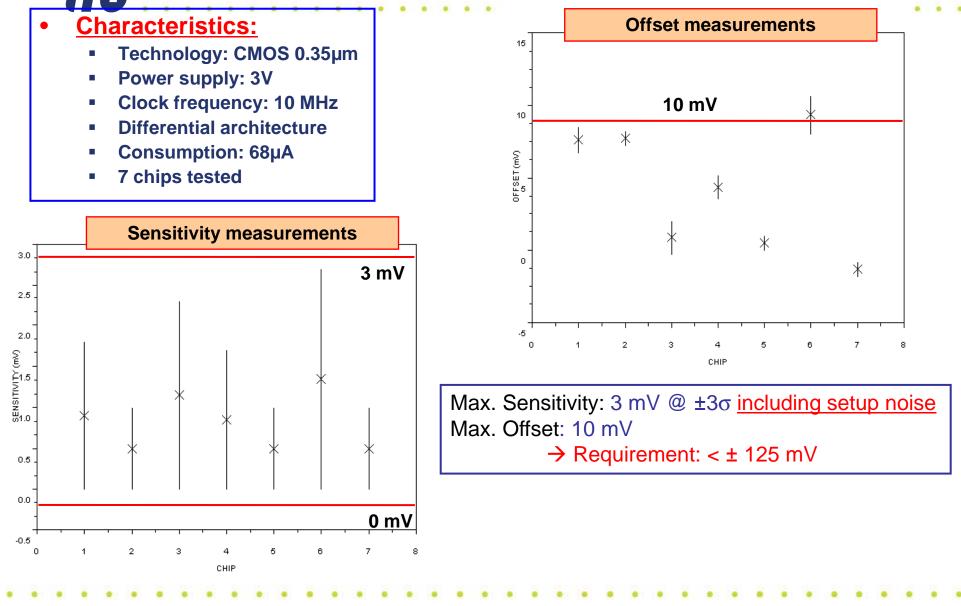

### **Comparator measurements**

### Gain-2 amplifier: preliminary results

#### **Characteristics & performance:**

- Technology: CMOS 0.35µm

- Power supply: 3.5V

- Differential architecture

- Consumption: 2.8 mW

- Gain : 16 k

- Gain Band product: 50 MHz

- Linear, Stable

- Matching of capacitors optimized (precision of gain 2)

06/02/2008

ilc

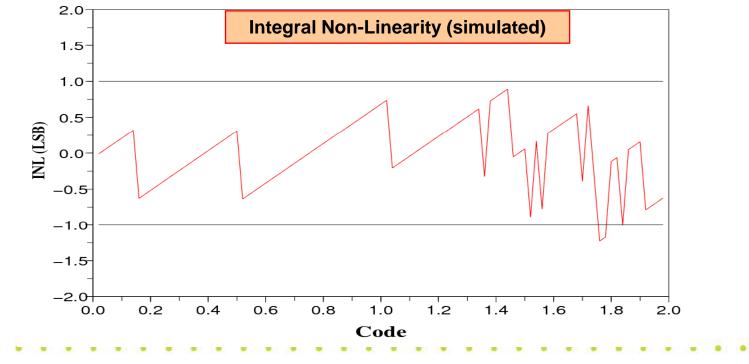

# Simulation of the 12-bit cyclic ADC

- An original architecture:

- One gain-2 amplifier and two comparators required

- Only 6 periods of clock needed to achieve a conversion

- Simulated performance:

- Integral Non-Linearity nearly within ±1 LSB

- Conversion time (clock freq. of 1MHz) : 6 μs

- Power consumption: 3.2 mW

|           | # bits | Precision                                     | Integ. consum.<br>per channel         | Die area            | Status                                                     |

|-----------|--------|-----------------------------------------------|---------------------------------------|---------------------|------------------------------------------------------------|

| Pipeline  | 10     | 10 bits                                       | 0.22 μW (1%)<br>1 ADC/n channels      | 1.4mm <sup>2</sup>  | Tested & publicated                                        |

| Wilkinson | 12     | 12 bits @ low energy<br>10 bits @ high energy | 6 μW (13%)<br>1 ADC/channel           | 0.12mm <sup>2</sup> | in SKIROC<br>Test in<br>progress                           |

| Cyclic    | 12     | 12 bits                                       | <i>≈ 0.5</i> µW (2%)<br>1 ADC/channel | ≈ 0.15 mm²          | in develop <sup>t</sup><br>Building<br>blocks<br>validated |

Our Wilkinson ADC is a candidate for the EUDET VFE chip... IF its performance is confirmed by measurements

Our cyclic ADC, which is an evolution of the pipeline ADC, should be a good candidate to the final chip (accurated, low power, compact...)

$\rightarrow$  Fabrication and test of prototypes foreseen in 2008