### CALICE February 6<sup>th</sup> LPSC Grenoble

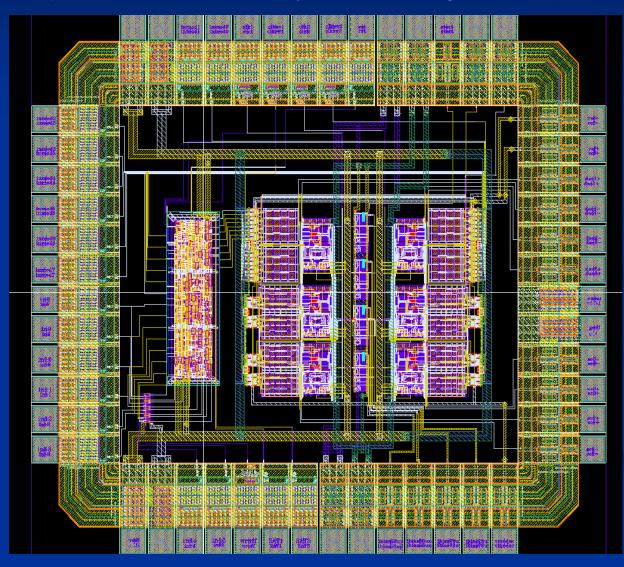

# 16 bits ΣΔ DAC (submitted January 21<sup>st</sup>)

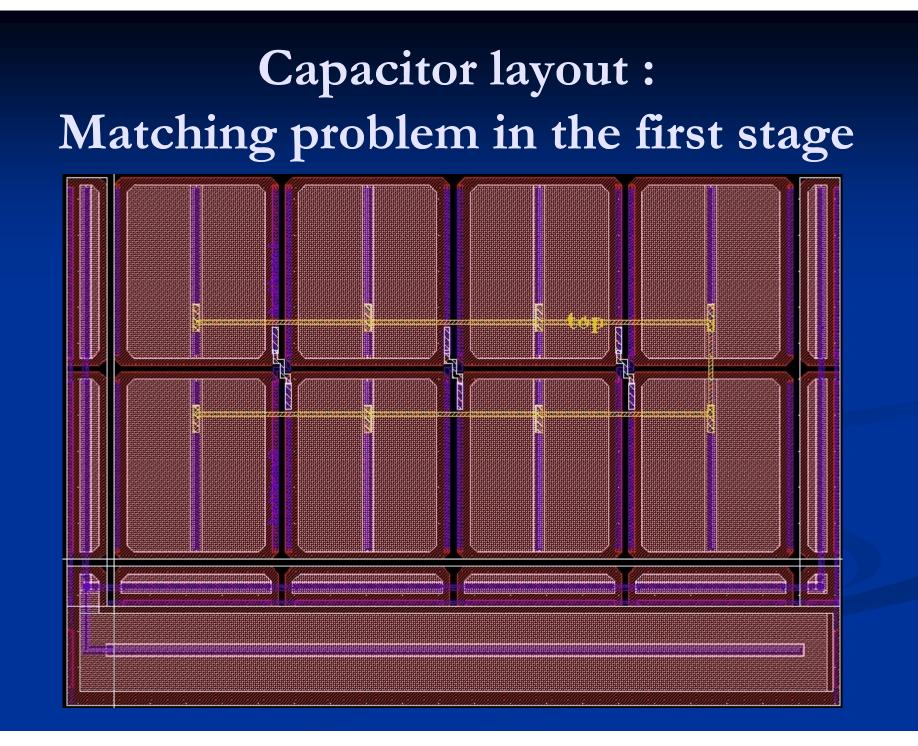

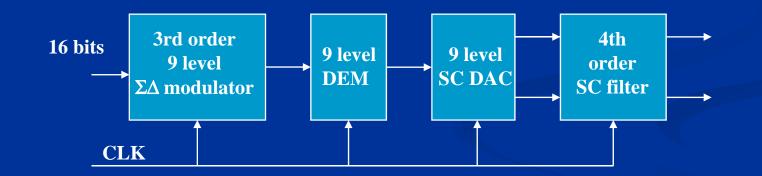

# 16 bits ΣΔ DAC Block diagram

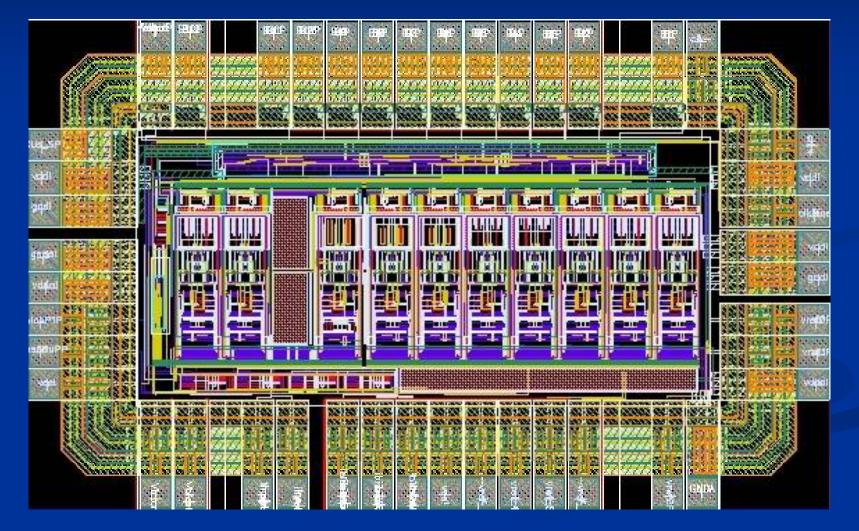

# 12 bits, 30 MHz ADC pipeline

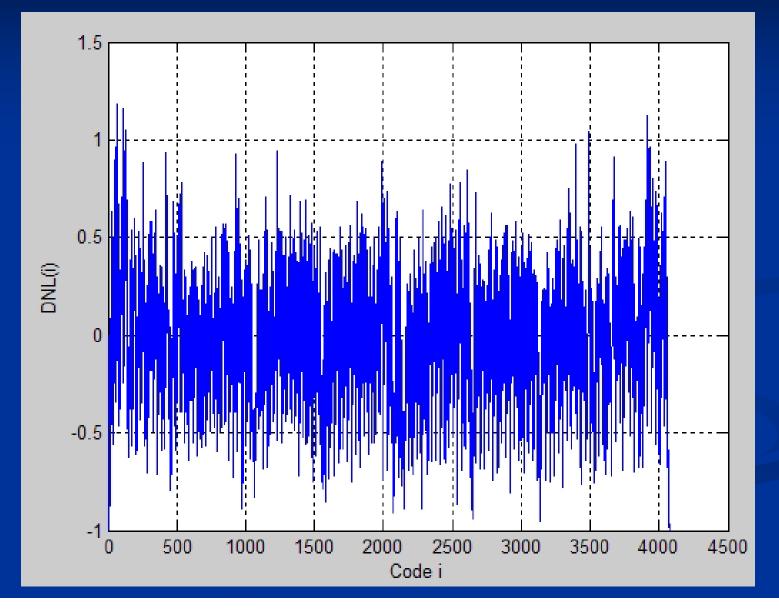

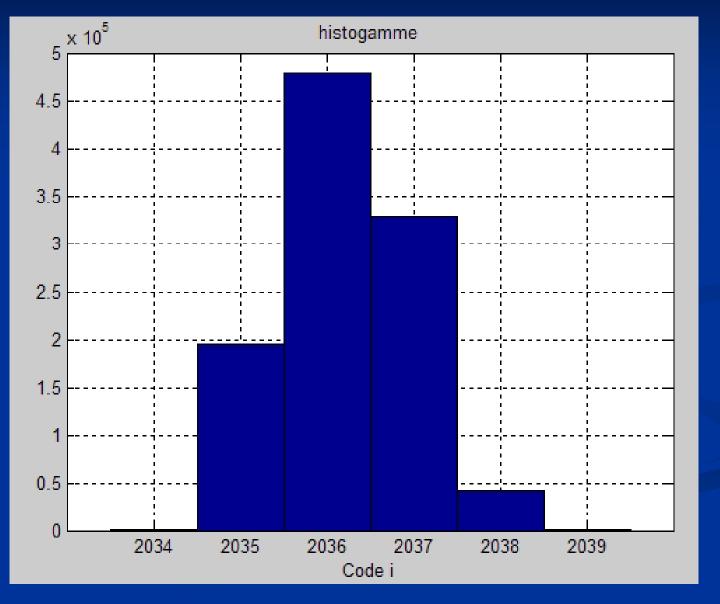

# DNL testing result

## Noise: 0.8 LSB

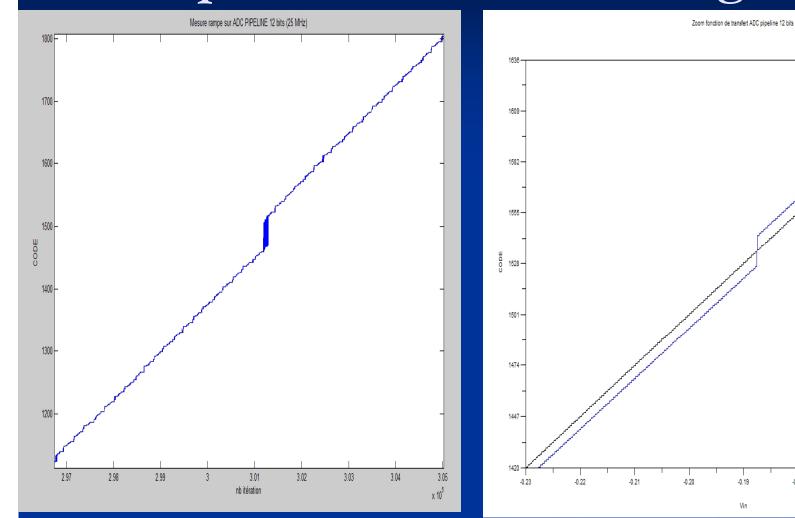

### Ramp simulation and testing results

#### measurement

#### simulation

-0.18

-0.17

-0.16

-0.15