# CALICE Electronics issues

2 June, 2008

Orsay Micro Electronic Group Associated

#### Electronics for technological modules

- Summary of Argonne meeting

- Some issues from London's meeting

- pressing issues :

- Hardroc, Spiroc and SKIROC results and plans [Omega,LPCC]

- ASIC Production issues

- ECAL ASUs and signals distribution [Cambridge, Manchester, LAL, LLR]

- AHCAL HBUs [DESY]

- DHCAL ASUs and DIF [Lyon, LAPP, LLR]

- Power supplies considerations

- 3rd generation R&D [Omega,LPCC,LPSC]

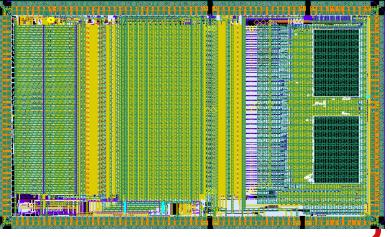

## HARDROC2

- HARDROC1 could go to production directly

- No major bug

- Measurements going on since > 1 year : still some imperfections found

- Main drawback is package size and double row bonding yield

- HaRDROC2 could be prototyped in june 08

- Keep HARDROC1 basic architecture and backward compatibility

- Have 3 very different thresholds

- Move bonding pads to single row

- + many small changes

(gain accuracy, power pulsing...)

– Area : 25 mm2

nega

# HV sparks (ESD)

- ASIC inputs:

- protection PADs (AMS library): robustness up to 2kV HBM (100pF)

- From T2K large µmegas [E. Delagnes], AC coupling necessary for area > 10cm<sup>2</sup>:

- Maximum decoupling capacitor that can be integrated: ≈30pF (50µm x 600 µm ) and Cdet= nF loss of signal

- EXTERNAL CAP=500 pF/ch to ensure protection

- Drawbacks of a decoupling cap: Xtalk, space

- <u>HV sparks robustness for large GEM-like</u> detectors requires dedicated design effort

neaa

HV

1 nF

500p

1M

#### SPIROC2

- SPIROC1 needs one more prototype before production

- 2 major bugs : no probe, no ADC

- Analog part so far OK, can be used to replace FLC\_SiPM

- Autotrigger at ~50-100 fC

- Could be tested with existing detector and DAQ

- Many more measurements to be done : complex chip

- SPIROC2 could be prototyped in june 08

- If no major change

- Possibly SKIROC compatible

- TQFP208 package : 28x28x1.4 mm

mega

## SKIROC2

- SKIROC1 cannot be used for detector

- Digital part outside

- needs one more prototype before production

- Analog part so far OK, can be used to replace FLC\_PHY3

- Many more measurements to be done

- SKIROC2 could be SPIROC2

- Bypass input capacitance

- Possibly limited dynamic range

- But ECAL PCB needs 64 channels

<u> (mega</u>

# **Digital part**

- Digital part validated on hardroc

- VHDL code available

- Still many small changes coming up [see F. Dulucq]

- Many improvements on Slow Control

- Default mode

- Last FF for daisy chain timing requirements

- Reduce PAD number

- Increase reliability:

- Double some drivers

- Possibility to disconnect bus drivers

- Add bypass on critical signals

- Remove "dummy frame" and improve digital operation

- Management of PowerON for digital part

- Start / Stop clocks

- Start / Stop LVDS receivers...

mega

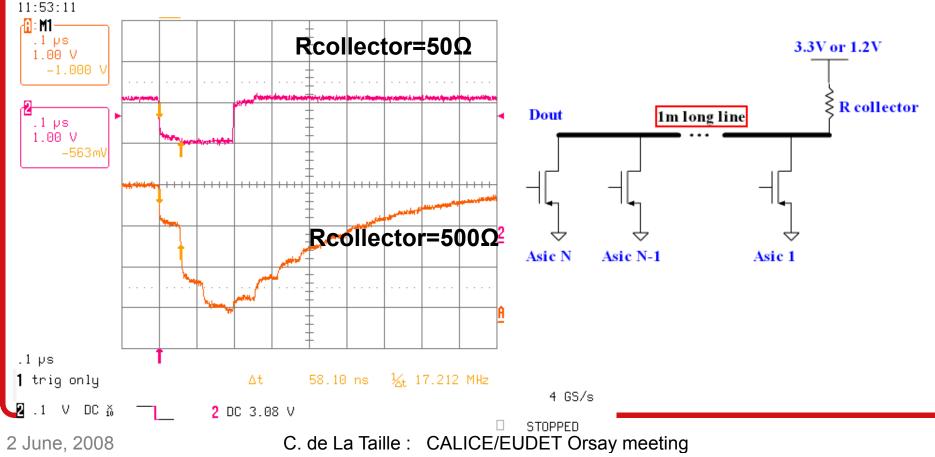

# Open collector signals after 1m long line

- 5 m data line / slab -> 500 pF

- Multiple reflections when unterminated : 1 MHz max

- 50 ohm termination => clean, 10 MHz R/O possible, power dissipation 10 mW/slab in DIF

- Need to change driver transistor size in ASICs

()mega

#### Tentative schedule

- June 08 : submission of HaRDROC2 and SPIROC2

- Sept 08 : chips in hand and for standalone tests

- March 09 : production run with HaRDROC2, SPIROC2 and (challenging) SKIROC2 (64ch)

- June 09 chips available for ASUs

mega

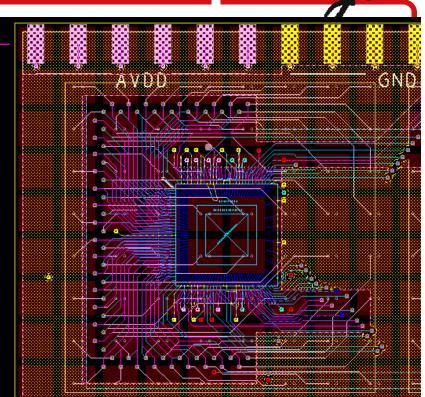

#### PCB developments

- ECAL : ASU prototype

- FEV5 expected soon

- Uses 4 HArdroc chips

- Can test stitching

- Connects to proto DIF

- AHCAL : HBU

- First prototype with Spiroc

DHCAL : m2 prototype boards

For RPCs and µMEGAS : different sizes and connections

#### **DIF** issues

- Common connector specification

- 90 pins

- Thanks to DIF task force

|                       | N pins |

|-----------------------|--------|

| nalog                 | 3      |

| Iser Single Ended     | 22     |

| Controls Single Ended | 5      |

| igital Readout        | 12     |

| ower pulsing controls | 5      |

| VDS signals           | 16     |

| Slow controls signals | 8      |

| OWER pins             | 6      |

|                       |        |

| SND                   | 13     |

|                       |        |

|                       |        |

| BND    1      MUX3_CSn    3      MUX2_CSn    5      MUX1_CSn    7      spare1    9      MUX_ENN    11      MUX_ENN    11      MUX_ENN    11      MUX_WRN    13      spare2    15      an_otaq    17      BND    19      SR_reset    21      nold    23      spare3    25      SR_OUT    31      spare4    29      SR_Ckk    35      SR_Clk    35      SR_clk    35      SND    39      Pwr_analog    41      Yar analog    <             | 1 m   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| MUX2_CSn    5      MUX1_CSn    7      spare1    9      MUX_ENN    11      MUX_WRN    13      spare2    15      an_otaq    17      SND    19      SR_reset    21      apare3    25      SR_IN    27      spare4    29      SR_Ck    35      SR_Ck    35      SR_Ck    35      SND    37      SR_ck    35      SND    44      GND    42      Dout_3    44      GND    50      SrassOUT_4    51      SC_SROUT_5    53                                                                         |       |

| MUX2_CSn    5      MUX1_CSn    7      spare1    9      MUX_ENN    11      MUX_WRN    13      spare2    15      an_otaq    17      SND    19      SR_reset    21      apare3    25      SR_IN    27      spare4    29      SR_Ck    35      SR_Ck    35      SR_Ck    35      SND    37      SR_ck    35      SND    44      GND    42      Dout_3    44      GND    50      SrassOUT_4    51      SC_SROUT_5    53                                                                         |       |

| spare1    9      MUX_ENN    11      MUX_WRN    13      spare2    15      en_otaq    17      BND    19      SR_reset    21      hold    23      SR_reset    21      SR_reset    21      SR_OUT    31      SR_OUT    31      SR_clk    35      SR_clk    35      SR_clk    35      SR_clk    35      SR_clk    35      SR_clk    35      SND    37      TransmitOn_2    43      Vwr_dac    45      Pwr_ss/Pwr_sca    47      SND    52      Start_Readou      Soc_SROUT    59      SC_SROUT    59 <tr< td=""><td></td></tr<> |       |

| MUX_ENN    11      MUX_WRN    13      spare2    15      en_otaq    17      SND    19      SR_reset    21      hold    23      SR_reset    21      bagare3    25      SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_ck    35      SR_ck    35      SR_ck    35      SR_ck    35      SR_ck    35      SND    37      TransmitOn_3    39      Pwr_dac    45      Pwr_digital    53      TransmitOn_1    51      SC_SROUT    59      SC_SROUT_BYPASS    61      SC_select    63      SC_select    63      SC_select    63      SC_select    63      SC_sclak    65      Jser_LVDS_P    67      Trig_Ext_P    69      OVDD    71                                   |       |

| MUX_ENN    11      MUX_WRN    13      spare2    15      en_otaq    17      SND    19      SR_reset    21      hold    23      SR_Roll    22      MUX_A0      Spare3    25      SR_OUT    31      spare5    33      SR_clk    35      SR_clk    35      SR_clk    35      SR_clk    35      SR_clk    35      SND    37      TransmitOn_2    43      Pwr_dac    45      Pwr_digital    53      TransmitOn_1    51      SC_SROUT_SP    61      SC_SROUT_SP    61      SC_SROUT_SP    67      SC_SRIN_B    62                                 |       |

| MUX_WRN    13      spare2    15      en_otaq    17      SND    19      SR_reset    21      nold    23      spare3    25      SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_cik    35      SND    37      fransmitOn_3    39      Pwr_dac    41      Yar analog                 |       |

| an_otaq    17      an_otaq    19      SR_reset    21      an_otad    23      an_otad    24      an_otad    34      Start_con    34      an_otad    34      an_otad    34      an_otad    34      an_otad    35      an_otad    36      an_otad    37                        |       |

| SND    19      SR_reset    21      nold    23      spare3    25      SR_IN    27      spare3    25      SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_CIK    35      SND    37      TransmitOn_3    39      Pwr_dac    41      Yaranalog    41      YaransmitOn_2    43      Pwr_dac    45      Pwr_digital    53      TransmitOn_0    55      SC_SROUT    59      SC_SROUT_BYPASS    61      SC_SROUT_BYPASS    61      SC_SROUT_BYPASS    61      SC_SROUT_SP    67      SC_SROUT_SP    67      SC_SROUT_SP    67      SC_     |       |

| SND    19      SR_reset    21      nold    23      spare3    25      SR_IN    27      spare3    25      SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_cik    35      SND    37      fransmitOn_3    39      Pwr_dac    41      Pwr_dac    45      Pwr_digital    53      SransmitOn_1    51      Se_SROUT    59      SC_SROUT_BYPASS    61      SC_SROUT_BYPASS    61      SC_SROUT_SP    67      Sc_select    63      SC_ckk    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71      72    AVDD                 |       |

| SR_reset    21      nold    23      apare3    25      SR_IN    27      apare4    29      SR_OUT    31      apare5    33      SR_cik    35      SND    37      TransmitOn_3    39      Pwr_dac    41      Pwr_dac    45      Pwr_digital    53      TransmitOn_1    51      Sc_SROUT    59      Sc_SROUT_BYPASS    61      Sc_select    63      Sc_cik    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                               |       |

| anold    23      apare3    25      SR_IN    27      apare4    29      SR_OUT    31      apare5    33      SR_cik    35      SND    37      TransmitOn_3    39      Pwr_dac    41      Pwr_dac    45      Pwr_digital    53      TransmitOn_1    51      Sc_SROUT    59      Sc_SROUT    59      Sc_SROUT_BYPASS    61      Sc_select    63      Sc_cik    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                                                |       |

| SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_clk    35      SND    37      TransmitOn_3    39      Pwr_analog    41      Yar_analog    47      Yar_analog    47      Yar_analog    53      Yar_analog    53 |       |

| SR_IN    27      spare4    29      SR_OUT    31      spare5    33      SR_clk    35      SND    37      TransmitOn_3    39      Pwr_analog    41      Yar_analog    47      Yar_analog    47      Yar_analog    53      Yar_analog    53 |       |

| spare4    29      SR_OUT    31      spare5    33      SR_clk    35      SR_clk    35      SND    37      TransmitOn_3    39      Pwr_analog    41      TransmitOn_2    43      Pwr_dac    45      Pwr_dac    45      Pwr_dac    46      Dout_2    48      Start_Readou    50      Trig_ext    50      Trig_ext    54      Pwr_adc    57      SC_SROUT    59      SC_SROUT_BYPASS    61      SC_select    63      SC_clk    65      Jser_LVDS_P    67      Trig_Ext_P    69      OVDD    71                                                                                                                                                                                                 |       |

| SR_OUT    31      spare5    33      SR_clk    35      SND    37      TransmitOn_3    39      2wr_analog    41      TransmitOn_2    43      2wr_dac    45      2wr_ss/Pwr_sca    47      SND    44      GND    49      2wr_digital    53      TransmitOn_0    55      Ser_SROUT    59      SC_SROUT_BYPASS    61      SC_select    63      SC_clk    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                                                                                                                                                                                                                        |       |

| SR_clk      35        SND      37        TransmitOn_3      39        Pwr_analog      41        TransmitOn_2      43        Pwr_dac      45        Pwr_dac      45        Pwr_ss/Pwr_sca      47        SND      48        Start_Readou        Pwr_dac      45        Pwr_dac      47        SND      49        FransmitOn_1      51        Pwr_digital      53        TransmitOn_0      55        Pwr_adc      57        SC_SROUT      59        SC_SROUT_BYPASS      61        SC_select      63        SC_clk      65        Jser_LVDS_P      67        Frig_Ext_P      69        OVDD      71                                                                                           |       |

| SR_clk      35        SND      37        TransmitOn_3      39        Pwr_analog      41        TransmitOn_2      43        Pwr_dac      45        Pwr_dac      45        Pwr_ss/Pwr_sca      47        SND      48        Start_Readou        Pwr_dac      45        Pwr_dac      47        SND      49        FransmitOn_1      51        Pwr_digital      53        TransmitOn_0      55        Pwr_adc      57        SC_SROUT      59        SC_SROUT_BYPASS      61        SC_select      63        SC_clk      65        Jser_LVDS_P      67        Frig_Ext_P      69        OVDD      71                                                                                           | laqb  |

| SND    37      GND    37      GransmitOn_3    39      Pwr_analog    41      GransmitOn_2    43      Pwr_dac    45      Pwr_dac    45      Pwr_ss/Pwr_sca    47      GND    49      GND    49      FransmitOn_1    51      SVr_digital    53      FransmitOn_0    55      Sc_SROUT    59      Sc_SROUT_BYPASS    61      Sc_select    63      Sc_ckk    65      GSC_SROUT_DP    67      Frig_Ext_P    69      OVDD    71                                                                                                                                                                                                                                                                    |       |

| TransmitOn_3    39      2wr_analog    41      TransmitOn_2    43      2wr_dac    45      2wr_ss/Pwr_sca    47      3ND    49      TransmitOn_1    51      2wr_digital    53      7ransmitOn_0    55      2wr_adc    57      3C_SROUT    59      3C_SROUT_BYPASS    61      3C_select    63      3C_clk    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                                                                                                                                                                                                                                                                  |       |

| Pwr_analog    41      TransmitOn_2    43      Pwr_dac    45      Pwr_ss/Pwr_sca    47      SND    49      TransmitOn_1    51      Pwr_digital    53      TransmitOn_0    55      Pwr_adc    57      SC_SROUT    59      SC_SROUT_BYPASS    61      SC_ckk    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                                                                                                                                                                                                                                                                                                               |       |

| TransmitOn_2    43      Pwr_dac    45      Pwr_ss/Pwr_sca    47      SND    49      TransmitOn_1    51      Pwr_digital    53      TransmitOn_0    55      Pwr_adc    57      SC_SROUT    59      SC_SROUT_BYPASS    61      SC_select    63      SC_clk    65      Jser_LVDS_P    67      Frig_Ext_P    69      OVDD    71                                                                                                                                                                                                                                                                                                                                                                |       |

| Pwr_dac      45      46      Dout_2        Pwr_ss/Pwr_sca      47      48      Start_Readout        GND      49      50      Trig_ext        GND      49      52      Start_Readout        Start_Readout      53      54      Dout_1        Pwr_digital      53      56      GND        Pwr_adc      57      58      Dout_0        SC_SROUT      59      60      SC_SRIN_BY        SC_SROUT_BYPASS      61      62      SC_SRIN_BY        SC_select      63      64      SC_reset        66      SC load      68      User_LVDS        Strig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                   |       |

| Pwr_ss/Pwr_sca      47        GND      49        So      Trig_ext        Sever_digital      53        FransmitOn_0      55        Sec_SROUT      59        SC_SROUT_BYPASS      61        SC_select      63        GC_clk      65        Jser_LVDS_P      67        Frig_Ext_P      69        OVDD      71                                                                                                                                                                                   |       |

| SND      49      50      Trig_ext        TransmitOn_1      51      52      Start_Readou        Swr_digital      53      54      Dout_1        TransmitOn_0      55      56      GND        Swr_adc      57      58      Dout_0        SC_SROUT      59      60      SC_SRIN_BY        SC_SROUT_BYPASS      61      62      SC_SRIN        SC_select      63      64      SC_reset        66      SC load      68      User_LVDS        Jser_LVDS_P      67      68      User_LVDS        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                  | ut    |

| TransmitOn_1      51      52      Start_Readou        Pwr_digital      53      54      Dout_1        TransmitOn_0      55      56      GND        Pwr_adc      57      58      Dout_0        SC_SROUT      59      60      SC_SRIN_B        SC_SROUT_BYPASS      61      62      SC_SRIN        SC_select      63      64      SC_reset        66      SC load      68      User_LVDS        Jser_LVDS_P      67      68      User_LVDS        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                            |       |

| Pwr_digital      53      54      Dout_1        TransmitOn_0      55      56      GND        Pwr_adc      57      58      Dout_0        SC_SROUT      59      60      SC_SRIN_BY        SC_SROUT_BYPASS      61      62      SC_SRIN        SC_select      63      64      SC_reset        SC_clk      65      66      SC load        Jser_LVDS_P      67      68      User_LVDS        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                    |       |

| Sc_sROUT      55      56      GND        Sc_sROUT      57      58      Dout_0        Sc_sROUT      59      60      SC_SRIN_BY        Sc_select      63      64      SC_reset        Sc_clk      65      66      SC load        Jser_LVDS_P      67      68      User_LVDS        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                          |       |

| Sever_adc      57      58      Dout_0        SC_SROUT      59      60      SC_SRIN_BY        SC_SROUT_BYPASS      61      62      SC_SRIN        SC_select      63      64      SC_reset        SC_clk      65      66      SC load        Jser_LVDS_P      67      68      User_LVDS        Frig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                              |       |

| SC_SROUT_BYPASS      61      62      SC_SRIN        SC_select      63      64      SC_reset        SC_clk      65      66      SC_load        Jser_LVDS_P      67      68      User_LVDS_        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| SC_select      63      64      SC_reset        SC_clk      65      66      SC_load        Jser_LVDS_P      67      68      User_LVDS_        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (PASS |

| SC_select      63      64      SC_reset        SC_clk      65      66      SC_load        Jser_LVDS_P      67      68      User_LVDS_        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| SC_clk      65      66      SC_load        Jser_LVDS_P      67      68      User_LVDS        Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Trig_Ext_P      69      70      Trig_Ext_N        OVDD      71      72      AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | N     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| Clk_5MHz_0_P 73 74 Clk_5MHz_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | N     |

| Clk_5MHz_1_P 75 76 Clk_5MHz_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N     |

| GND 77 78 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| Clk_40MHz_0_P 79 80 Clk_40MHz_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0_N   |

| Clk_40MHz_1_P 81 82 Clk_40MHz_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1_N   |

| 0VDD 83 84 AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| Raz_Chn_P 85 86 Raz_Chn_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| /al_Evt_P 87 88 Val_Evt_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| AVDD 89 90 AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

90

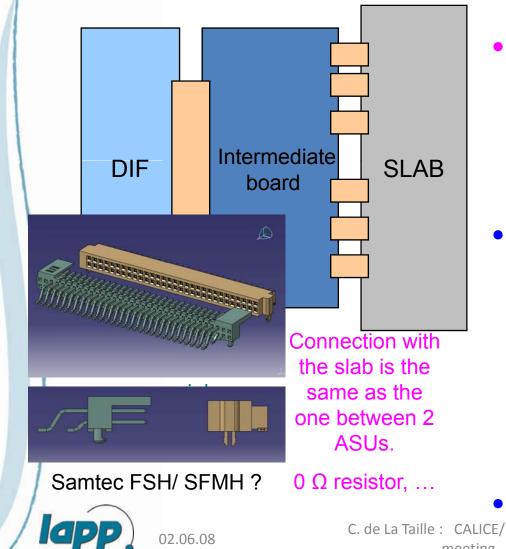

# Interface with the SLAB

- Use of a small

intermediate board,

which is specific to the

FE ASIC and ASU.

- The DIF can be used :

- Whatever the FE ASIC.

- Whatever the slab (RPC, uM)

- Whatever the slab to slab connection.

• 1<sup>rst</sup> ASU is the same as C. de La Taille : CALICE/EUDET Orsay meeting the others. 12

- A very critical issue !!!

- Power supplies won't be dimensionned for continuous operation, but for 1/100 of the load.

- Need local storage (capacitors, even a battery!) on power board and regulators to accomodate large voltage swing

- Simple calculation (ECAL)

- Slab = 24 000 channels

- 1 mA/channel unpulsed => 24 A/slab

- With a <u>24 000µF</u> capacitor <u>dV/dt = 1V/ms => acceptable</u>

#### Done and to do list

<u> Mega</u>

- DONE

- Second generation ASICs prototypes

- Auto-trigger

- Daisy-chain readout

# • TO BE DONE :

- PCB stitching (in progress)

- Tests of bonding chip on board for ECAL (in progress)

- DIF prototypes (in progress)

- Tests of power budget with existing chips and boards

- Tests of power pulsing with Imad's boards

- Integration issues (in progress)

- Design of Power distribution (no one' s looking)

- HV distribution and robustness

- Testbeam with 2<sup>nd</sup> generation detectors

- MEASUREMENTS, MEASUREMENTS, MEASUREMENTS