### EUDET module - Status AHCAL

Mathias Reinecke

for the AHCAL developers

1

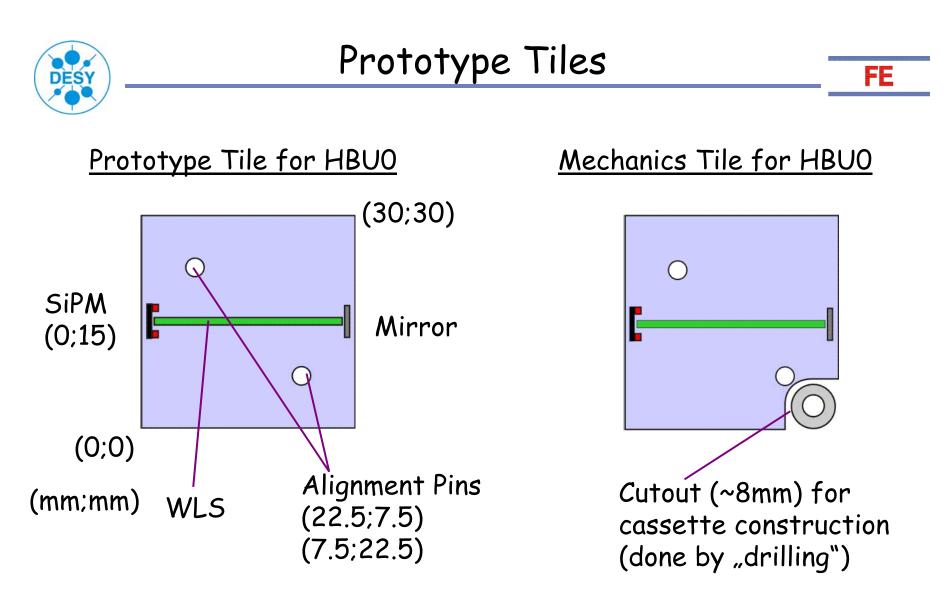

100-150 prototype tiles (structures machined, not moulded) expected end of June.

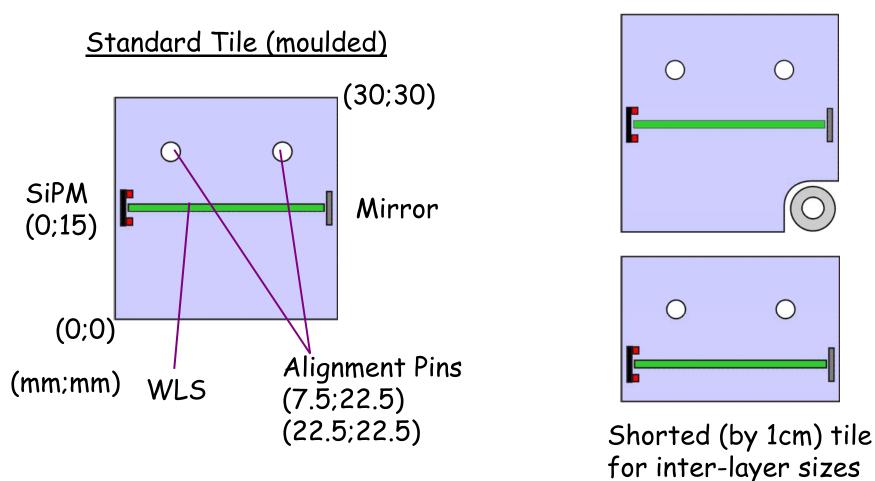

# Tiles for EUDET module

Time schedule for moulded tiles not completely clear (end of 2008?).

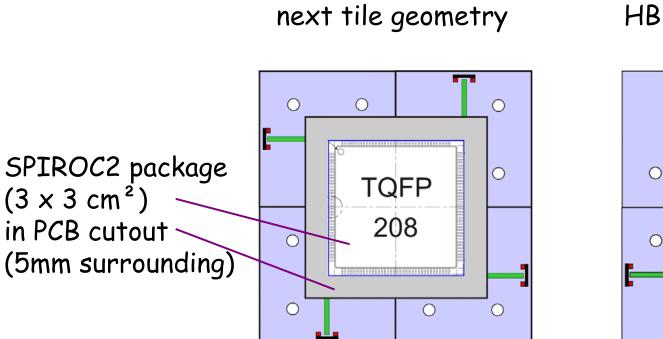

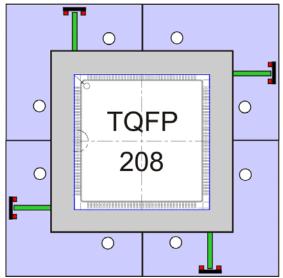

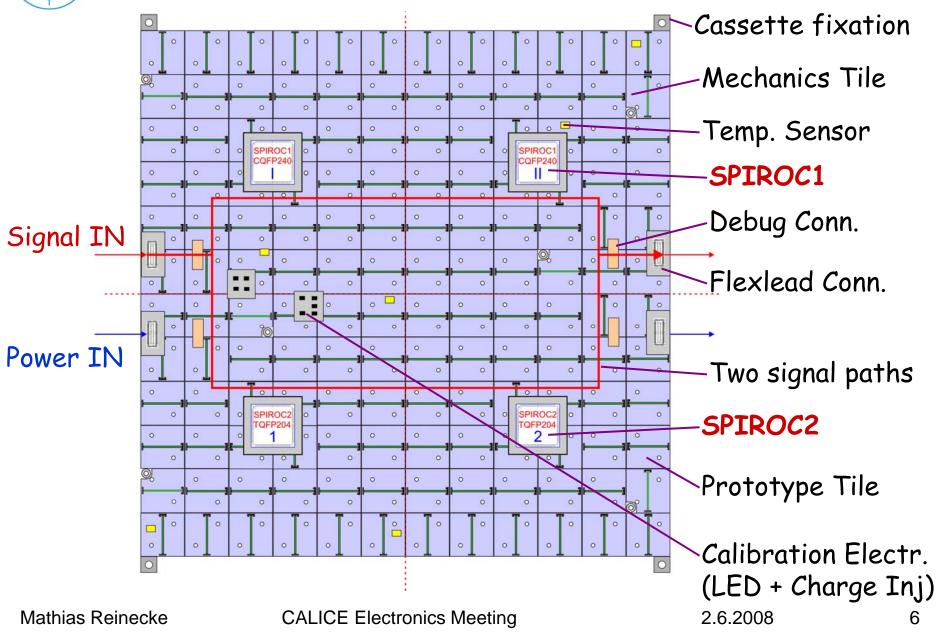

SPIROC on HBU PCB cannot be placed above SiPM and alignment pins of the tiles (=> Tile grouping)

HBUO, tile prototypes

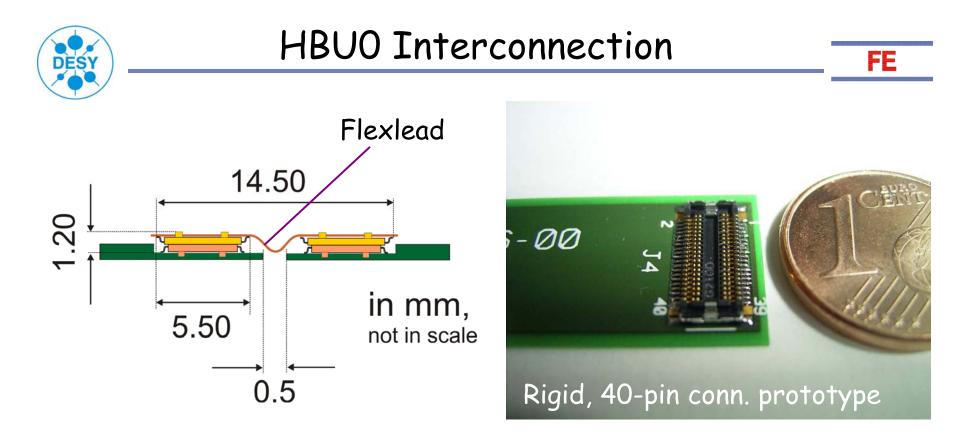

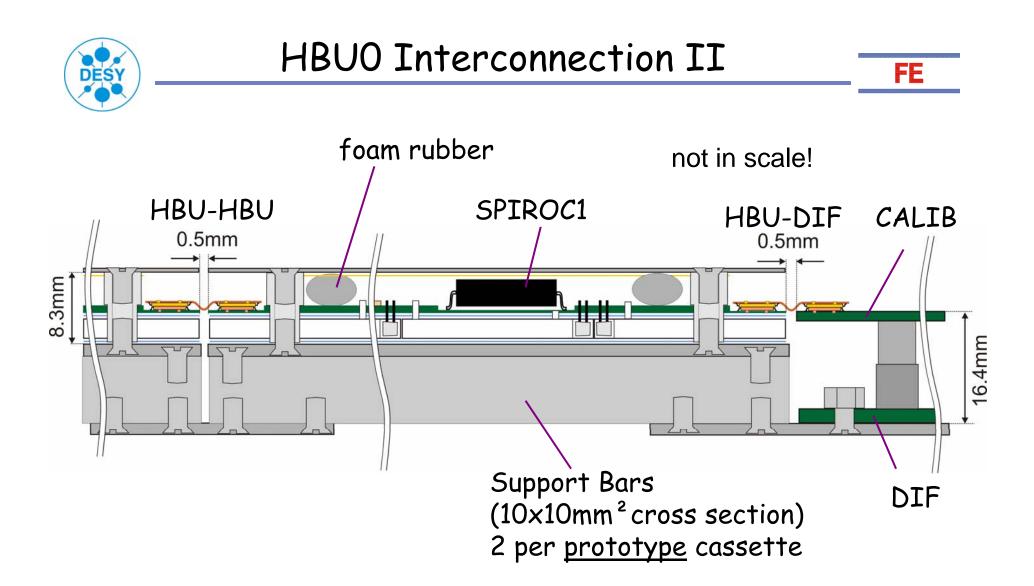

Flexlead: Rigid below connectors, 4 layers, flexible (polyimide) in between, 2 layers 80-pin connectors

Bended flexlead allows HBU-HBU displacement of ±100µm. Concern: Bending forces (tension) might disconnect one connector. Expected cost relation flexlead/connector: ~1.5

Bended flexlead allows HBU-HBU displacement of  $\pm 100 \mu m$ .

CALICE Electronics Meeting

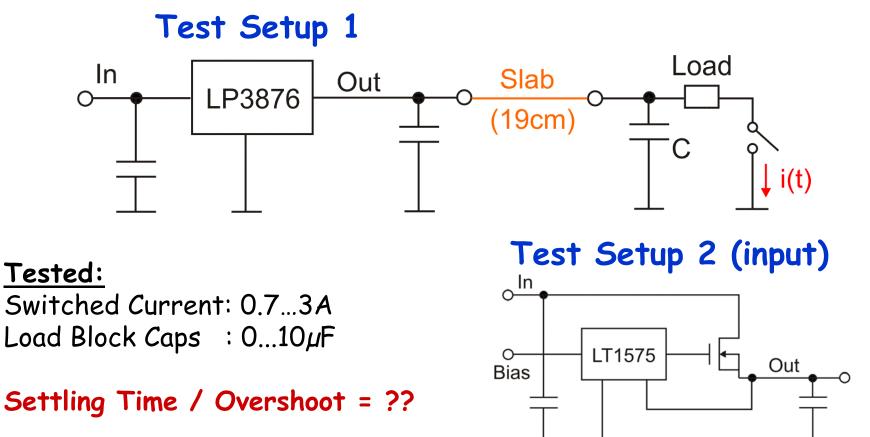

Detector electronics (Load) is switched between "off" (no current) and "on" (full current) with 1% duty cycle. => Oscillations on 2.20m-long power-ground system?

CALICE Electronics Meeting

2.6.2008

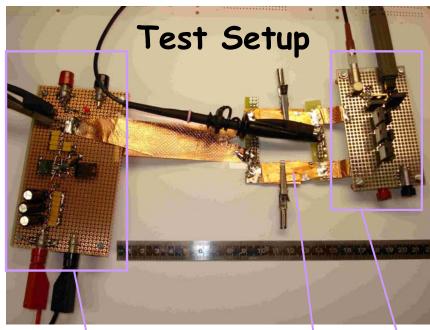

### Power cycling test setup

oln Out Bias ↓ LT1575 ↓ Out ↓ Out ↓ Slab ↓ Load ↓ Coad ↓ (19cm) ↓ i(t)

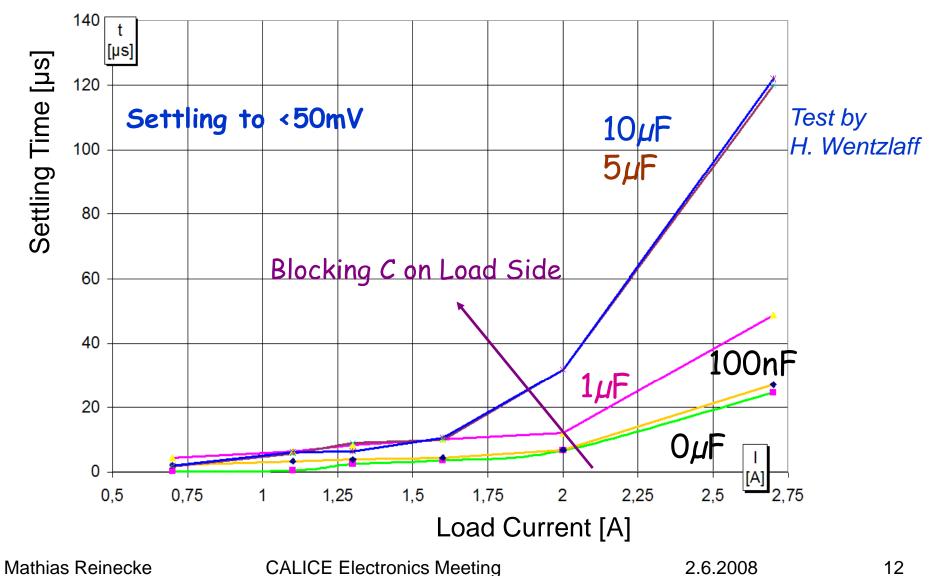

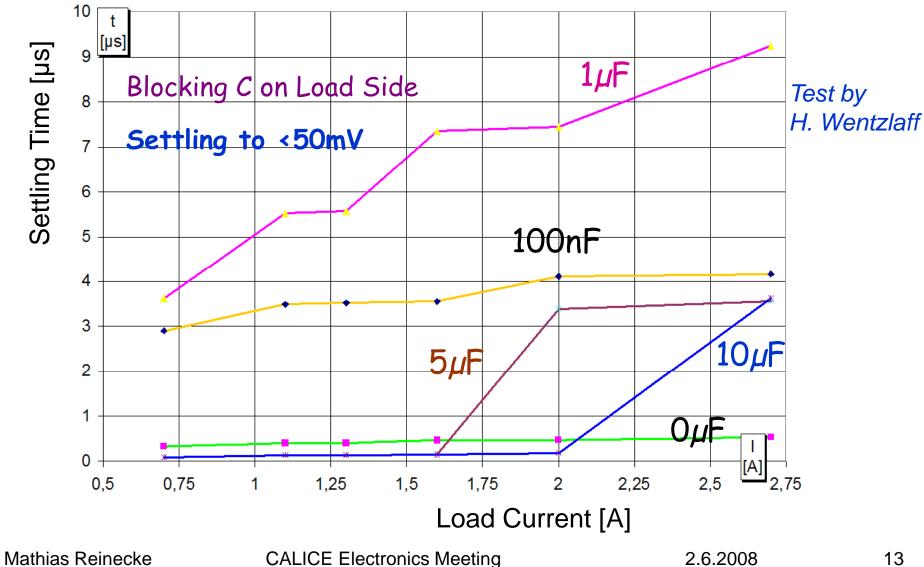

<u>Settling time (Load side):</u> Voltage within 50mV of final value. Aim: reasonable values for efficient power cycling (< 50µs)

FE

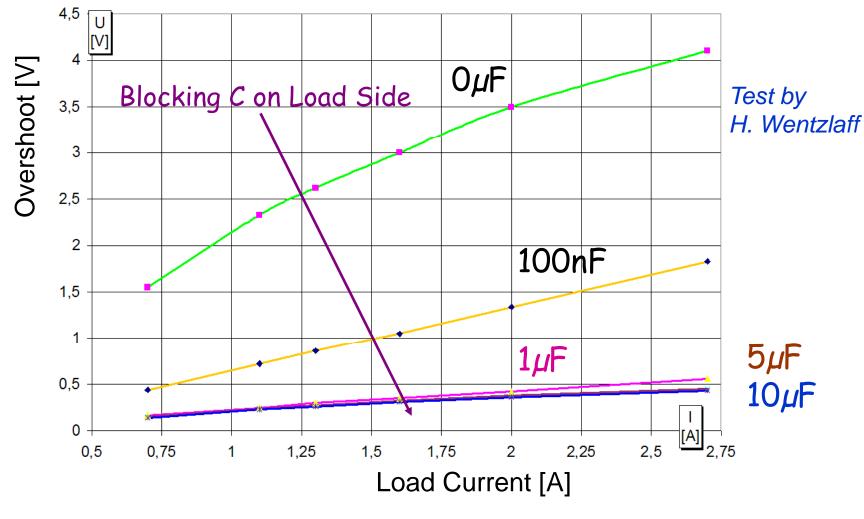

<u>Overshoot</u> shown here for switch-off case (worst-case). Aim: Protection of devices, stable register settings.

Later: Stability test for 2.20m slabs

Typical results for overshoot (loadside), similar for both setups. Overshoot on regulator side: <150mV.

**CALICE Electronics Meeting**

2.6.2008

Typical results for settling time (loadside), setup 1 (LP3876)

Typical results for settling time (loadside), setup 2 (LT1575)

Overshoot, settling-time good on regulator side.

Setup 2 (with transistor): better settling time (factor 10), in the order of  $5..10 \mu$ s.

Overshoot is still about 0.2-0.5V (~150ns spikes) for large blocking caps on load side. Trade-off settling time - overshoot.

Dependency on load-switch transition (5-10ns now)?

Influence of the 2.20m-long slab is analyzed now.

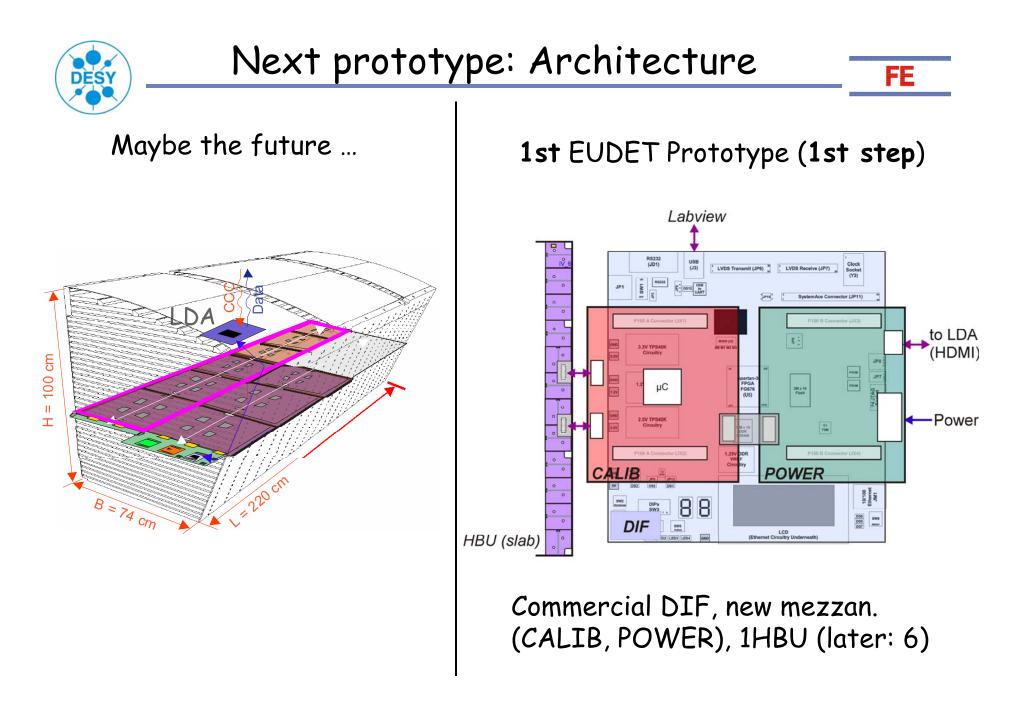

#### DIF (AHCAL):

-Two commercial FPGA boards have arrived.

- -VHDL development should start now.

- => DIF common block implementation needs closer coordination. Maybe starting with the basics (=>timeline?)?: Fixing of timing specs for DIF-ASIC's communication, VHDL block architecture, clock speed of DIF FPGA, LDA-DIF data rate and frame size (or start with USB?).

#### CALIB (LED system and charge-injection)

-Module's duties fixed, schematic almost finished.

- -Layout generation when we fix HBU interface (and design).

- -Microcontroller programming starts now (SPI to DIF, LVDS)

#### POWER (supply of AHCAL electronics)

-Components and architecture fixed in principal, but: -Regulator setup has to be checked for 2.20m slabs

#### HBUO (defines timelines for all other parts)

Schematic needs information about SPIROC2 and tiles.

Initial setup only has 2 HBUOs (no full slab test).

Prototype cassette design waiting (flexlead impl., tile size)

SPIROC1 and SPIROC2 in independent signal chains.

Latest results from Wuppertal LED and SPIROC digital part tests should go into design.

## Timeline (Rev. 1)

| FE AHCAL Timeline          | 2008     |          |                                          |               |       |           |            | 2009    |         |           |          |          |

|----------------------------|----------|----------|------------------------------------------|---------------|-------|-----------|------------|---------|---------|-----------|----------|----------|

| Month                      | Mar/Apr  | May/June | July/Aug                                 | Sept          | Oct   | Νον       | Dec        | Jan/Feb | Mar/Apr | May/June  | July/Aug | Sept/Oct |

| Task                       |          |          |                                          |               |       | Milestone |            |         |         | Milestone |          |          |

|                            |          |          |                                          |               |       |           | I<br>I     |         |         |           |          |          |

| Scint. Tiles               |          |          |                                          |               |       |           |            |         |         |           |          |          |

| Definition of architecture |          | _        |                                          | Moulded Tiles | 5     |           | Dimensions |         |         |           |          |          |

| Production                 |          |          |                                          |               |       |           |            |         |         |           |          |          |

| SPIROC                     |          | SPIROC2  |                                          | SPIROC3       |       |           | Pinout     |         |         |           |          |          |

| Hcal Base Unit (HBU)       |          |          |                                          |               |       |           |            |         |         |           |          |          |

| Circuit Design/Layout      |          |          |                                          |               |       |           | 1          |         |         |           |          |          |

| PCB Production/Assembly    |          |          | 20-00-00-00-00-00-00-00-00-00-00-00-00-0 |               |       | 8         |            |         |         |           |          |          |

| Detector Interface (DIF)   |          |          |                                          |               |       |           | 1          |         |         |           |          |          |

| Common Block Firmware      |          |          |                                          |               |       |           |            |         |         |           |          |          |

| AHCAL Block Firmware       |          |          |                                          |               |       |           |            |         |         |           |          |          |

| Circuit Design/Layout      |          |          |                                          |               |       |           |            |         |         |           |          |          |

| PCB Production/Assembly    |          |          |                                          |               |       |           | <br>       |         |         |           |          |          |

| CALIB, POWER               |          |          |                                          |               | ***** |           |            |         |         |           |          |          |

| Circuit Design/Layout      |          |          |                                          |               |       |           |            |         | ł       |           |          |          |

| PCB Production/Assembly    |          |          |                                          |               |       |           |            |         |         |           |          |          |

| System Tests               |          |          |                                          |               |       |           |            |         |         | ****      | ***      |          |

| DAQ Software, LDA          |          |          |                                          |               |       | 1         |            |         |         |           |          |          |

| Component Ordering         |          |          |                                          |               |       |           |            |         |         |           |          |          |

| Prototype                  |          |          |                                          |               |       |           | 1          |         |         |           |          |          |

| EUDET Mod. (Final)         | 28.05.08 |          |                                          |               |       | [         |            |         |         |           |          |          |

#### Milestone shifted now by 1 month to Nov. 08. Full slab not available before mid 2009.

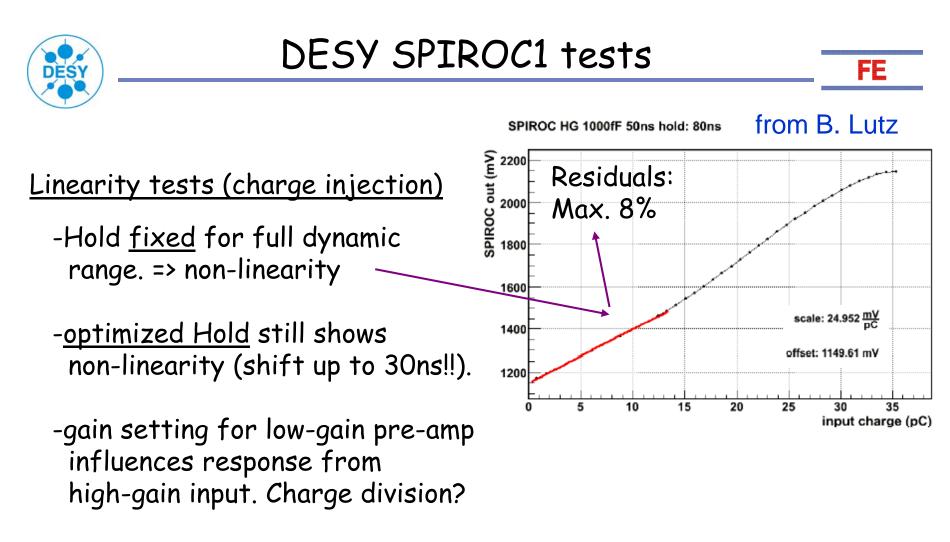

## DESY SPIROC1 tests

Tests and all the work done by B. Lutz, R. Fabbri, Wei Shen

What is the optimum Hold position (conc. response  $\Leftrightarrow$  linearity)?

Autotrigger tests (ongoing):

-Single-photon peak spectrum / MIP signals (radiactive source)

-Jitter and delay tests of auto-trigger: "large signals trigger faster than small signals".

<u>Digital Part tests (pending):</u>

-Probe-register / ADC ramp problems. Is the second testboard with external ramp available? Results important for **DIF** (and HBU) setup!

- -AHCAL techn. prototype (TP) does not cover a full slab, but ~150 channels (2 HBUOs, tile-prototypes).

- -Eudet module (detector layer) requires HBU redesign (mid 2009).

- -timeline for TP is defined by HBUO (input SPIROC2, tile geometry).

- -DIF VHDL programming and DIF hardware interface to detector needs closer coordination (ECAL, DHCAL, AHCAL) soon. (=> hardware round-table meeting?)