#### **Electronics Integration - Status**

Mathias Reinecke

for the AHCAL developers

AHCAL Main Meeting

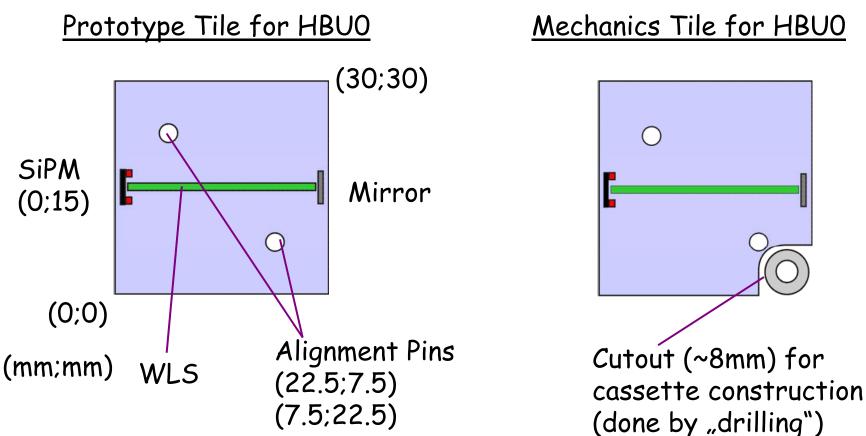

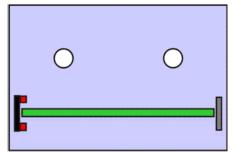

Mechanics Tile for HBUO

100-150 prototype tiles (structures machined, not moulded) expected very soon.

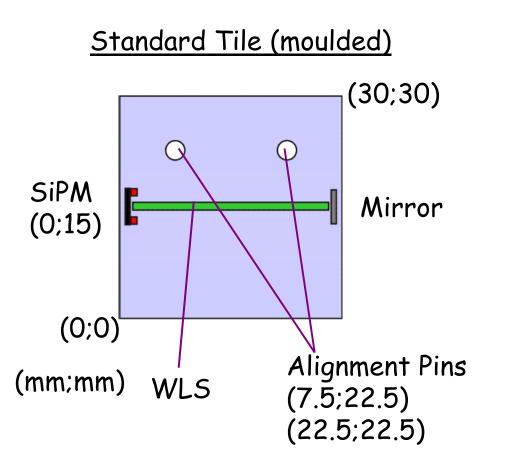

# Tiles for EUDET module

Shorted (by 1cm) tile for inter-layer sizes

Time schedule for moulded tiles not completely clear (end of 2008?).

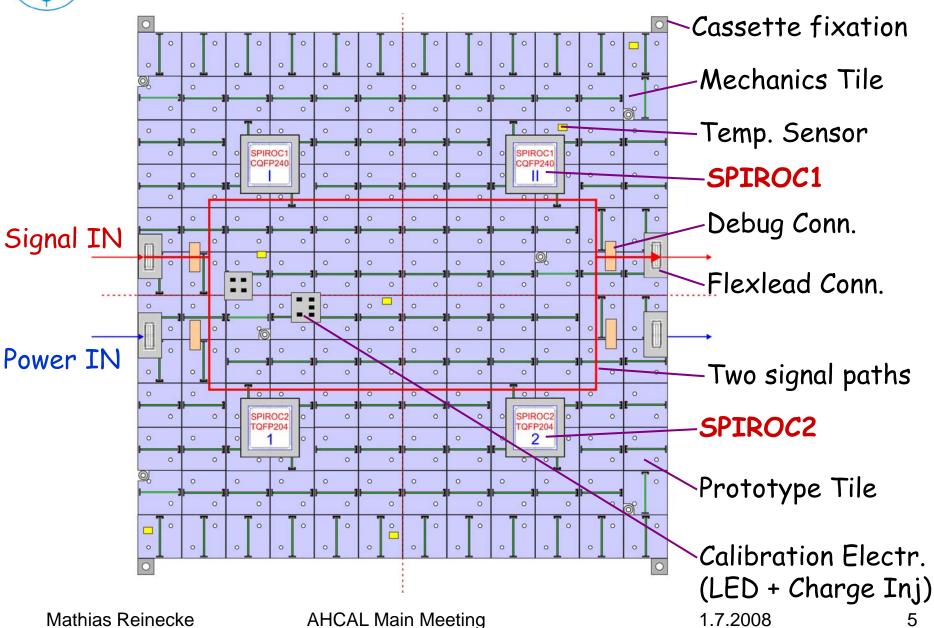

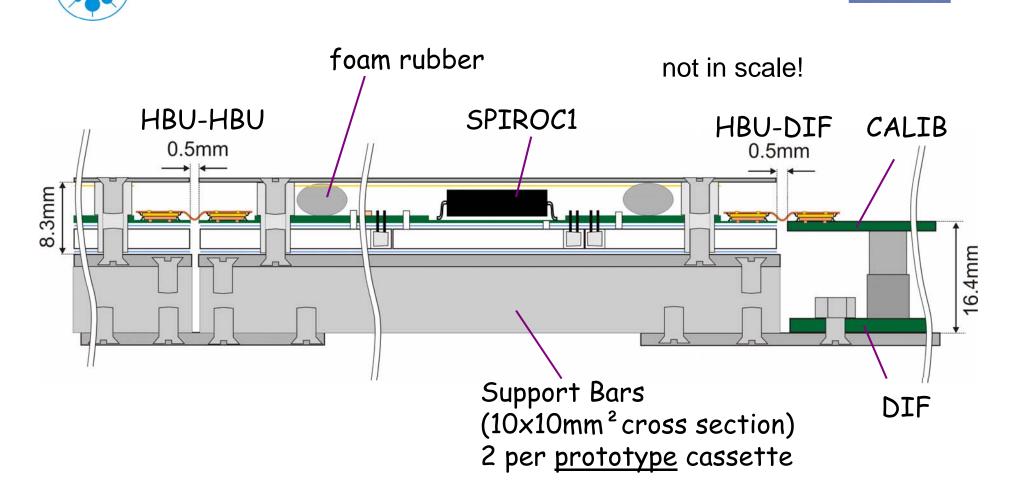

# **HBUO** Interconnection

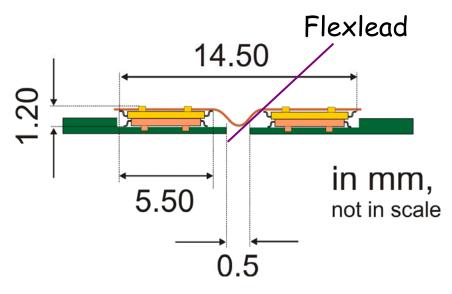

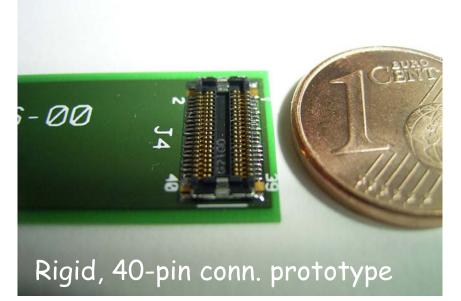

Flexlead: Rigid below connectors, 4 layers, flexible (polyimide) in between, 2 layers 80-pin connectors

Bended flexlead allows HBU-HBU displacement of ±100µm. Concern: Bending forces (tension) might disconnect one connector. Expected cost relation flexlead/connector: ~1.5 Under investigation: Flexleads without connectors (IR soldering) (M. Goodrick et al., Cambridge)

## HBUO Interconnection II

Bended flexlead allows HBU-HBU displacement of  $\pm 100 \mu m$ .

Mathias Reinecke

DESY

AHCAL Main Meeting

7

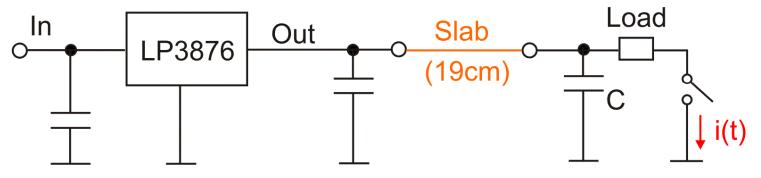

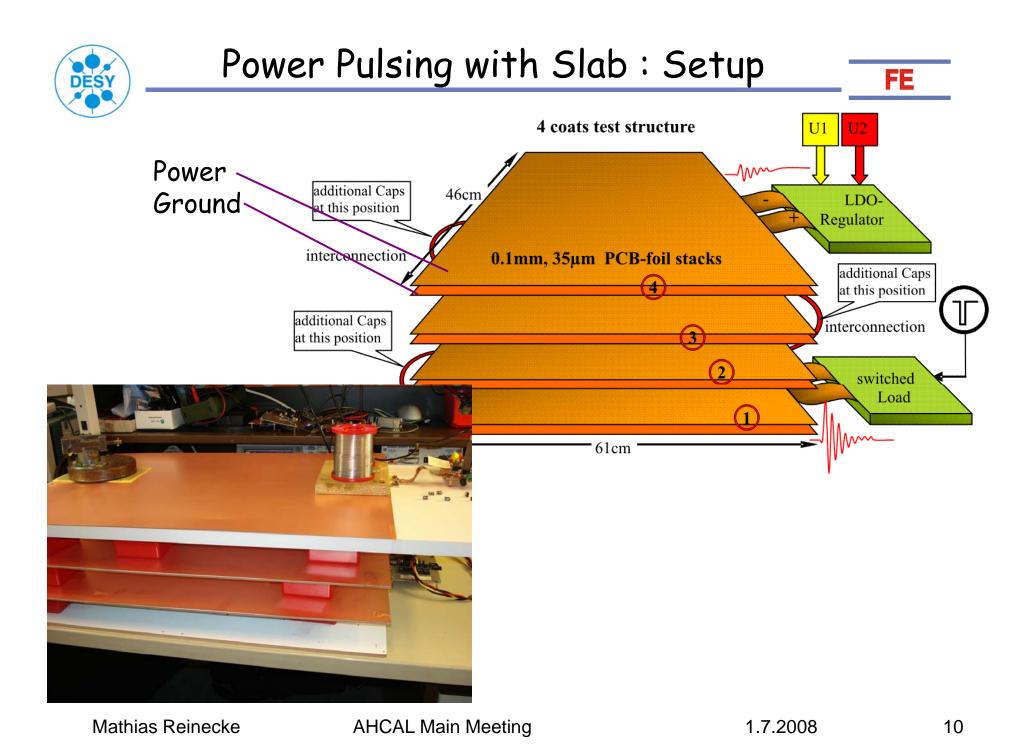

Detector electronics (Load) is switched between "off" (no current) and "on" (full current) with 1% duty cycle.

=> Oscillations on 2.20m-long power-ground system?

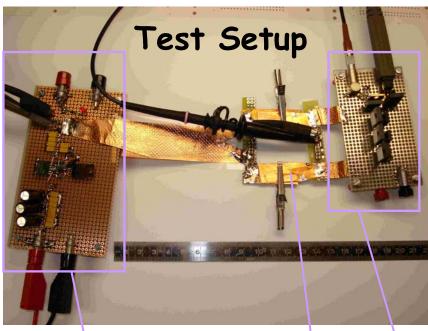

### Tested:

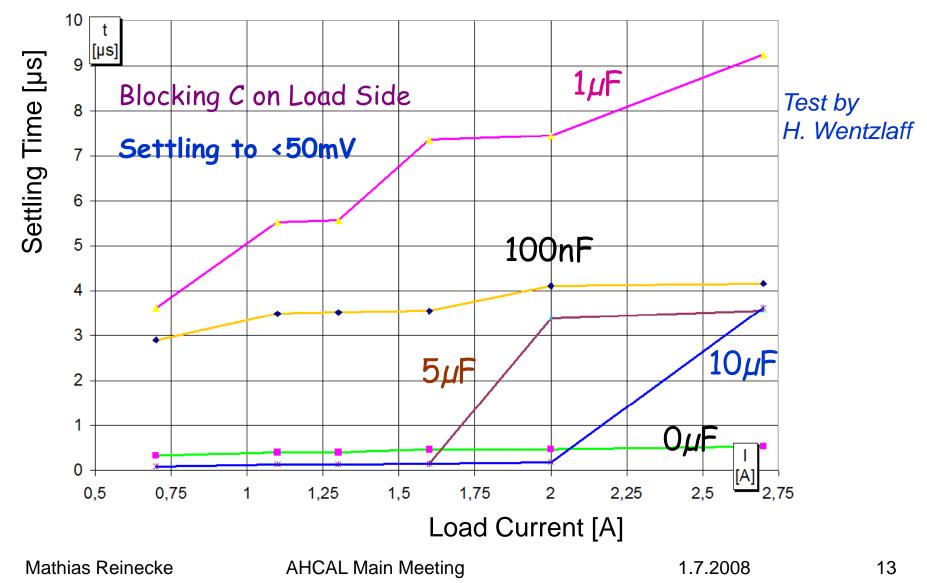

Switched Current: 0.7...3A Load Block Caps : 0...10µF

Settling Time / Overshoot = ??

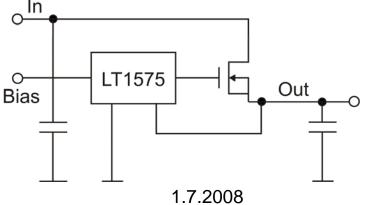

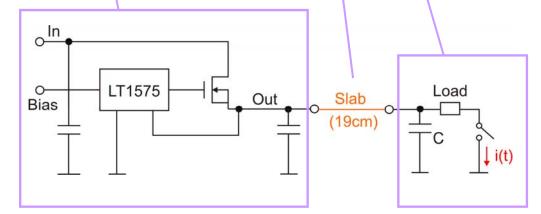

## Test Setup 2 (input)

# Power cycling test setup

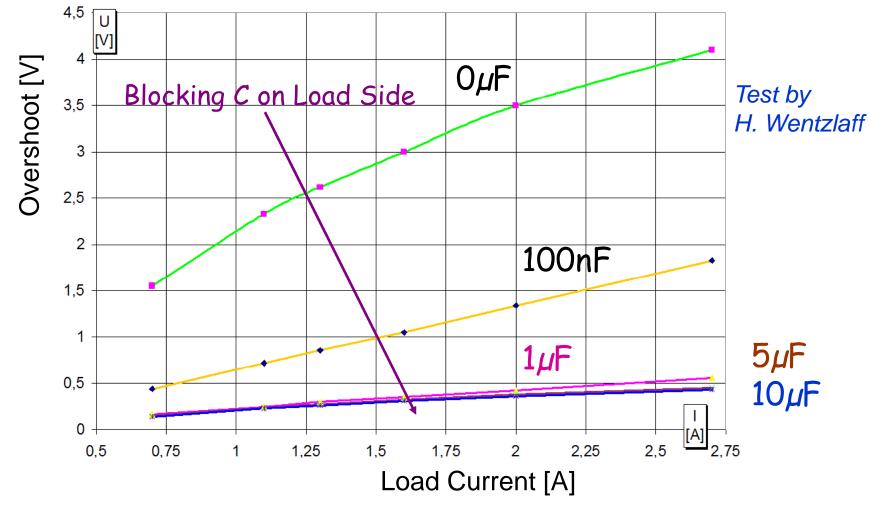

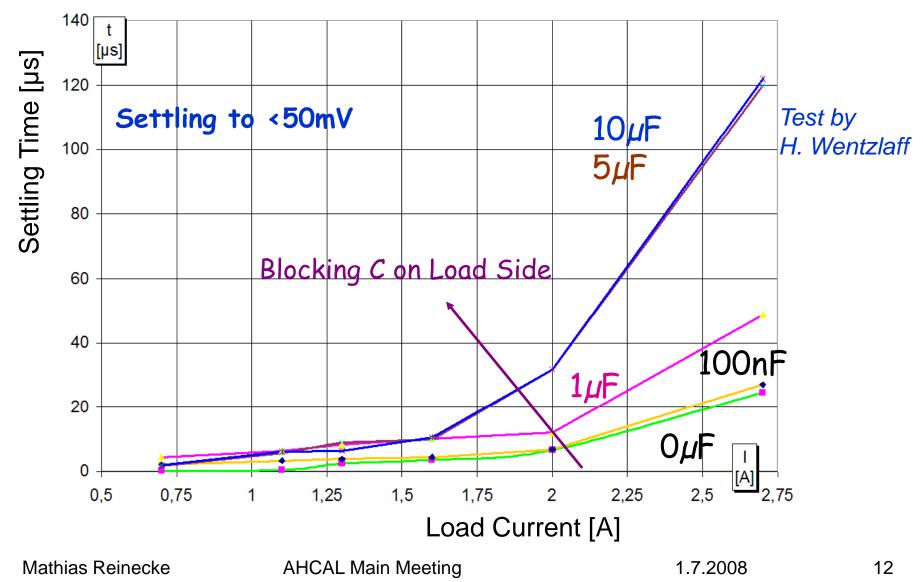

<u>Settling time (Load side):</u> Voltage within 50mV of final value. Aim: reasonable values for efficient power cycling (< 50µs)

FE

<u>Overshoot</u> shown here for switch-off case (worst-case). Aim: Protection of devices, stable register settings.

Later: Stability test for 2.20m slabs

Typical results for overshoot (loadside), similar for both setups. Overshoot on regulator side: <150mV.

Typical results for settling time (loadside), setup 1 (LP3876)

Typical results for settling time (loadside), setup 2 (LT1575)

Overshoot, settling-time good on regulator side.

Setup 2 (with transistor): better settling time (factor 10), in the order of  $5..10\mu$ s.

Overshoot is still about 0.2-0.5V (~150ns spikes) for large blocking caps on load side. Trade-off settling time - overshoot.

Dependency on load-switch transition (5-10ns now)?

Influence of the 2.20m-long slab seems to be small (analysis ongoing)

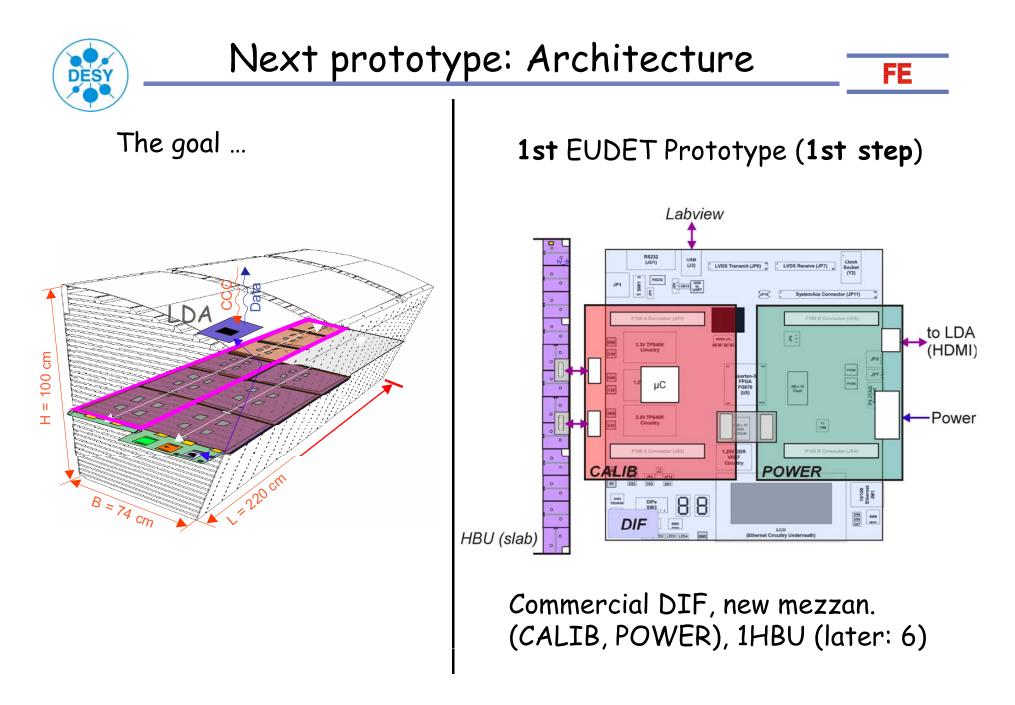

#### DIF (AHCAL):

-Two commercial FPGA boards have arrived.

-VHDL development should starts now

#### POWER (supply of AHCAL electronics):

-Components and architecture fixed in principal, but: -Regulator setup has to be checked for 2.20m slabs

HBUO (defines timelines for all other parts):

-Schematic needs information about SPIROC2 and tiles. -Initial setup only has 2 HBUOs (no full slab test). -SPIROC1 and SPIROC2 in independent signal chains.

#### CALIB (2 LED systems (Prague, Wuppertal) and charge-injection):

-Module's duties fixed, schematic almost finished.

-Layout generation when we fix HBU interface (and design).

-Microcontroller programming starts now (SPI to DIF, LVDS)

| FE AHCAL Timeline          | 2008     |          |                                           |               |     |           |            | 2009    |          |           |          |          |

|----------------------------|----------|----------|-------------------------------------------|---------------|-----|-----------|------------|---------|----------|-----------|----------|----------|

| Month                      | Mar/Apr  | May/June | July/Aug                                  | Sept          | Oct | Nov       | Dec        | Jan/Feb | Mar/Apr  | May/June  | July/Aug | Sept/Oct |

| Task                       |          |          |                                           |               |     | Milestone |            |         |          | Milestone |          |          |

|                            |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Scint. Tiles               |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Definition of architecture |          | _        |                                           | Moulded Tiles | 5   |           | Dimensions |         |          |           |          |          |

| Production                 |          |          |                                           |               |     |           |            |         |          |           |          |          |

| SPIROC                     |          | SPIROC2  |                                           | SPIROC3       |     |           | Pinout     |         |          |           |          |          |

| Hcal Base Unit (HBU)       |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Circuit Design/Layout      |          |          |                                           |               |     |           | 1          |         | <i>.</i> |           |          |          |

| PCB Production/Assembly    |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Detector Interface (DIF)   |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Common Block Firmware      |          |          |                                           |               |     |           |            |         |          |           |          |          |

| AHCAL Block Firmware       |          |          |                                           |               |     |           |            |         |          |           |          |          |

| Circuit Design/Layout      |          |          |                                           |               |     |           |            |         |          |           |          |          |

| PCB Production/Assembly    |          |          |                                           |               |     |           |            |         |          |           |          |          |

| CALIB, POWER               |          |          | An |               |     |           |            |         |          |           |          |          |

| Circuit Design/Layout      |          |          |                                           |               |     |           |            |         |          |           |          |          |

| PCB Production/Assembly    |          |          |                                           |               |     |           |            |         |          |           |          |          |

| System Tests               |          |          |                                           |               |     |           |            |         |          |           | ****     |          |

| DAQ Software, LDA          |          |          |                                           |               |     | E.        |            |         |          |           |          |          |

| Component Ordering         |          |          |                                           |               |     |           | 1          |         |          |           |          |          |

| Prototype                  |          |          |                                           |               |     |           | 1          |         |          |           |          |          |

| EUDET Mod. (Final)         | 28 05 08 |          |                                           |               |     |           |            |         |          |           |          |          |

Milestone shifted now by 1 month to Nov. 08. Full slab not available before mid 2009.

- -AHCAL techn. prototype (TP) does not cover a full slab, but ~150 channels (2 HBUOs, tile-prototypes).

- -Eudet module (detector layer) requires HBU redesign (mid 2009).

- -timeline for TP is defined by HBUO (input SPIROC2, tile geometry).