IN2P3

### **ECAL Electronics Status**

Orsay Micro Electronics Group Associated

# ASIC design SKIROC 2

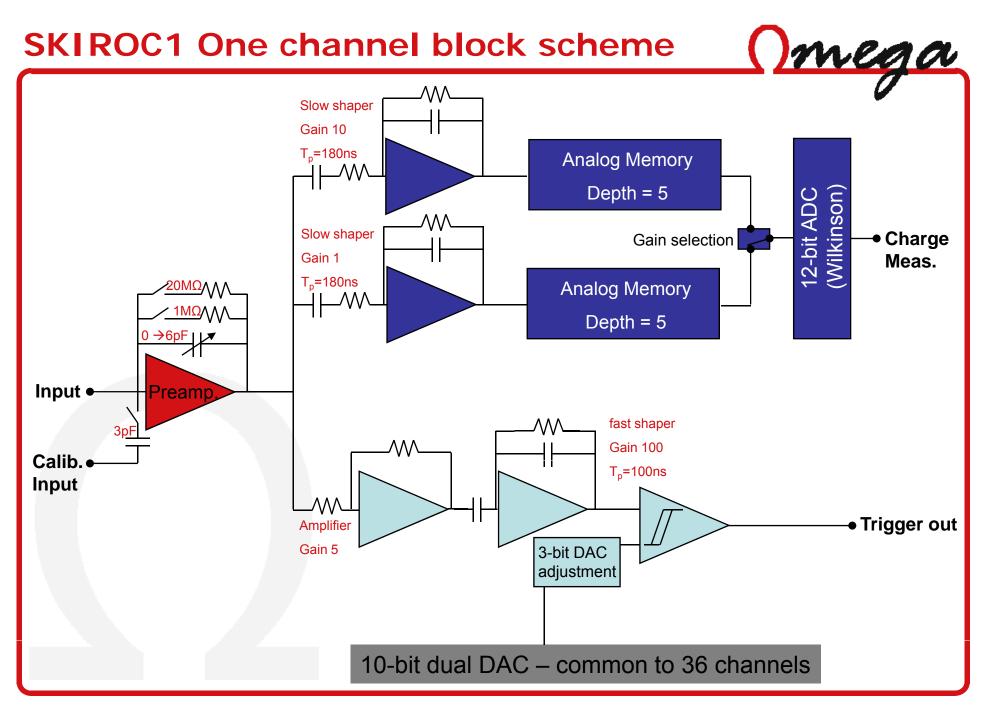

### **SKIROC 1 design limits**

- Most critical issue : Too much dynamic range in the charge preamplifier

- Max input signal : 2000 MIP

- Noise floor : 0.15 MIP

- Preamplifier gain too small

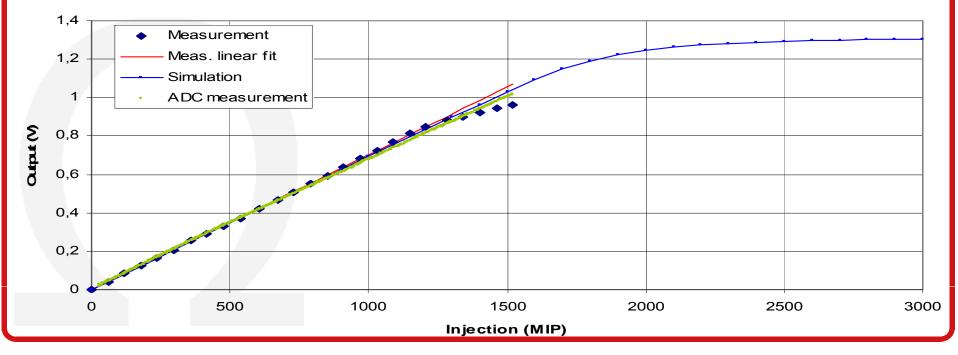

- Huge gain in the trigger path to be able to trig on 1/2 MIP SKIROC linearity results

1 December, 2008

()mega

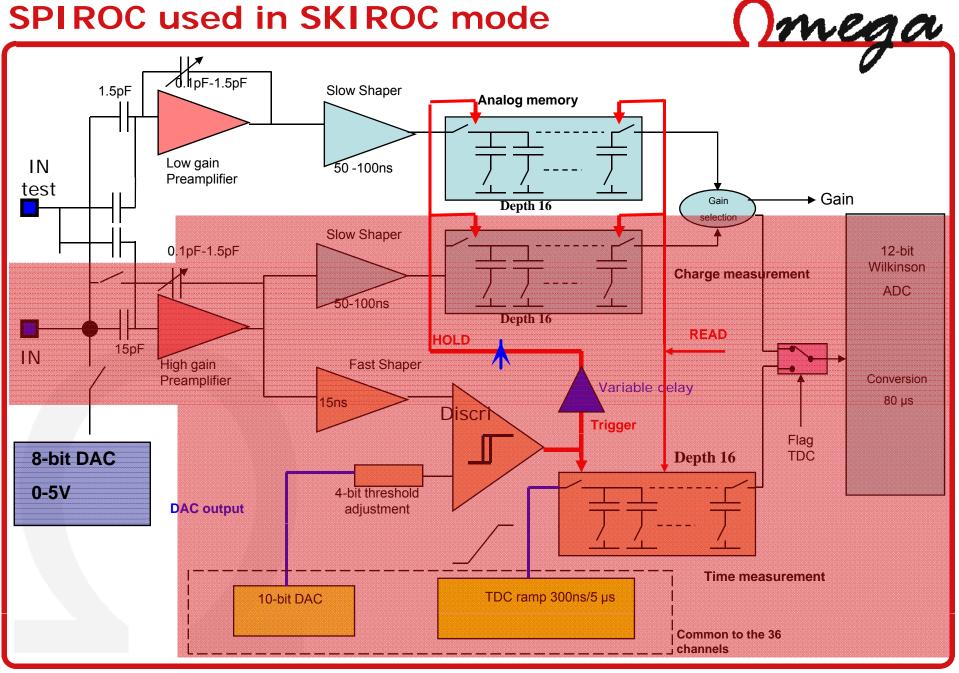

### **SPIROC** used in **SKIROC** mode

- Dynamic range : -500 MIP/cell → same as physics prototype

- Number of channels :

- 36 instead of 64

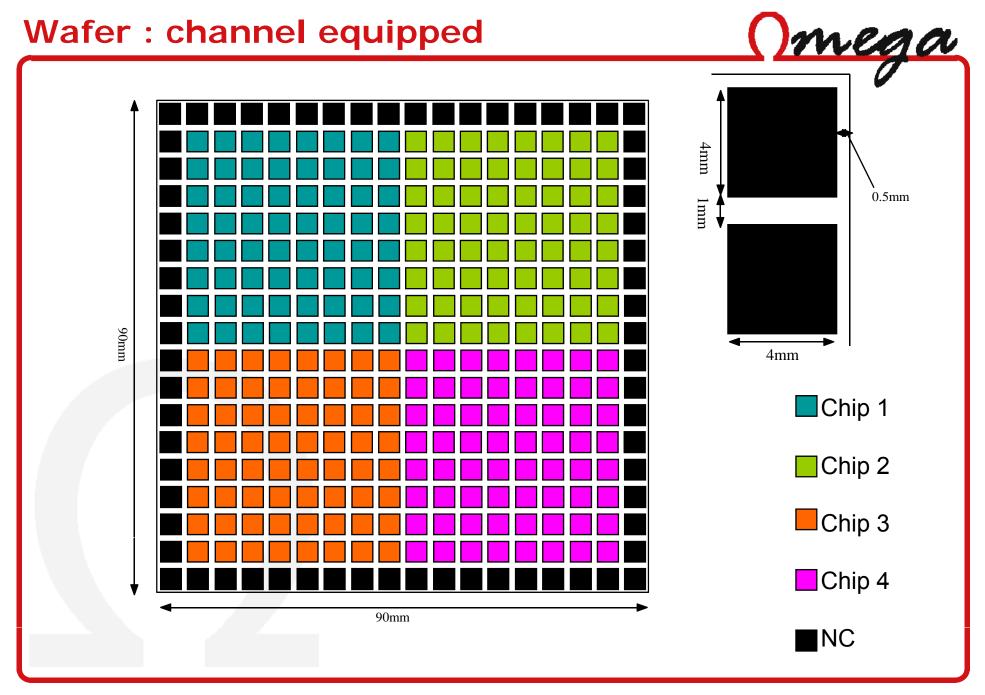

### **Expectations for EUDET**

- 64 channels to read out new 256 pads wafers with 4 chips

- This is a critical PCB requirement

- This will make SKIROC2 the biggest chip of the ROC family

- 50-60 mm<sup>2</sup>

- Capability to operate in ILC mode and in test beam

- This is a physics requirement to take data with EUDET module

- Calculation of data rates to be validated

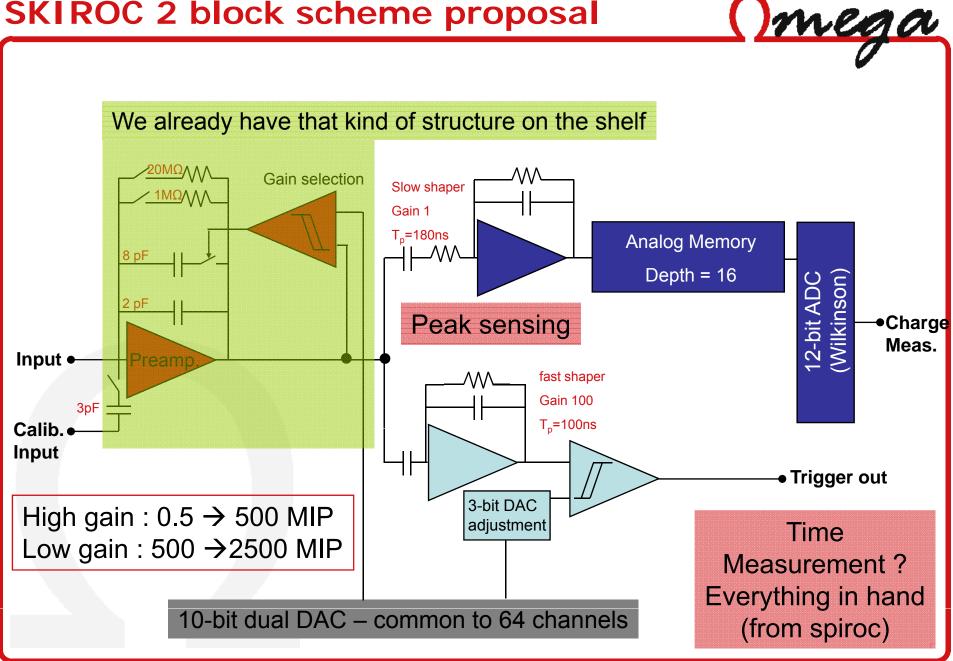

- High dynamic range from 0.1 to 2500 MIP

- (Eventually) time measurement to tag events in test beam (not useful in ILC mode)

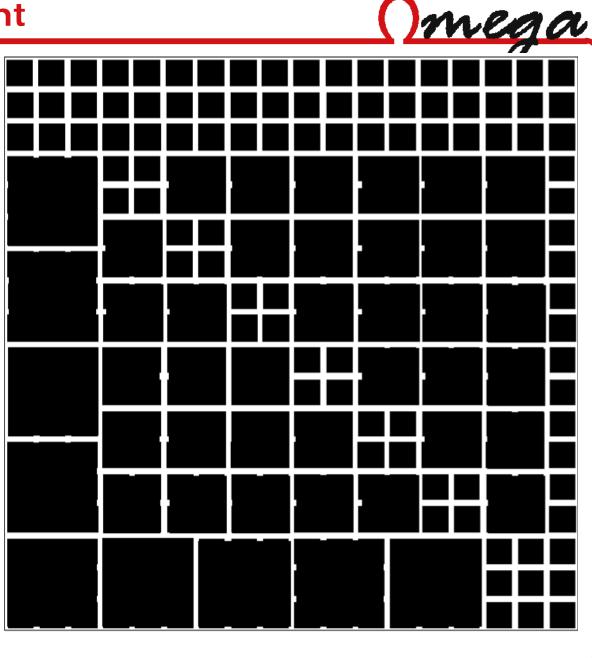

### SKIROC 2 block scheme proposal

### **Schedule**

- Skiroc 2 expected to be sent in fab in March'09

- Sharing of the HARDROC2 and SPIROC2 production

- If SKIROC 2 is validated → production in hand for EUDET module

- Cheaper than an engineering run for prototyping due to big silicon area (60mm<sup>2</sup> ie ~60k€)

- Next PCB prototype will use SPIROC2 with Hamamatsu wafers

- Validation of all electronics and assembling process

- missing : dynamic range (500MIP/2500MIP), granularity

- PCB in hand before the end of the year?

mega

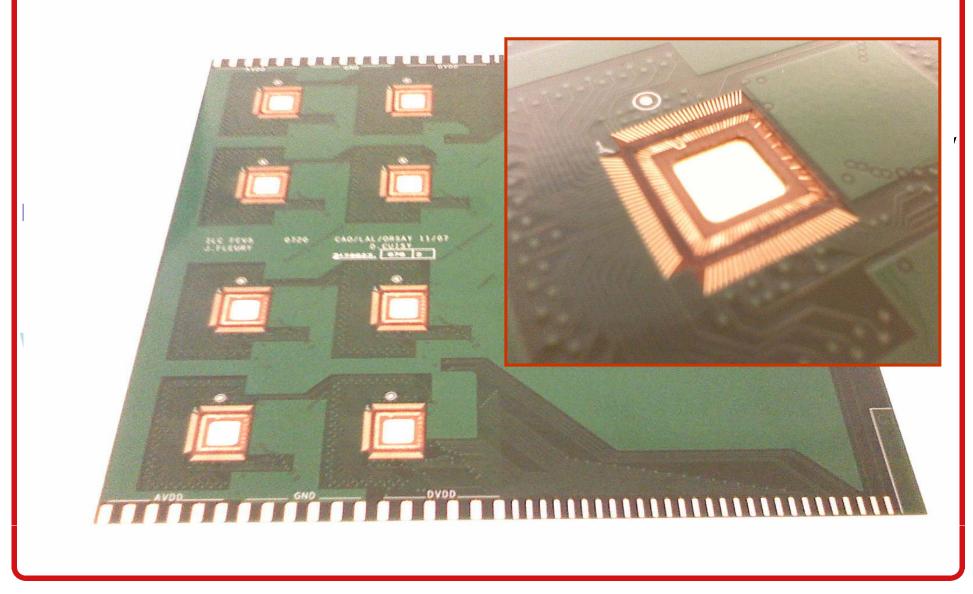

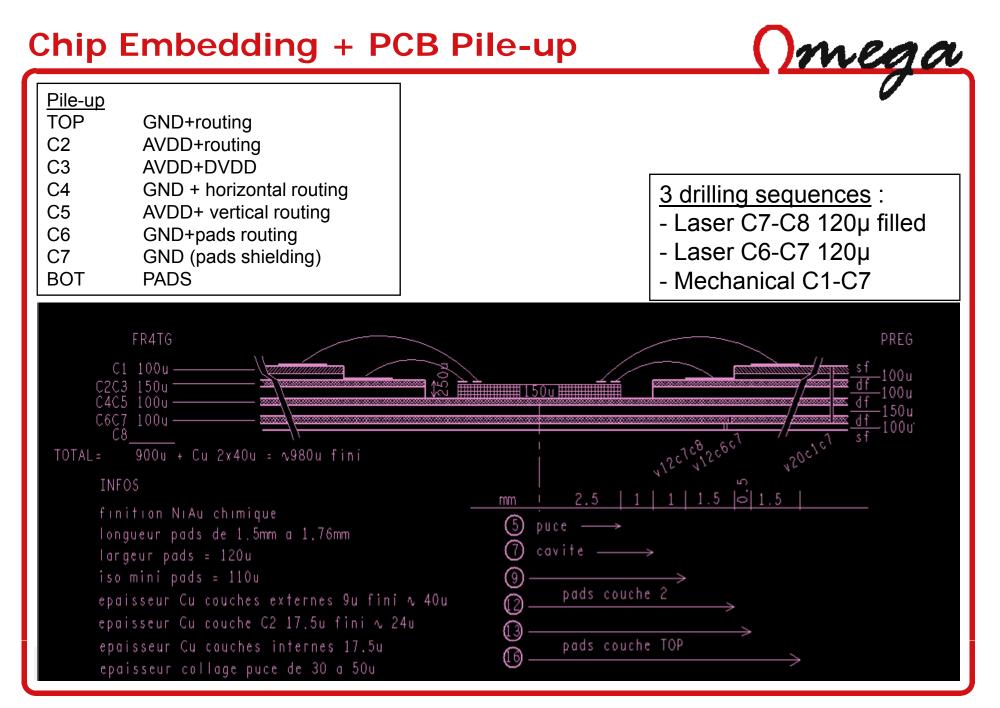

# PCB design FEV 5 presentation

### FEV5 : design

### **Issues : Layer 2 not bondable**

#### 1 December, 2008

### FEV7

- First EUDET compliant PCB, using SPIROC2 in SKIROC mode.

- several pads merged for each electronics input

- Halfway from expected granularity and physics prototype granularity

<u>(mega</u>

### **FEV7** wafer footprint

144 Channels Will be used for Wafer charact. Need SPIROC2 validation

### Conclusion

- PCB design

- FEV5 engineering done

- NOT SO EASY TO BUILD → still not validated

- Opportunity to have 256 ch. Wafers ? (5.5mm pads)

- For FEV8 design

- To be available in Spring 09

- FEV7 design using hamamatsu Wafer and Spiroc 2 in 2008

- Front-end ASIC design

- Skiroc2 planned for march 09

- All test with Spiroc2 before then, when validated

mega