# SiW Ecal EUDET Module

From the TDR to the Demonstrator and beyond

> Roman Pöschl LAL Orsay

To learn more ....

http://flc.web.lal.in2p3.fr/poeschl/siwecal.html

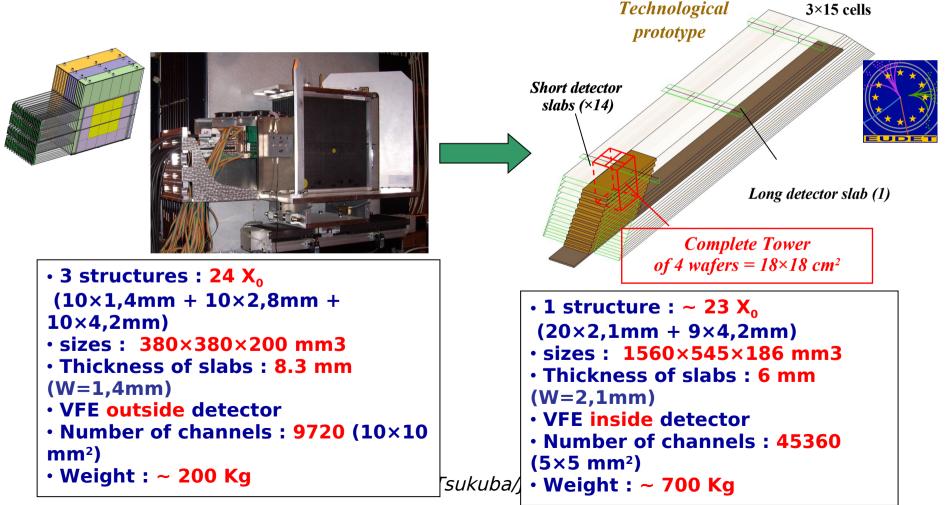

### **EUDET Prototype**

- Logical continuation to the physical prototype study which validated the main concepts : alveolar structure , slabs, gluing of wafers, integration

- Techno. Proto : study and validation of most of technological solutions wich could be used for the final detector (moulding process, cooling system, wide size structures,...)

- Taking into account industrialization aspect of process

- First cost estimation of one module

2

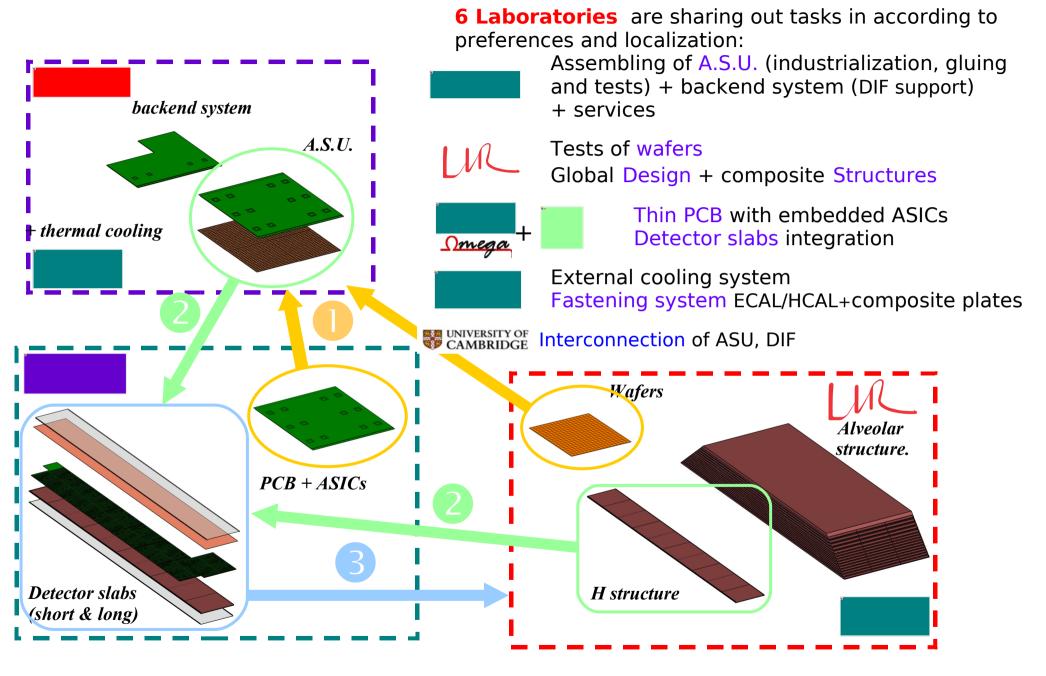

### The groups working on the EUDET Electromagnetic Calorimeter

- What we call "EUDET Module" is in fact the next SiW Ecal CALICE Prototype

- Financial support by EU but largest fraction of funding still from "Calice" ressources!!!!

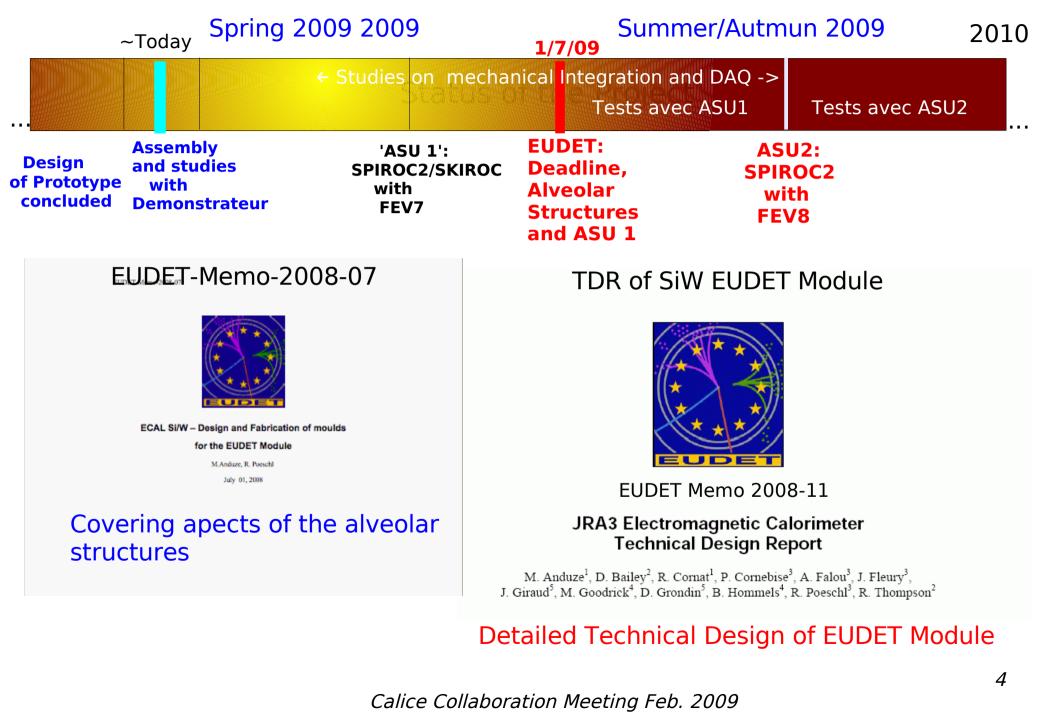

## Time Scale of Project

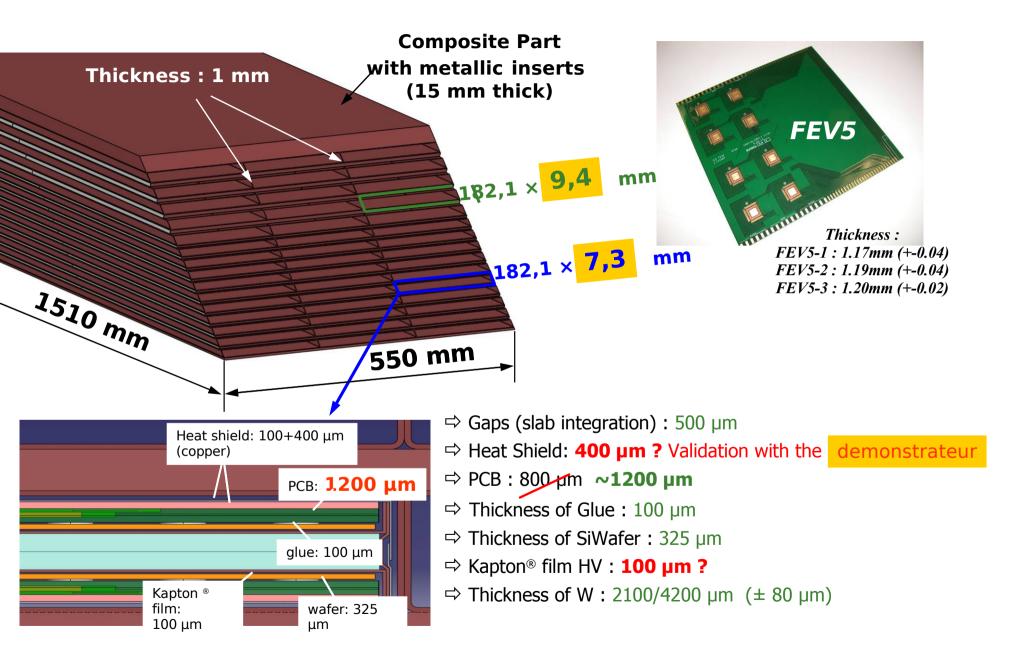

### Module EUDET – Current Design (final)

### **Parties Involved**

# Sensors layout

### Find a low cost but effective sensor

#### Why ? ILC would need 3000 m2 of them

How ? Smallest number of manufacturing steps •PIN diodes

•Guard-rings made with the same steps :

floating guard-rings

- •Easy to integrate : gluing

- Low leakage current (<4 nA/cm2)</li>

- •Stable in time and for gluing

- I(Vbias) : leakage

- •C(Vbias) : depletion and dC/dV noise

Last prototype :

- 3 production batches (2005-2007)

- Russia (Moscow State University)

- Czech Republic (Institute of Physics)

- Korea

- 6x6 pads, 525 um thick, 200V bias

- MIP = 42000 electrons

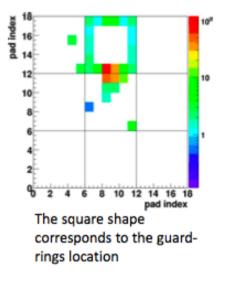

### Cross talk observed during prototype testbeam

Rémi CORNAT - NSS 2008 - Dresden, Germany

# Sensors : unexpected behavior

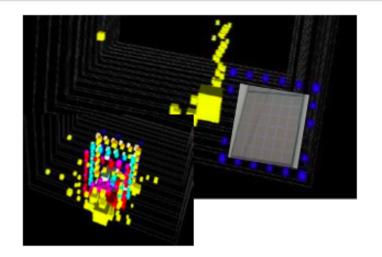

When a particle hit the floating guard-rings...

Unbiased guard-rings act as a pad all around the sensor

Definitely confusing for clustering and reconstruction

Guard-rings are mandatory to avoid breakdown = need to find a turnaround which meet the cost requirements

That's (also) what test beams are good for!!!!!

Don't think that you're perfetct - Detect the unexpected!!!

5

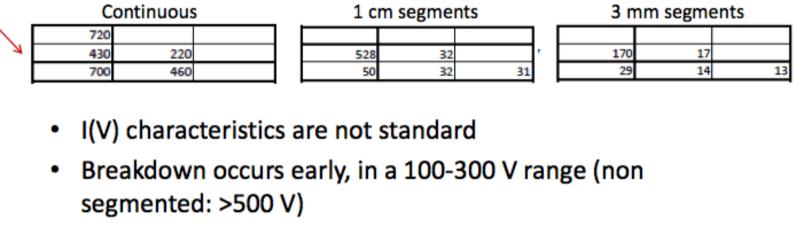

# Segmented guard rings prototypes preliminary measurements results

The segmentation of guard rings clearly contributes to the lowering of crosstalk along the edge of the wafers

- BUT: no optimizations were done on the layout

- Further investigations are needed

- Close contacts with Onsemi: agreement to share the costs

5

Measurement backed up by theroretical calculations (NSS Proceedings by R. Cornat)

Pixel cross talk seems to be understood – Conclusive remedies are under study

# Hamamatsu wafers

- 9x9 cm2, 256 pixels ordered, 40 should be delivered on April

- Cost ! (eur/yen parity)

- 300 um (may be) gained on the edges

- 800 um dead space (1.1 mm in previous version)

- Excellent breakdown >800 V

- Low leakage <4 nA/pixel</li>

- DC coupling to the chips

- 1 nA = 1% dynamic range

- Good dC/dV at Vbias, <2pF/V (full wafer)</li>

- Mandatory for noise (CdV + VdC)

- C= 10E-12, dV=10 mV, V=150V, dC = 20 fF => ~400 MIPs...

week at Deagu, Febuary 19

- Wafer Type at hand which meets requirements

- However, vey expensive!!!

- Broaden basis of manufacturers ( FZU (Cz), OnSemi (CZ), MSU (Russia), Korea)

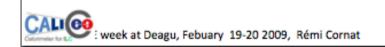

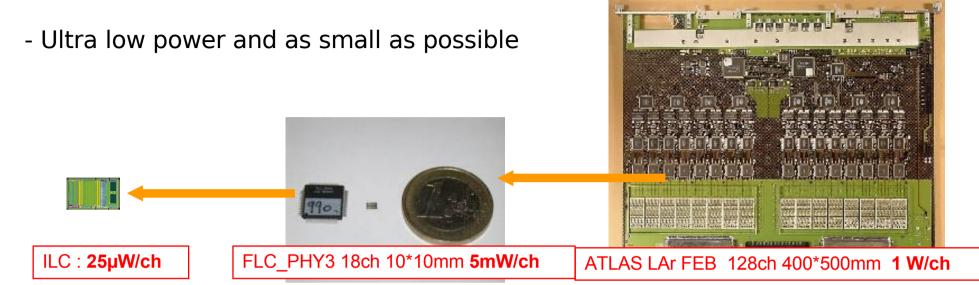

### **SKIROC** Chip

- Designed to read out 64 Channels => 4 Chips per Wafer

## SKIROC1 One channel block scheme

### SPIROC used in SKIROC mode

TILC09 Tsukuba/Japan April 2009

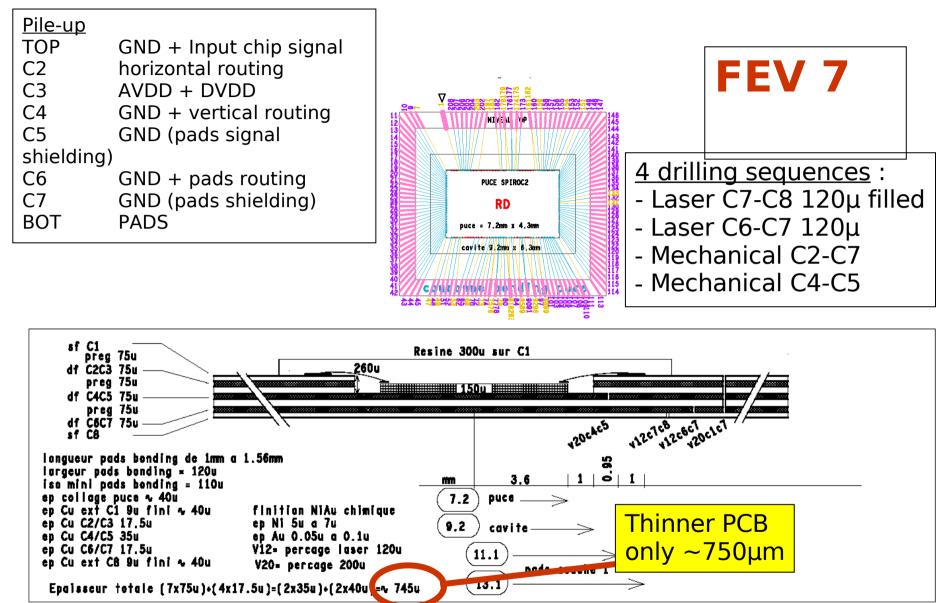

Printed Circuit Board – Interface between Si Wafers and Chips

#### **Very Challenging project – Design under revision**

In contact with CERN and Industrial Partners (seems to be beyond industrial standards)

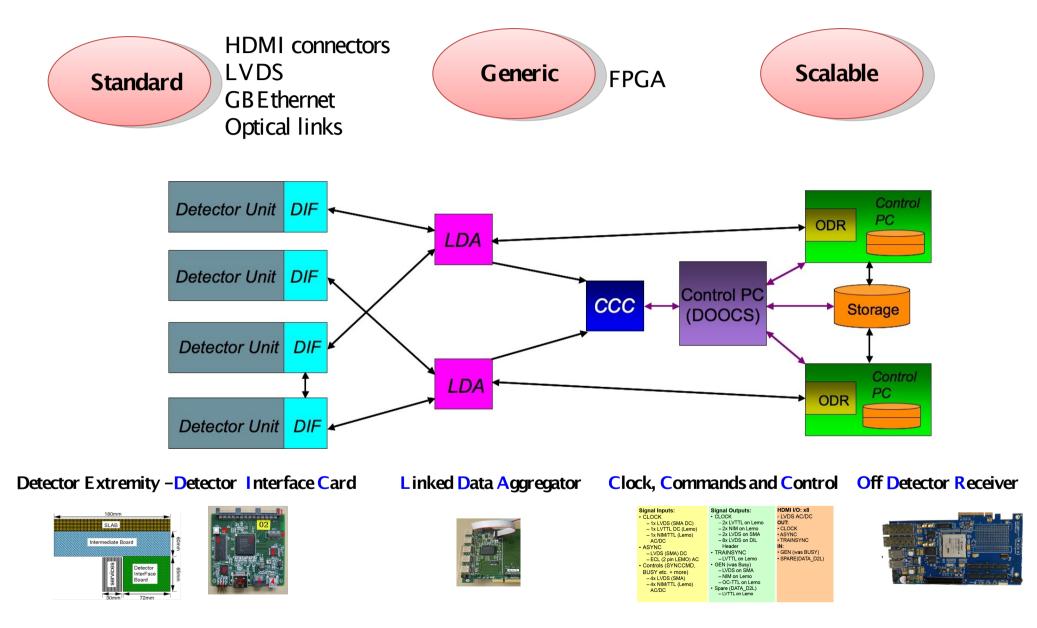

# A generic DAQ System

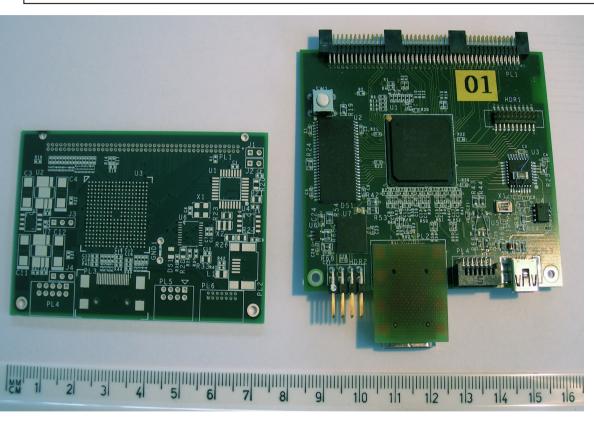

# ECAL DIF - 2nd revision coming up

Status: 8 DIF prototypes now produced and commissioned

# ECAL DIF: small form factor. No room for extra features!

- Xilinx Spartan3 based

- USB, HDMI connections

DIF re-spin for EUDET in creditcard size form factor. Main changes:

- No external SRAM, user connector, reset button

- SPI-flash PROM, Flash RAM for VFE config

### Hardware status:

PCB designed & produced, some components still being ordered, board population, testing to be done

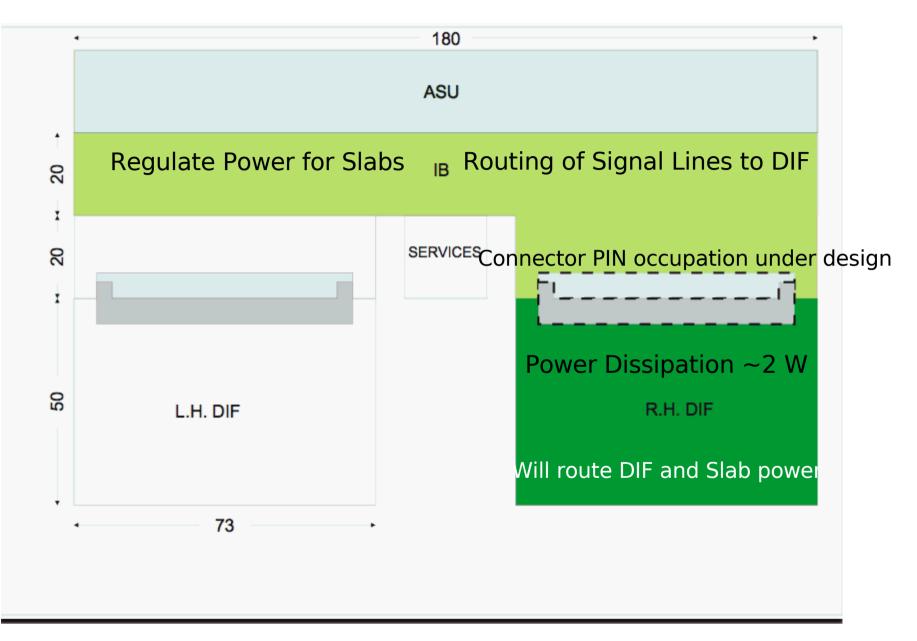

### Agreed Dimensions DIF/IB Region

### Gluing of ASUS

- Controlled glue dot deposition on the PCB

- The (four) Si Wafers are picked up, aligned and placed on the PCB

- Accurate thickness and planarity control via vacuum jigs

- The assembled ASU is allowed to cure

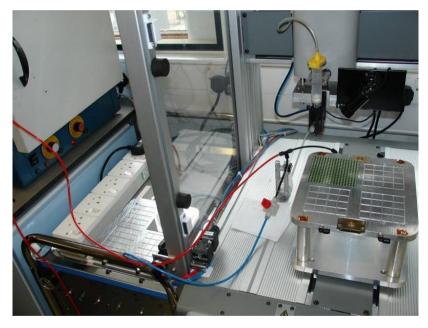

### Test board with Dispenser Robot

### BGA Workstation for Wafer Placement

"Gluing" rate 0.4 Hz

Precise Wafer Placement by Split Field Optics

ASUs for four thermal layers glued at Uni Manchester

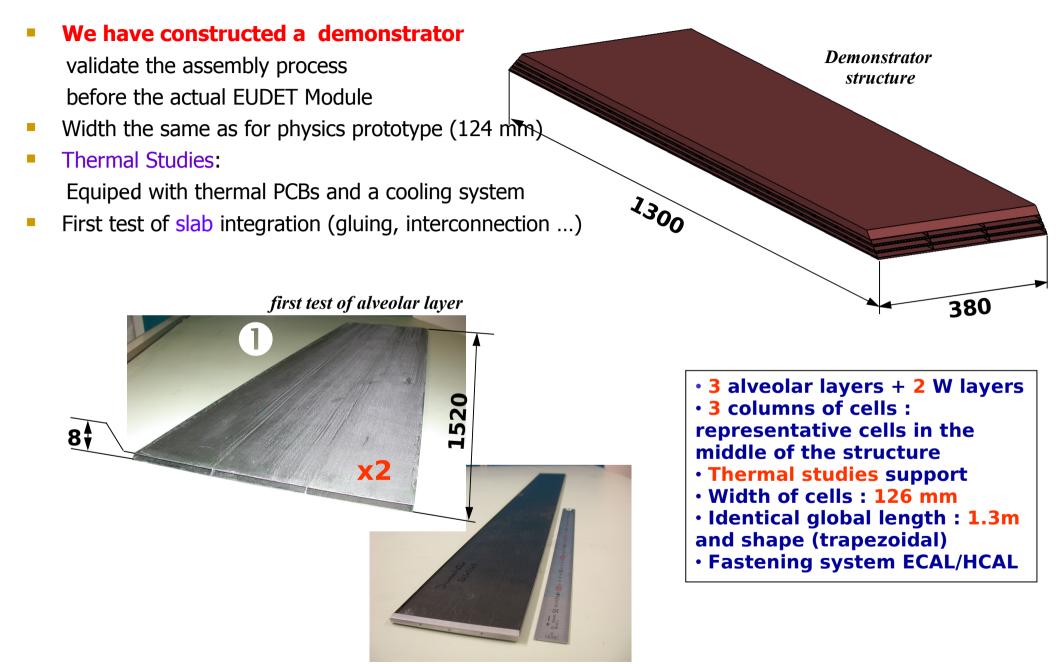

### Demonstrator design

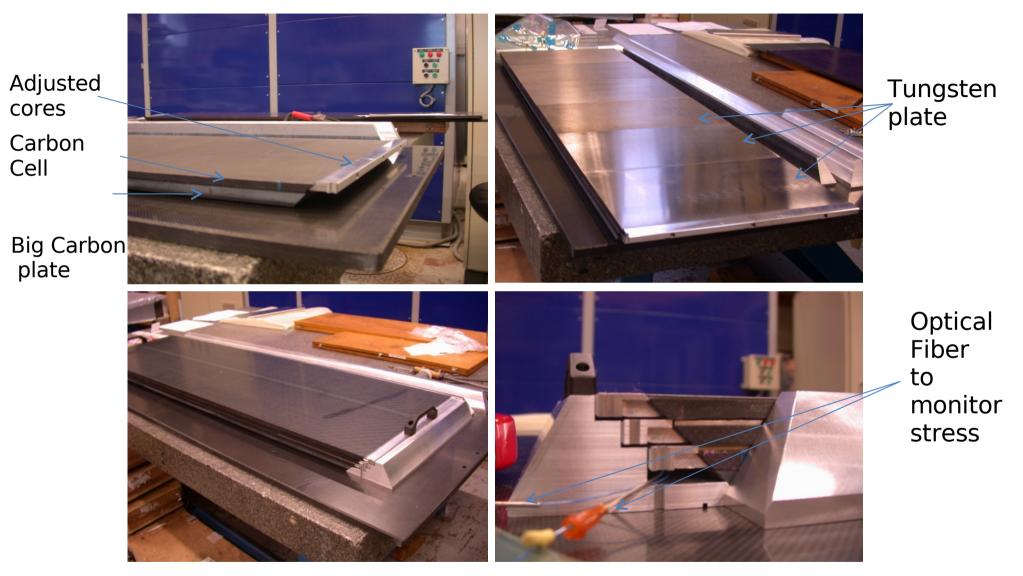

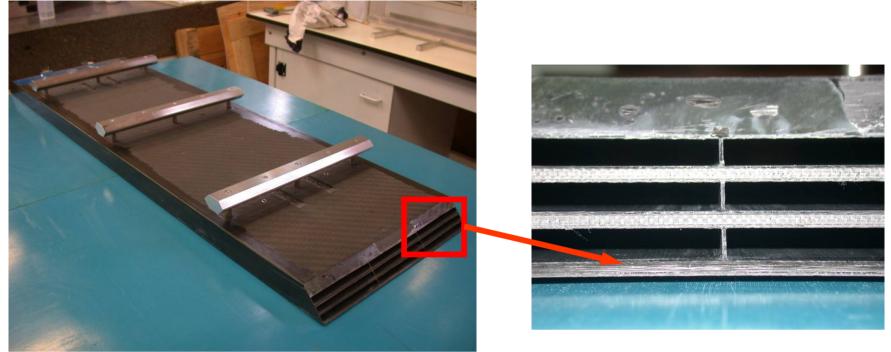

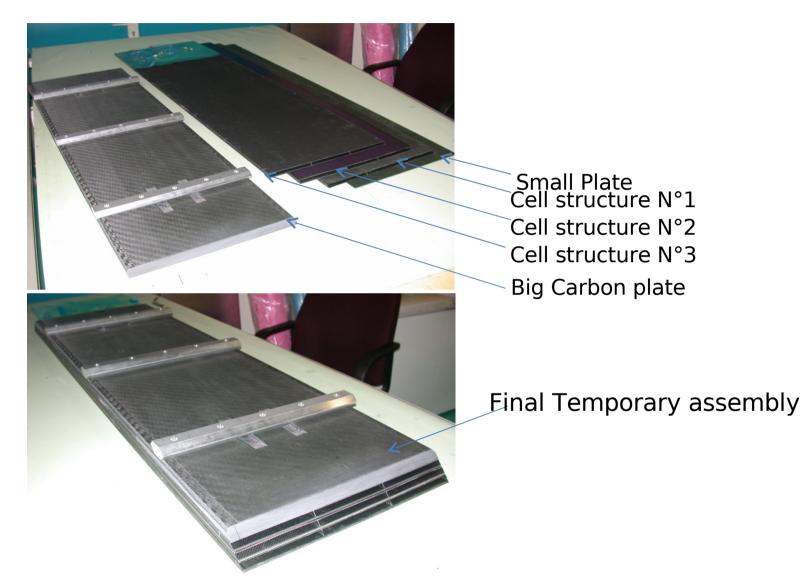

### **Full Assembly**

...including Aluminum Cores and Assembly Mould -> Ready for Curing

#### Alveolar Structures with (~) ILC Dimensions – Yes, we can!!!!

TILC09 Tsukuba/Japan April 2009

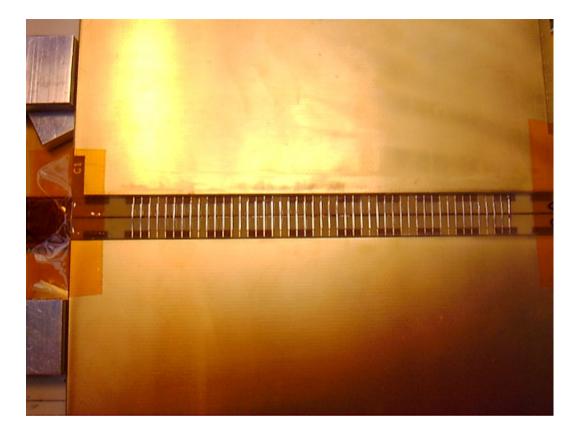

#### The joint between two boards

- Joint by halogen lamp heating up tin-bismuth soldering paste (Method developed by U. Cambridge)

- Heating Temperature  $\sim 200^{\circ}$  C

Delicate Process for Demonstrator – Easier for EUDET Module

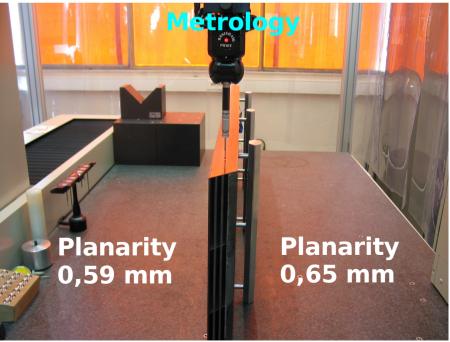

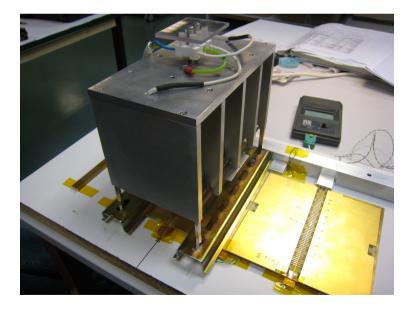

#### Thermal Layer assembled and ready for Thermal Tests

- w/o Photo: Copper Shielding and CuCe Electrical Protection manufactured at CERN in Collaboration with CALICE

# First Results from Thermal Tests/ demonstrator

YES: ALL IS LINEAR

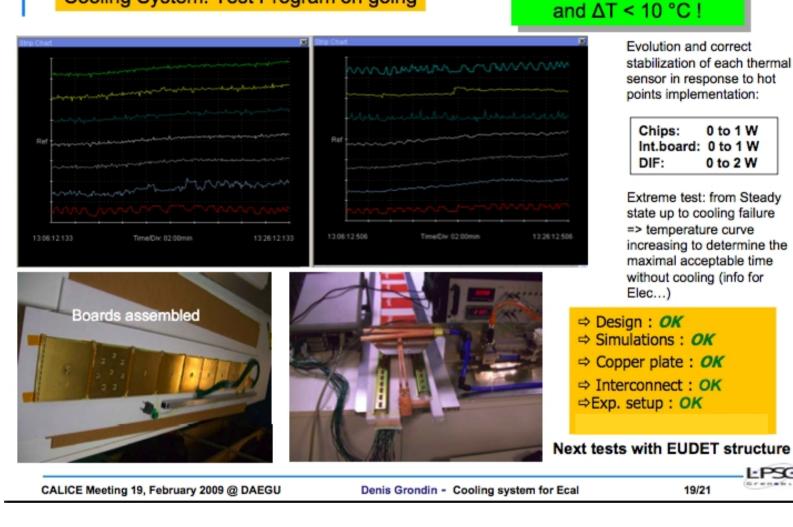

#### Cooling System: Test Program on going

- First test measurements did validate simulation

- However conclusions compromised by convection in workshop and not optimal thermal contacts with copper drain

- Optimisation studies ongoing Continuation of tests Middle of May 09

**Conclusion and Outlook**

- Technical Design finished in Oct. 2008 Preparation and conduction of Demonstrator Tests since then

- In the middle of the studies with the demonstrator

- First measurement for thermal analysis

- Assembly of alveolar structure finished

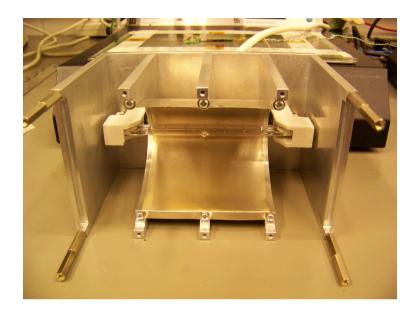

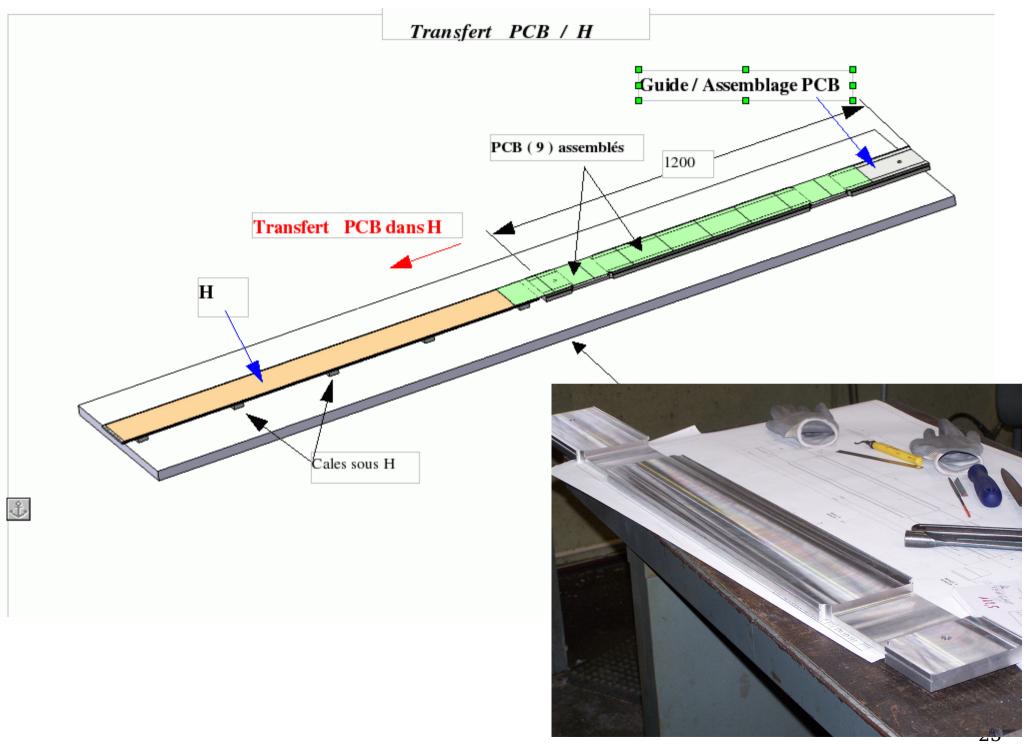

- Integration cradle for long slab ready

- Revision of thermal drain ongoing

Demonstrator studies finished by July 2009 Will cover most if not all mechanical aspects described in EUDET proposal Conclusion and Outlook cont'd

- Towards the EUDET Module

- Construction of H Structures and alveolar layers seems feasible Demonstrator can be extrapolated to full blown structure

- "Wrapping" of Slab and Integration Cradle for 'real' slab

- First protoype in hand needs further study

- needs special tools which are very <u>expensive</u>!!!!

- Excellent progress concerning Si Wafers

- Wafers according to specs available (However expensive)

- Corss talk problem understood

- Focus of getting the VFE accomplished in (early) 2010

- "Shipping" signals out Interface to the DAQ and beyond will be advancing

First Assembly of the Alveolar Structure for the Demonstrator Mechanical Structure only slightly smaller than for EUDET Module

All pieces for mechanical housing of "Demonstrator" Slabs available

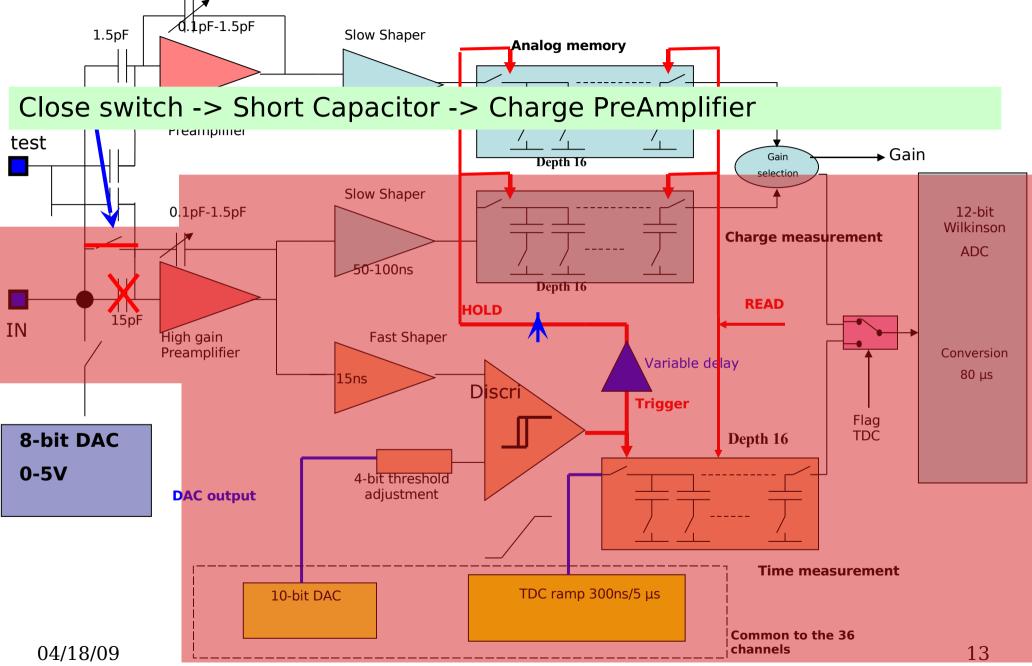

# SPIROC in ECAL

- Limitations :

- Dynamic range :

- 500 MIP/cell → same as physics prototype

- Number of channels :

- 36 channels instead of 64  $\rightarrow$  lower granularity