#### Si-W ECAL Silicon wafers status

🔬 🗤 week at Deagu, Febuary 19-20 2009, Rémi Cornat

### Si overview

- Cz and Rus used on the prototype (low cost, standard design)

- Ok : Depletion, current leakage, signal

- 500 nm, 6x6 cm<sup>2</sup>, 26 pads

- Square events : understood to come from guard rings

- Search for new design techniques

- Reducing crosstalk due to the GR

- Segmented guard rings to avoid square events

- Lowering Dead space (at the border)

- Hamamatsu design

- New size ordered: 300 nm, 9x9 cm<sup>2</sup>, 256 pads

- Sold as having no guard rings (thus no square events)

- Have guard rings ! External charge injection shows square events...

- Large dead space

- Behavior with glue checked over 8 months : OK

- Cost of prototypes: 70 k€ = 40 wafers, not enough for EUDET

NEW : Prototypes are measured !

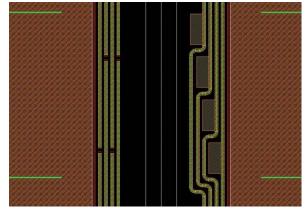

## Segmented guard rings

- Should avoid the signal propagation along the border of the wafer

- Idea tested thanks to PCBs and test bench at LPC (CALOR'08, NSS-MIC'08 talk)

- Segmented topology helps to prevent SqEvt

- Prototype wafers are being manufactured (LLR made layout)

- OnSemi/Institute of Physics (Prague), Cz

- Current leackage can now be measured

- Together with crosstalk

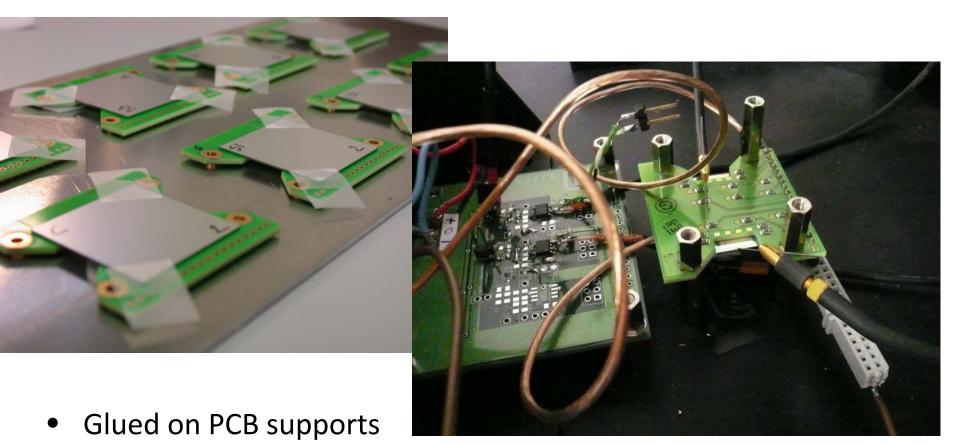

- First 8 wafers were measured at LPC

# Segmented guard rings prototypes

• Mesured with signal injection and charge amplifiers

## Segmented guard rings prototypes preliminary measurements results

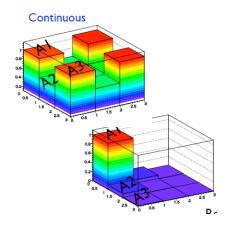

• The segmentation of guard rings clearly contributes to the lowering of crosstalk along the edge of the wafers

| Continuous |     |     | _ | 1 cm segments |     |    |    | 3 mm segments |     |    |    |

|------------|-----|-----|---|---------------|-----|----|----|---------------|-----|----|----|

|            | 720 |     |   |               |     |    |    |               |     |    |    |

| И          | 430 | 220 |   |               | 528 | 32 |    | 1             | 170 | 17 |    |

|            | 700 | 460 |   |               | 50  | 32 | 31 |               | 29  | 14 | 13 |

- I(V) characteristics are not standard

- Breakdown occurs early, in a 100-300 V range (non segmented: >500 V)

- BUT: no optimizations were done on the layout

- Further investigations are needed

- Close contacts with Onsemi: agreement to share the costs

## Hamamatsu wafers

- 9x9 cm2, 256 pixels ordered, 40 should be delivered on April

- Cost ! (eur/yen parity)

- 300 um (may be) gained on the edges

800 um dead space (1.1 mm in previous version)

- Excellent breakdown >800 V

- Low leakage <4 nA/pixel</li>

- DC coupling to the chips

- 1 nA = 1% dynamic range

- Good dC/dV at Vbias, <2pF/V (full wafer)</li>

- Mandatory for noise (CdV + VdC)

- C= 10E-12, dV=10 mV, V=150V, dC = 20 fF

~400 MIPs...

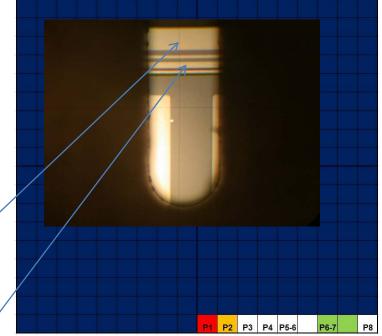

# Hamamatsu wafers : crosstalk measurements

Charge is injected on the metal rings: a similar behavior as for square events is measured. Compared to PCB models with continuous guard rings :

Factor 4 less for the outer guard ring

Factor 50 less for the inner guard ring

Square events are expected !

| Pixel ID | Amplitude |

|----------|-----------|

| P1       | 1030      |

| P2       | 1060 (mV) |

| P6-7     | 2080      |

| Pixel ID | Amplitude (mV) |

|----------|----------------|

| P1       | 80             |

| P2       | 63             |

| P6-7     | 111            |

But signal (charge) is injected at the surface. What if charge is generated in the volume below the rings ?

### It needs further investigations with particles or laser beam

## Layout: Some optimizations

**3D sensors** : lower Vbias, internal current flow, low sensibility to edge effects : can be ~edgeless (100 um)

# tor Vertex detectors Cut through edge

Integration same technology as for 3D but used only at the edge no saw cuts, 3D edges 4-side abuttable ~*no dead space*, Deep trench etch, n doped polysilicon fill provides edge doping

**Trenches + saw cut** : cost of trenching, post processing of every sensors, bad control of current.

#### Dry etching cut

Cost

#### **Current terminating ring** two rings but biased : thin contact needed, gluing not applicable edge width less than <sup>1</sup>/<sub>2</sub> wafer thickness **Double sided GR Doped edges** Crosstalk + ~edgeless ③ (300 um) **Punch-through biasing** Integration 😕 **Biased GR** edge 🙁 (800 um) Segmented GR : need further tests week at Deagu, Febuary 19-20 2009, Rémi Cornat

## Front end board

- Hamamatsu wafer will have pads to bias the GR in order to avoid crosstalk (if necessary)

- FEV7 to be adapted for bounding (holes)

- Prototype for a definitive solution (additional cost) if segmented/other do not work

- FLCPHY3 should be used for crosstalk measurements

- Instead of Op. Amp.

- Upgrade of test bench at LPC

- measurements with laser or beam

week at Deagu, Febuary 19-20 2009, Rémi Cornat

#### **ECAL Silicon wafers : Conclusion**

#### <sup>In2p3</sup> Hamamatsu wafers expected on Q2'09 (NRE 31k€ + 1k€/sensor) despite some uncertainties on crosstalk (~OK) In touch (or at least try) with other manufacturers (ONsemi, Russia, Korea,...)

Segmented guard ring to be tested on full size wafers + with beam

R