# Status of the Data Concentrator Card and plans for the J<sub>DHCAL</sub> DAQ2

Vincent Boudry Franck Gastaldi Antoine Matthieu David Decotigny

**CALICE** meeting

19 feb. 2009 Kyungpook Nat'l U., Daegu, Korea

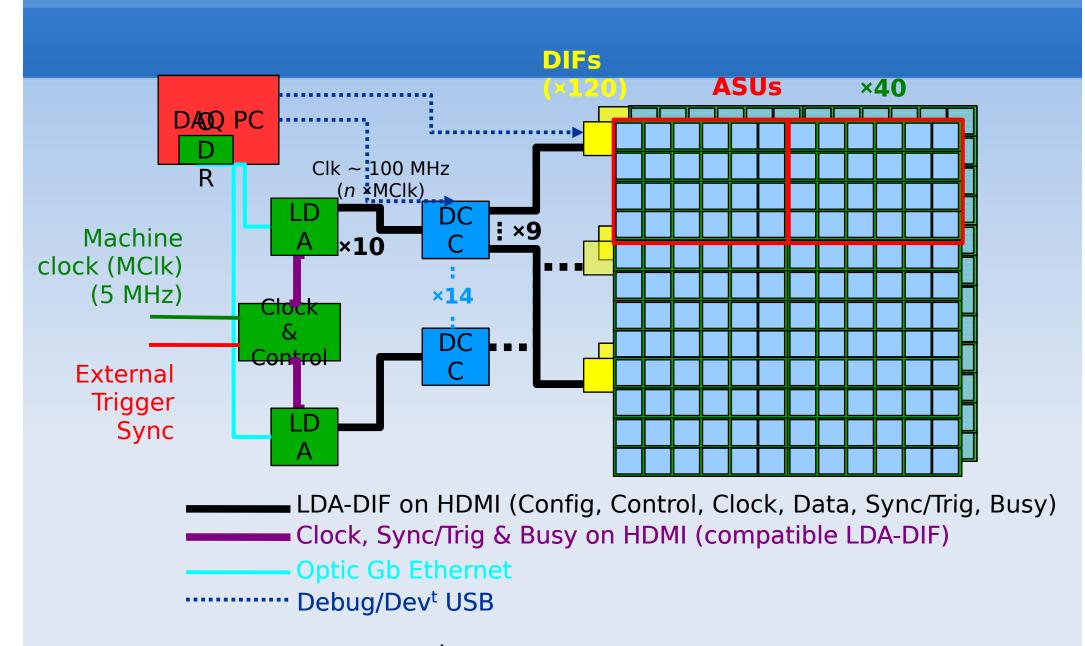

### **EUDET DAQ2 for the DHCAL**

V. Boudry

# The 1 m<sup>2</sup> electronics (quick status)

USB

HDMI

#### **DIF** Julie Prast & Guillaume Vouters

- 10-layer board (6 for signals) designed and prototype produced

- FirmWare & SoftWare operationnal and tested in beam & cosmics (with 4 HR μMegas & 24 HR card)

#### **ASU**s

- RPC: 50×33.3 cm<sup>2</sup> (24 HR) boards produced & tested

- $\mu$ MeGas 32×8 cm<sup>2</sup> 4 HR produced and tested

- HR1 ASICs used

#### data available:

- µMeGas + 4 HR ASU + DIF TB

⇒ not yet analysed

- 48 HR ASU + DIF working in cosmics...

#### **EUDET DAQ2 for the DHCAL**

V. Boudry

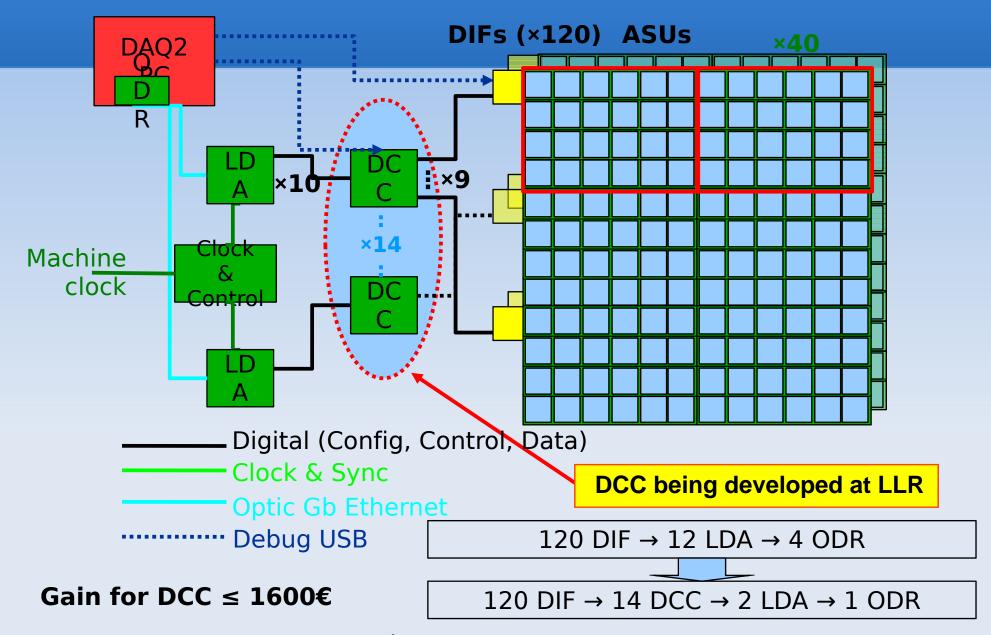

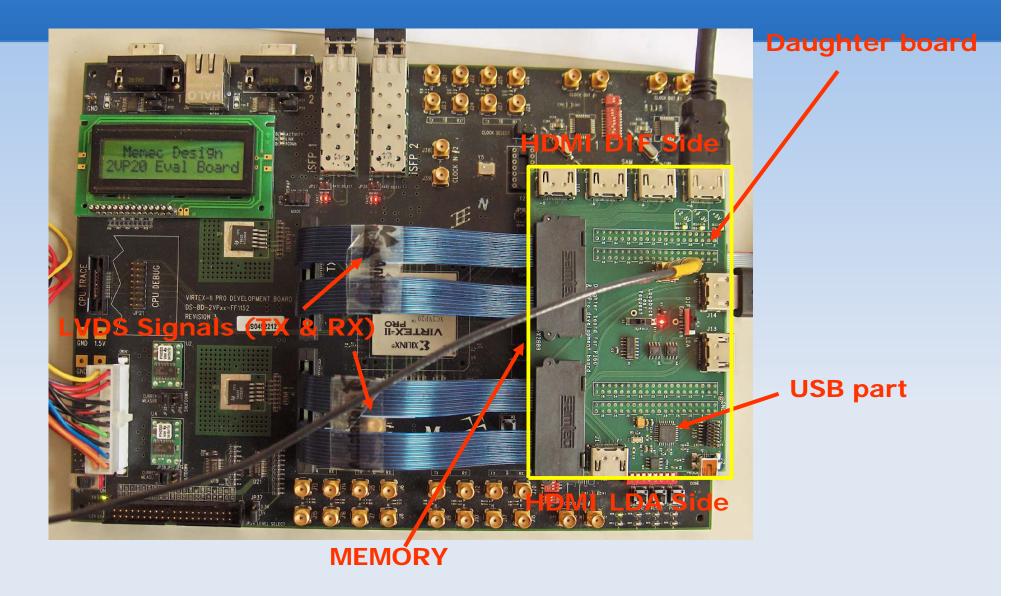

# **Data Concentrator Card**

Franck Gastaldi Antoine Mathieu

#### Goals

Transparency on the path DIF-LDA

- ➢Optimization of flux

- Low cost

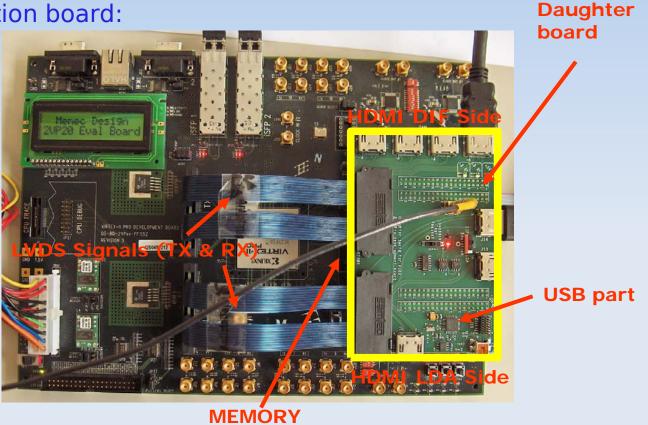

- Pre-proto (proto-0)

- 4 DIFs connections

- Implantation et tests du code VHDL

- Based on a XILINX evaluation board:

- 128 Mbits SDRAM

- Custom Daughter board:

- HDMI connectors

- USB blocs

V. Boudry

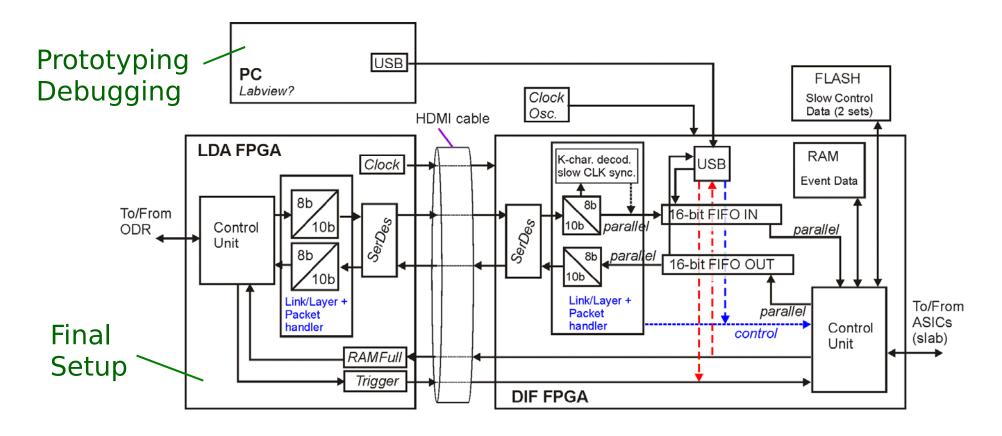

#### **Command Interface - Structure**

- DIF clock (from LDA): 100MHz (40-120MHz).

- Standard data transfer: 8b/10b channel-coding.

- Trigger/RAMFull: uncoded.

USB interface emulates LDA interface (clock-source: free of choice).

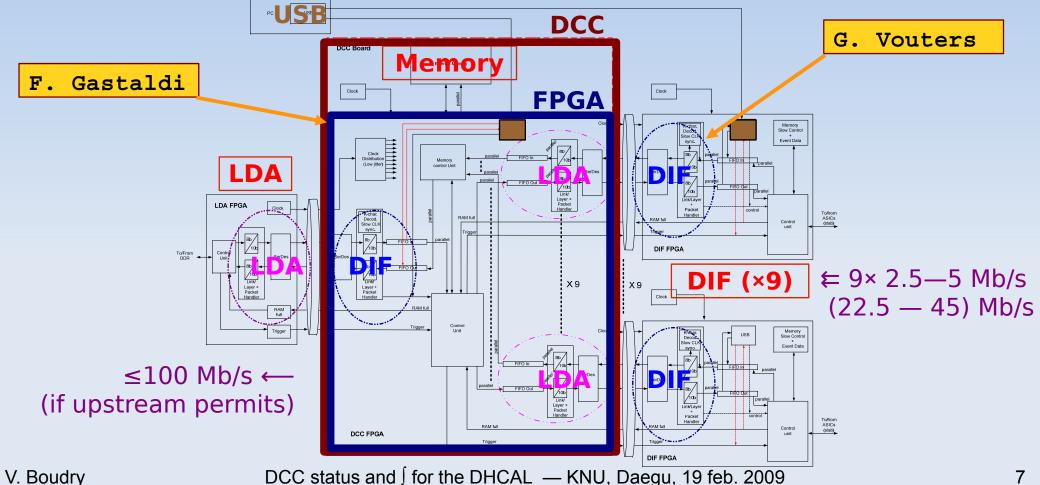

# **DCC prototype data flux**

- Developments:

- Marc Kelly (U. Man) : blocs Ser-Des, coding 8b/10b

- USB blocs (from Clément Jauffret & Guillaume Vouters)

- Original VHDL blocs: Memory controller, commands, buffers (FIFO),.....

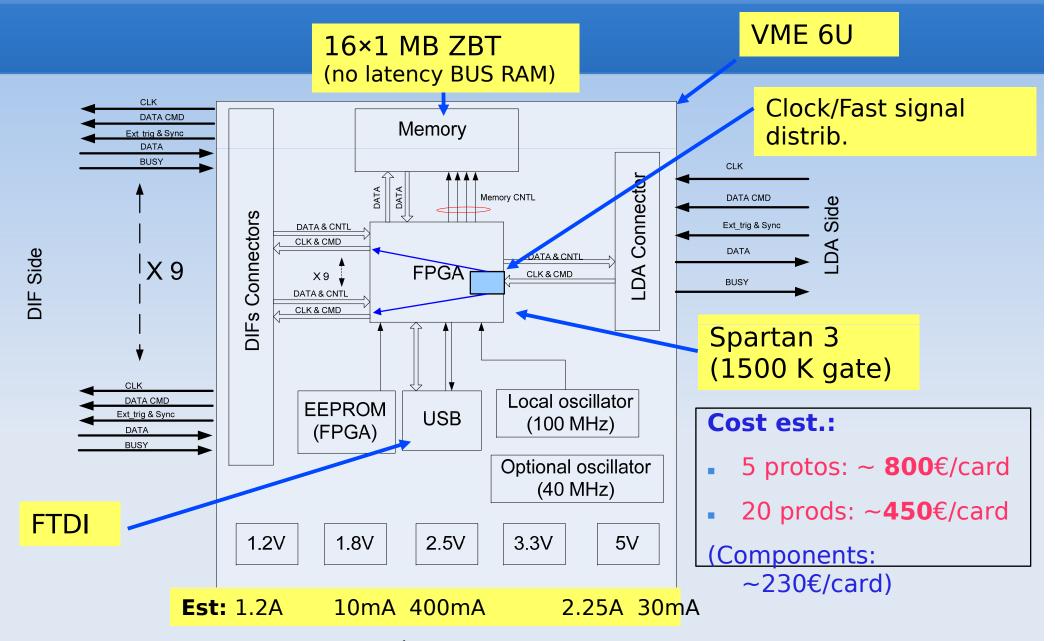

#### **DCC Proto-1**

# **Planning DCC**

- February 09:

- Proto-1

- 2 PCB received

- Cabling ⊂ 2 wks

- March- April 09

- Test of prototype

- Test bench mounting

- Validation & ∫ of VHDL blocs (started)

- Mai June 09 (estimation)

- Production of boards for the m<sup>3</sup>

- Looping DCC-DIF /

DCC-LDA

- Connection with the DIF (code on DIF: started)

:::::

### DAQ2 Hardware: status of 12/12/08

#### Components:

- ▶ 1 Proto-DHCAL DIF ✓, ECAL DIF (2 protos) ✓

- Integration code LDA-DIF on going

- 1 LDA (HW but 8-10 wks , FW ongoing)

- ▶ 1 CCC ✓ (2 cards avail., 8 more in prod)

- ▶ 1 ODR v2 + 1 PC DAQ ✓ (mid feb.)

- I proto DCC (march) or proto-0

- HW and protocols: on-going → March ?

- Mars 09 → Jun 09

- DAQ code DOOCS

- Integration for a m<sup>3</sup>

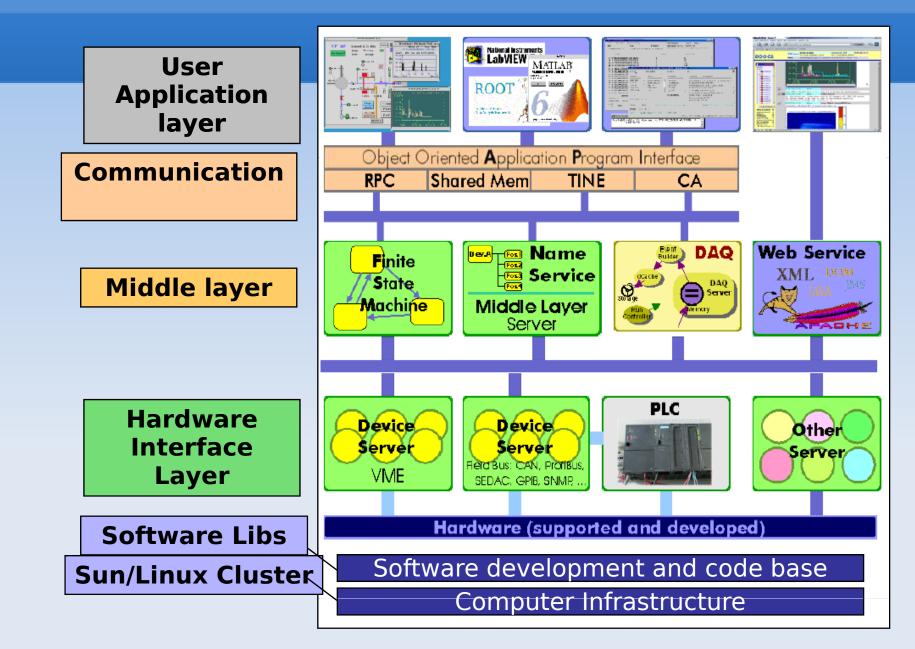

### **DAQ2 SW components: DOOCS**

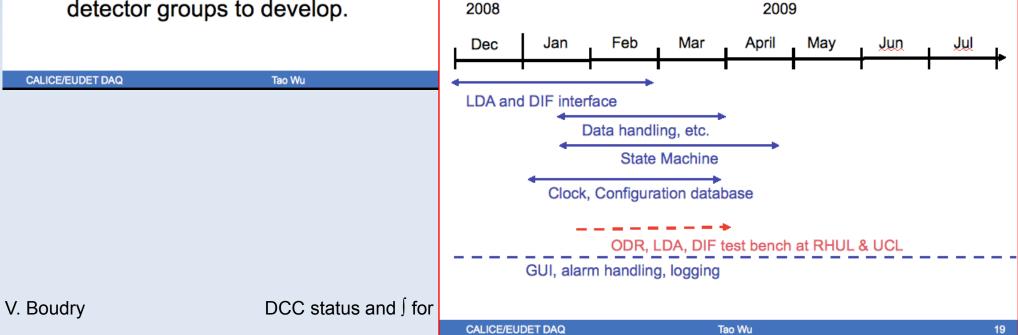

#### DAQ2 SW To do's & Timeline

#### Some essentials

- The components are not integrated in software,

- LDA / DIF / ASICs

- Full chain will be available ~Jan/2009.

- No event building & LCIO converting

- Data are saved to local disk in raw format;

- Just provide interfaces in the framework;

- More flexible way to leave them free for subdetector groups to develop.

2008

### **DAQ2 test benches**

#### Meeting 12/12/2008 in DESY: needs of various groups

- 1 bench in LLR:

- D. Decotigny

- DAQ PC + ODRv2 end-February

- now: PC + DCC pre-proto

- USB access to DCC proto-0

- DCC auto-sending (DIF/LDA)

- scripting (python ?)

- to be used for ECAL tests (See D. Jeans talk)

- test with USB connection on DCC & DIFs

- test readout with ODR + LDA (or emul) of a few DIF's

- integration of all DOOCS components

- LCIO data writing

- Event display

- Database integration with LCDB (MySQL based)

- Slow Control

V. Boudry

#### **Data Flow & expected rates**

|            | N DIF/LDA                                                 |                   |                            | LDA-DIF FLUX      |                    |                     |                                      | Disk Flux     |

|------------|-----------------------------------------------------------|-------------------|----------------------------|-------------------|--------------------|---------------------|--------------------------------------|---------------|

|            | 10                                                        |                   |                            | [MB/s]<br>10      | [MHz]<br>1000      | • •                 |                                      | [MB/s]<br>170 |

|            | 10                                                        | 9                 | 00                         | 10                | 1000               | 120                 | 1000                                 | 170           |

|            | Detector                                                  | DHCAL             | Evt Size                   |                   | ASIC Dclk<br>[MHz] | ASIC FLUX<br>[MB/s] |                                      |               |

|            |                                                           |                   | 20 B                       | 128               | 2,5                | 0,31                |                                      |               |

| Acq Mode   | Mode<br>N ASIC/DIF                                        |                   | Calib/noise<br>Burst<br>48 | TB<br>Single<br>6 | TB<br>Burst<br>6   | Demo<br>6           | Number of hit ASICs<br>for 100 GeV π |               |

|            |                                                           |                   |                            |                   |                    |                     |                                      |               |

|            | ASIC                                                      | 20 B              |                            | 20 B              |                    |                     | LC-DET-2004-0                        |               |

| Limiting — | R/O time 1<br>R/O time ALL                                | 64 μs             |                            |                   |                    |                     |                                      | 4,8<br>2,6    |

| •          | DIF                                                       | 3 072 μs<br>960 B |                            |                   |                    |                     | +3σ /√128                            | 5,49          |

| Factor     | R/O time                                                  |                   |                            |                   |                    |                     |                                      | 0,40          |

|            | 100 1110                                                  | 00 µ3             | 12 200 #3                  | 12 μ0             | 1000 #3            | 1000 μ3             |                                      |               |

|            | LDA w/o DCC                                               | 9 600 B           | 1228 800 B                 | 1 200 B           | 153 600 B          | 153 600 B           |                                      |               |

|            | R/O time                                                  |                   |                            |                   |                    |                     |                                      |               |

|            |                                                           |                   |                            |                   |                    |                     |                                      |               |

|            | DCC                                                       | 8 640 B           | 1 105 920 B                | 1 080 B           | 138 240 B          | 138 240 B           |                                      |               |

|            | R/O time                                                  | 864 µs            | 110 592 µs                 | 108 µs            | 13 824 µs          | 13 824 µs           |                                      |               |

|            | LDA w/ DCC                                                | 86 400 B          | 11 059 200 B               | 10 800 B          | 1 382 400 B        | 1 382 400 B         |                                      |               |

|            | R/O time                                                  | 691 µs            | 88 474 μs                  | 86 µs             | 11 059 μs          | 11 059 μs           |                                      |               |

|            |                                                           |                   |                            |                   |                    |                     |                                      |               |

|            | ODR                                                       | 17 280 B          | 2 211 840 B                | 2 160 B           | 276 480 B          |                     |                                      |               |

|            | 1000MB/s                                                  | 17 µs             |                            |                   |                    |                     |                                      |               |

|            | Disk                                                      | 17 280 B          |                            | 2 160 B           |                    |                     |                                      |               |

|            | 170MB/s                                                   | 102 µs            | 13 011 μs                  | 13 µs             | 1 626 μs           | 1 626 μs            |                                      |               |

| Expected   | Max R/O time                                              | <b>3 072</b> μs   | <b>393 216</b> μs          | <b>384</b> μs     | <b>49 152</b> μs   | <b>49 152</b> μs    | "Oursel                              |               |

| speed      | Min Freq                                                  | 0,33 kHz          | 0,00 kHz                   | 2,60 kHz          | 0,02 kHz           | 0,02 kHz            | Overk                                | ill for RPC   |

|            | Min. evts Freq                                            |                   | 0,33 kHz                   |                   | 2,60 kHz           | 2,60 kHz            |                                      |               |

| V. Boudry  | DCC status and ∫ for the DHCAL — KNU, Daegu, 19 feb. 2009 |                   |                            |                   |                    |                     |                                      |               |

#### Summary

#### All HW component for the DAQ are now available

- some need extra prod (LDA, CCC)

- DCC is advancing well according to planning

- test prod this month (3 wks)

- FW: on-going everywhere

- DHCAL DIF OK for USB but needs integration of DIF-LDA blocks

- Effort of DIF Task force to write modular code on-going

- LDA & DCC in intensive development

- Protocol definition crystallising

- SW: Almost full skeleton working

- integration of HW started

- needs implementation in a real test bench with real objects (in part. ASICs) → @ UCL and LLR soon

- Good hope for full working system at end of spring → use in June TB ?

V. Boudry

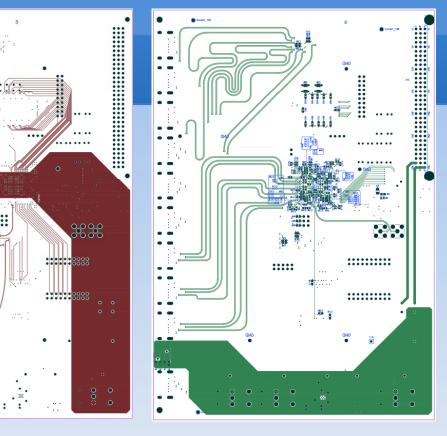

### **DCC pre-proto**

V. Boudry