# News from the 1m<sup>2</sup> GRPC SDHCAL

collection of slides from : Ch.Combaret, I.L, H.Mathez, J.Prast, N.Seguin, W.Tromeur, G.Vouters and many others

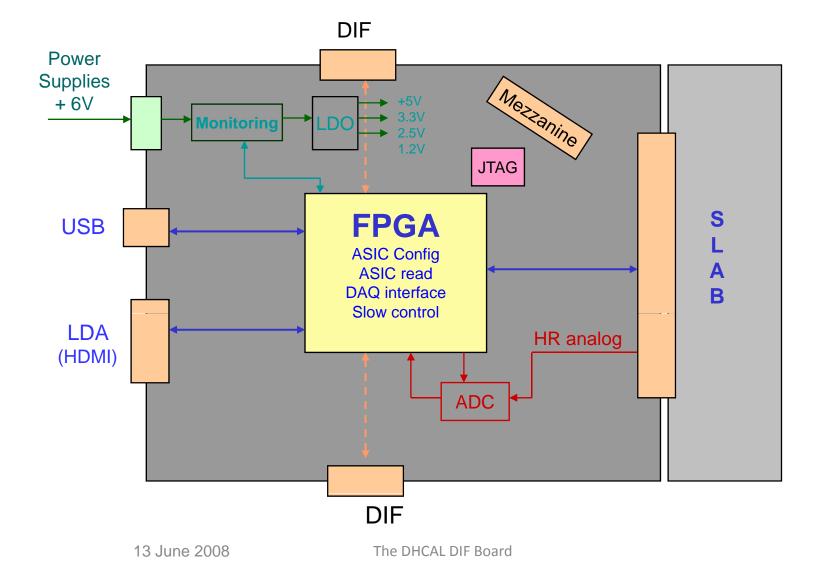

# The DHCAL DIF Board

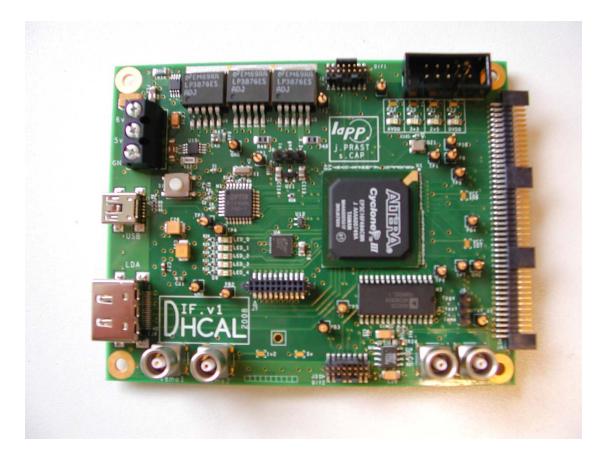

- Based on a Cyclone 3 Altera FPGA (EP3C6F484).

- Separated from the slab for more flexibility.

- Can handle slab what ever the nb of HardRoc on it.

- DIF task force interface compliant.

- MicroMegas and RPC detector compatible.

- HardRoc, Lyon's asics and also Spiroc and Skyroc compatible.

- On the DAQ side, interface with :

- The LDA (final DAQ).

- PC through USB for standalone tests and debugs.

- DIF neighbors.

- Interface with the analog DAQ removed.

## Architecture of the DIF Board

| GND             | 1              | 2  |

|-----------------|----------------|----|

| MUX3_CSn        | 3              | 4  |

| MUX2_CSn        | 5              | 6  |

| MUX1_CSn        |                | 8  |

| spare1          | 9              | 10 |

| MUX_ENN         | 11             | 12 |

| MUX_WRN         | 13             | 14 |

| spare2          | 15             | 16 |

| en_otaq         | 17             | 18 |

| GND             | 19             | 20 |

| SR_resiet       | 21             | 22 |

| hold            | 23             | 24 |

| spare3          | 25             | 26 |

| SR_IN           | 27<br>29<br>31 | 28 |

| spare4          | 29             | 30 |

| SR_OUT          | 31             | 32 |

| spare5          | 33             | 34 |

| SR_ck           | 35             | 36 |

| GND             | 37<br>39       | 38 |

| TransmitOn_3    |                | 40 |

| Pwr_analog      | 41             | 42 |

| TransmitOn_2    | 43             | 44 |

| Pwr_dac         | 45             | 48 |

| Pwr_ss/Pwr_sca  | 47             | 48 |

| GND             | 49             | 50 |

| TransmitOn_1    | 51             | 52 |

| Pwr_digital     | 53             | 54 |

| TransmitOn_0    | 55             | 56 |

| Pwr_adc         | 57             | 58 |

| SC_SROUT        | 59             | 60 |

| SC_SROUT_BYPASS | 61             | 62 |

| SC_select       | 63             | 64 |

| SC_ck           | 65             | 66 |

| User_LVDS_P     | 67             | 68 |

| Trig_Ext_P      | 69             | 70 |

| DVDD            | 71             | 72 |

| Ck_5MHz_0_P     | 73             | 74 |

| Ck_5MHz_1_P     | 75             | 78 |

| GND             | 77             | 78 |

| Clk_40MHz_0_P   | 79             | 80 |

| Clk_40MHz_1_P   | 81             | 82 |

| DVDD            | 83             | 84 |

| Raz_Chn_P       | 85             | 86 |

| Val_Evt_P       | 87             | 88 |

| AVDD            | 89             | 90 |

| 2        | GND                            |

|----------|--------------------------------|

| 4        | Analog_0                       |

| 6        | GND                            |

| 8        |                                |

| -        | Analog_1<br>GND                |

| 10       |                                |

| 12       | C_test                         |

| 14       | GND                            |

| 16<br>18 | MUX_A4                         |

|          | MUX_A3                         |

| 20       | MUX_A2                         |

| 22<br>24 | MUX_A1<br>MUX_A0               |

| 26       | Ramfullext                     |

| 28       | Reset_BCID                     |

|          |                                |

| 30<br>32 | GND<br>Resetn                  |

| 34       | Start_Conv_daqb                |

| 36       | Start_Conv_daqp                |

| 30       | End_Readout<br>Start_acq       |

| 40       | Start_acq<br>RamFull           |

| 40       | Dout_3                         |

| 44       | GND                            |

| 44       | Dout_2                         |

| 40       |                                |

| 50       | Start_Readout<br>Trig_ext      |

| 52       |                                |

| 54       | Start_Readout_Bypass<br>Dout_1 |

| 56       | GND                            |

| 58       | Dout_0                         |

| 60       | C CRIN RYPACE                  |

| 62       | SC_SRIN_BYPASS<br>SC_SRIN      |

| 64       | SC_reset                       |

| 66       | SC_load                        |

| 68       | User_LVDS_N                    |

| 70       | Trig_Ext_N                     |

| 72       | AVDD                           |

| 74       | Ck_5MHz_0_N                    |

| 76       | CIK_5MHz_1_N                   |

| 78       | GND                            |

| 80       | Clk_40MHz_0_N                  |

| 82       | Cik_40MHz_1_N                  |

| 84       | AVDD                           |

| 86       | Raz_Chn_N                      |

| 88       | Val_Evt_N                      |

| 90       | AVDD                           |

| 100      | AV DD                          |

# **SLAB** Interface

#### The connector has been designed for DHCAL but also ECAL or AHCAL

# So the DHCAL DIF can also be used for ECAL or AHCAL !

Samtec FSH/ SFMH 90 pin connector

# The DIF Board

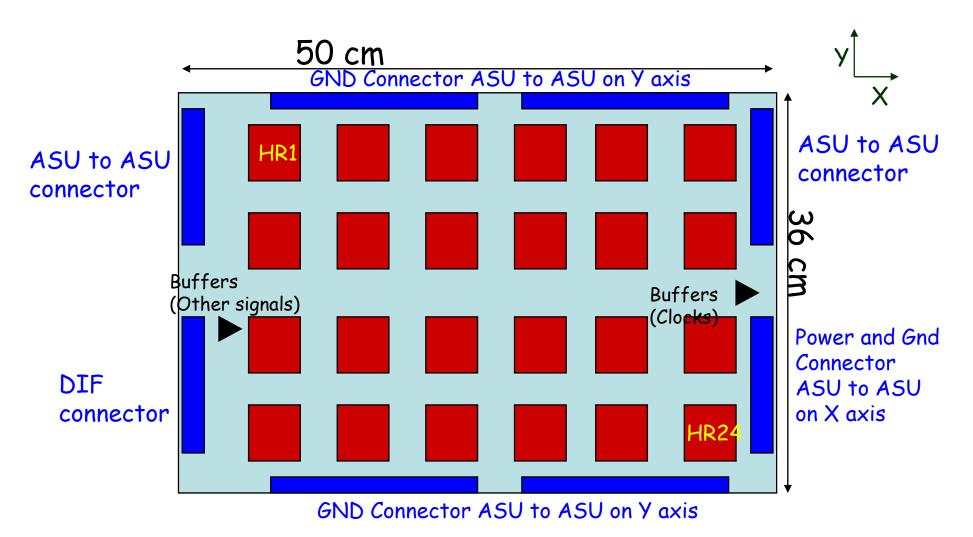

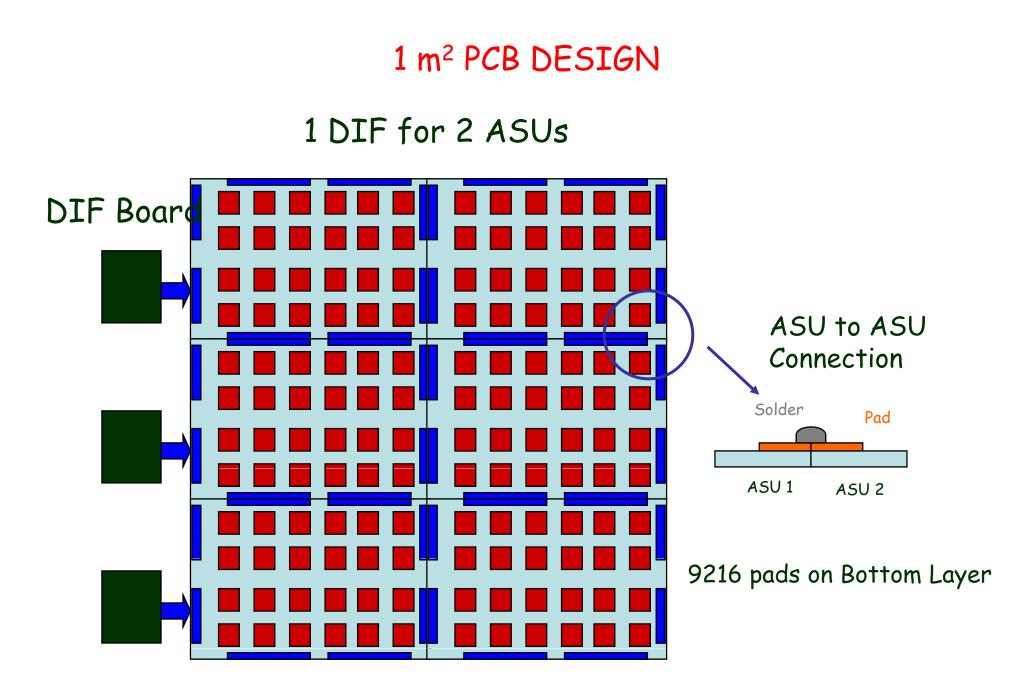

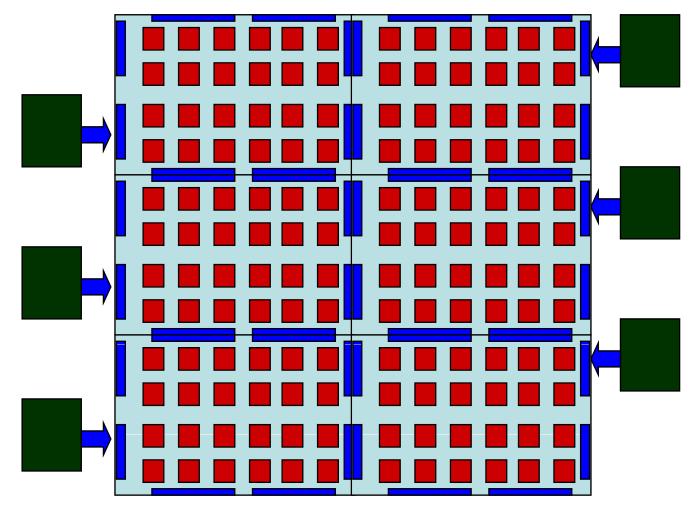

## 1 m<sup>2</sup> PCB MAIN SPECIFICATIONS

ASU PCB Design

- 24 x 64 1 sq cm pads

- 24 Hardrocs Asics chained

1 m2 PCB board :

- 6 ASUs

- 144 Hardroc Asics

DIF boards :

- 1 DIF for 1 ASU : 6 DIFs

- 1 DIF for 2 ASU : 3 DIFs

**Buffered Signals**

Analog Readout :

(Long Lines 1 m for Clock on 1 ASU):

- Slow Control

- Power\_on

- Control for Analog Readout

- Digital Readout

- All OUT\_Q are connected together

- EN\_OTAQ switch on or off using DIF board and decoder

#### ASU PCB DESIGN

Buried and Blind Vias (Same as the last PCB with 4 HR)

#### 1 m<sup>2</sup> PCB DESIGN

1 DIF for 1 ASUs

#### 1 m<sup>2</sup> PCB DESIGN (Layers)

- o Layer 1 (TOP) : interconnect

- o Layer 2 : interconnect

- o Layer 3 : 3.3V Digital

- o Layer 4 : GND

- o Layer 5: 3.5V Analog

- o Layer 6 : PADs to Hardroc

- o Layer 7 : GND

- o Layer 8 (BOTTOM) : PADs

Pads to Hardroc interconnects are the same for the entire PCB (hierarchical design)

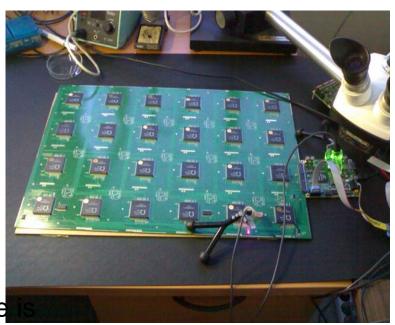

#### **Present Status**

- DIF command and register access use **XDAQ** software

- **DIF** is fully functionnal

- The tested slab is fully functionnal with following modifications :

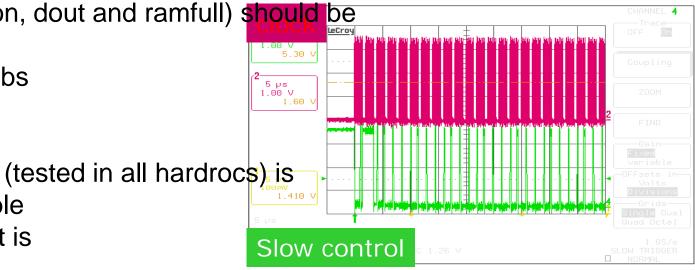

- 1. Use of buffers on the SLC clock line mandatory (max nb of hardrocs chained without buffer could not exceed 12)

- 2. Use of buffers on the Open drains readout lines

(transmit\_on, dout and ramfull) should be forseen 5.30

for next slabs

- Slow control (tested in all hardrocs) is stable and reliable

- Data readout is

**Present Status**

### What was tested :

- Numerical readout has been tested in the following modes :

- 1. Manual Start Acquisition/Manual Start Readout (Manual Trigger

- 2.Manual Start Acquisition/ Automatic Start Readout (Internal Trigger)

- 3.Automatic startAcquisition/ Automatic Start Readout (« Beam test mode

- -Both DIF firmware and XDAQ software stable and reliable

- -Both DIF Firmware and XDAQ software have been tested with trigger rate >1kHz and 128 events per trigger (DAQ levels < noise level)

- -DIF temperature and current consumption monitoring on all DIFs

#### **Present Status**

We have started tests with cosmics using one slab and step by step we will equip the 1M<sup>2</sup> GRP with the 6 slabs (all now equipped with tested HR1)

We hope the fully equipped 1M<sup>2</sup> GRPC will be running very soon