# **DIF Command Interface**

# The DIF developers

# **0** Introduction

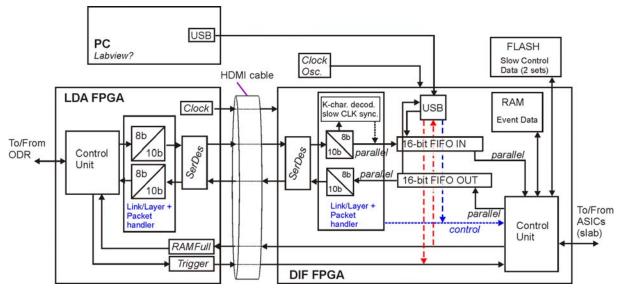

A simplified block diagram of the communication between DIF and LDA, or as it is proposed to a PC via USB bus, is shown in Fig. 1. Only the interface between LDA and DIF is shown, the remaining functionalities are combined on DIF- and LDA-side in the blocks "Control Unit". The USB-DIF link is generally for debugging, but as the more simple interface, it will be the first system realization stage as well. Data transfer between LDA and the slabs (front-end ASICs) might happen in two steps (by two commands from the LDA), for example the slow-control data: 1. Load slow-control data from LDA to DIF (data is stored in DIF memory). 2. Transfer data from the memory to the slabs (ASICs).

#### 0.1 LDA-DIF interface

The only connection between LDA and DIF is realized with a 19-pin HDMI cable. Commands are in general 8b/10b-channel coded, while the coding and decoding blocks are fully transparent for the remaining logic/electronics. The DIF is operated with the clock from the LDA: no PLL (DCM) on the DIF, by which a fully synchronous operation of all the DIFs that are connected to one LDA is guaranteed. Clock speed (default): 100MHz (but also possible: 40-120MHz). Fast Commands from the LDA to the DIF like a trigger are transported without channel coding, as well as fast commands from DIF to the LDA like the signal "RAMFull".

### 0.2 PC (USB) to DIF interface

The USB interface should "emulate" the LDA-DIF interface as much as possible in order to allow an easy switching to the LDA-DIF setup. The USB-interface does not use the 8b/10b channel coders/decoders. The DIF clock may be generated from the USB side or by a local oscillator. In the USB-setup, PLLs (DCMs) within the DIF FPGA are allowed. On the PC, Labview is a possible operating system, but not mandatory.

Figure 1: Interface of the DIF FPGA to the LDA, or a PC via USB

# 1 Transfer between LDA and DIF

The data transfer between LDA and DIF is 8b/10b channel coded. The 8b/10b coding is realized by a 5b/6b and a 3b/4b coder.

Two types of data transfer "frames" are defined between LDA and DIF [1, 2]:

### 1.1 (Fast-) Command Frames

The Fast-Commands are used for link-synchronization and for timing critical DIF commands (especially broadcasts to all DIFs) only.

A command frame is 16-bit long:

| 15 8                | 7 0              |

|---------------------|------------------|

| komma character (K) | command word (D) |

The komma character K and the command word D are referenced to by KX.Y and DX.Y, respectively: X has a **5-bit resolution**, Y has a **3-bit resolution**. E.g. K28.1 is the 8-bit sequence 11100 001.

#### **1.2 Block Transfers**

A block transfer is used to transmit configuration-, result- or status information data between LDA and DIF as well as timing-uncritical commands. The length is not fixed, although only an even number of 16-bit words is allowed (see K23.7 in Table 1 and /EPD/ in Table 2). The block:

| packettype | pktID  | type_modifier<br>(command def.) | data_length | data                   | CRC    |

|------------|--------|---------------------------------|-------------|------------------------|--------|

| 16 bit     | 16 bit | 16 bit                          | 16 bit      | data_length<br>*16 bit | 16 bit |

packettype: define block to be:

| packettype (16-bit hex) | identifies packet to be     | remark                  |

|-------------------------|-----------------------------|-------------------------|

| 0x0001                  | block data                  |                         |

| 0x0002                  | generic command             |                         |

| 0x0010                  | command ECAL only           |                         |

| 0x0020                  | command DHCAL only          |                         |

| 0x0040                  | command AHCAL only          |                         |

| 0x0080                  | Command is for DIF-DIF Link |                         |

| 0x0100                  | data is firmware for FPGA   |                         |

| 0x1000 to 0xF000        | DCC identifier              | only the upper 4 bits!! |

Each packet identifier (second column) is assigned to a certain bit in the 16-bit packettype (first column). The bits can be combined: e.g. packettype=0x0012 means "generic command for ECAL only".

**pktID:** numeration of sent blocks, used to identify block losses.

**type\_modifier:** command definition. In practise, this is the address of the respective command register inside the DIF. See table 8.

data\_length: Number of 16-bit vectors sent in the "data"-section of the block.

data: 16-bit data vectors, e.g. slow-control data for the ASICs, temperatures, voltages, currents.

CRC: cyclic redundancy check (look for transmission errors).

# 1.3 Komma Characters (see section 1.1) and special sequences [1]

The 8b/10b channel coding allows for channel synchronization and maintenance the so called komma characters (K):

| Komma Character K | Task (Meaning)                                                     |

|-------------------|--------------------------------------------------------------------|

| K28.0             | Signals the next symbol (command word) is a SYNCCMD.               |

| K28.1             |                                                                    |

| K28.2             |                                                                    |

| K28.3             | Signals the next symbol (command word) is a COMMAND.               |

| K28.4             | Signals in the next symbol (command word) is for DIF-DIF link      |

| K28.5             | reserved for link synchronization                                  |

| K28.6             |                                                                    |

| K28.7             | reserved for link synchronization                                  |

| K23.7             | Carrier Extend. Used to PAD the end of a data frame out to an even |

|                   | number of Symbols, so that next frame, or IDLE sequence starts on  |

|                   | an even footing. / <b>R</b> /                                      |

| K27.7             | Start of data frame /S/                                            |

| K29.7             | End of data frame <b>/T</b> /                                      |

| K30.7             |                                                                    |

### Table 1: Komma Characters

Several special sequences are defined:

| Set         | Sequence         | Comment                                                |

|-------------|------------------|--------------------------------------------------------|

| /I1/        | /K28.5/D5.6/     | Idle sequence, sent when running DP is +, flips it to  |

|             |                  | Sent automatically.                                    |

| /I2/        | /K28.5/D16.2/    | Idle sequence, sent when running DP is -, maintains it |

|             |                  | as Sent automatically.                                 |

| /EPD/       | /T/R/ or /T/R/R/ | Used to end a data frame, the addition of an extra /R/ |

|             |                  | is used to pad things out to an even number.           |

| /LOOP/      | /K28.5/D12.6/    | Low-level link loop back start (DON'T SEND from        |

|             |                  | User-Logic)                                            |

| /ENDLOOP/   | /K28.5/D16.7/    | Low-level link loop back end (DON'T SEND from          |

|             |                  | User-Logic)                                            |

| /LINKSTART/ | /K28.5/D1.4/     | Link Start. (DON'T SEND from User-Logic)               |

| /LINKACK/   | /K28.5/D30.3/    | Link Start ACK. (DON'T SEND from User-Logic)           |

**Table 2: Special Sequences**

# 2 DIF Commands (from LDA or USB to DIF FPGA)

The commands are subdivided into:

- timing critical commands (see table 3), sent with "FAST command frames" (see section 1.1)

- timing uncritical signals (see table 8) that are sent with "BLOCK transfers (see section 1.2).

For each command that is sent from LDA to DIF, the DIF has a dedicated **command register**. The address of this **command register** is defined:

- for FAST\_Commands by the X in the incoming DX.Y command word (see section 1.1)

- for **Block-Transfers** by the type\_modifier (see section 1.2).

Command registers are 16-bit, and can be subdivided for several functional purposes.

#### The general notation is:

| 15 | 10       | 9 5              | 4      | 3      | 2      | 1      | 0      |

|----|----------|------------------|--------|--------|--------|--------|--------|

|    | Reserved | Status Bits(4:0) | Bit    | Bit    | Bit    | Bit    | Bit    |

|    | R, +0    | RC, +10100       | RW, +0 | RS, +0 | RW, +0 | RW, +0 | RW, +0 |

**Note:** R = Readable by the LDA,

W = Writeable by the LDA,

C = Clearable by the LDA,

S = Settable by the LDA,

+x = Value undefined after reset,

+0 = Value is 0 after reset,

+1 = Value is 1 after reset,

### 2.1 FAST Commands

| FAST Command    | komma      | command       | Operation                        | Change            |  |  |

|-----------------|------------|---------------|----------------------------------|-------------------|--|--|

| see section 1.1 | character  | word D        |                                  | <b>DIF State?</b> |  |  |

| reset_BCID      | K28.3      | D1.1          | reset BCID                       | no                |  |  |

| start_acquire   | K28.3      | D2.1          | start data-taking (int. trig)    | yes               |  |  |

|                 |            | D2.2          | start data-taking (ext. trigger) |                   |  |  |

|                 |            | D2.3          | stop data-taking                 |                   |  |  |

| stop_readout    | K28.3      | D3.1          | stop data transfer DIF=>LDA      | no                |  |  |

|                 |            | D3.2          | continue data transfer           |                   |  |  |

|                 | ##         | ## ECAL spec  | eific ####                       |                   |  |  |

|                 | K28.3      | D5.0          |                                  |                   |  |  |

|                 | ###        | # DHCAL spe   | cific ####                       |                   |  |  |

|                 | K28.3 D8.0 |               |                                  |                   |  |  |

|                 | ###        | # AHCAL spe   | cific ####                       |                   |  |  |

| calibrate       | K28.3      |               | do a calibration run:            | yes               |  |  |

|                 |            | D11.1         | with light sys., int. trig       |                   |  |  |

|                 |            | D11.2         | with charge sys., int. trig      |                   |  |  |

|                 |            | D11.3         | with light sys., ext. trig.      |                   |  |  |

|                 |            | D11.4         | with charge sys., ext. trig.     |                   |  |  |

|                 | ##         | ## DCC identi | fier ####                        |                   |  |  |

|                 | K28.3      | D15.0         |                                  |                   |  |  |

Table 3: FAST Commands (timing critical and broadcasts) from LDA to DIF

# ECAL specific (D5.0 – D7.7), DHCAL specific (D8.0 – D10.7), AHCAL specific (D11.0 – D13.7), DCC identifier (D15.0-D17.7)

#### 2.1.1 reset\_BCID, FAST-command, set by D1.1

| 15 1     | 0            |

|----------|--------------|

| reserved | BCID_counter |

| +0       | S, +0        |

| Bit no. | Bit Field    | Description                                                                                                                                                                                                                                            |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 1  | reserved     | reserved                                                                                                                                                                                                                                               |

| 0       | BCID_counter | RESET the BCID (bunch counter) synchronously for all<br>DIFs (broadcast command):<br>reset_BCID = '1': reset is active for 4 clock cycles,<br>afterwards the DIF resets this bit automatically (set by D1.1)<br>reset_BCID = '0': reset is not active. |

#### Table 4: reset\_BCID register description

This register cannot be read from the LDA. A status bit of this command is in the general register (see section 2.2.2).

#### 2.1.2 start\_acquire, FAST-command, set by D2.Y

| 15 3     | 2     | 1         | 0         |

|----------|-------|-----------|-----------|

| reserved | stop  | start_ext | start_int |

| +0       | S, +0 | S, +0     | S, +0     |

| Bit no. | Bit Field                               | Description                                                                 |

|---------|-----------------------------------------|-----------------------------------------------------------------------------|

| 15 2    | h a a a a a a a a a a a a a a a a a a a | and a second                                                                |

| 15 – 3  | reserved                                | reserved                                                                    |

| 2       | stop                                    | stop data-taking synchronously for all DIFs (broadcast command):            |

|         |                                         | stop = '1': data taking is stopped (set by $D2.3$ )                         |

|         |                                         | stop is reset by the DIF automatically after executing the                  |

|         |                                         | command.                                                                    |

|         |                                         | stop='0': no action                                                         |

| 1       | start_ext                               | start data-taking synchronously for all DIFs (broadcast                     |

|         |                                         | command) with <u>external</u> trigger:                                      |

|         |                                         | $\underline{\text{start}} = 1^{\circ}$ data taking is started (set by D2.2) |

|         |                                         | start_ext is reset by the DIF automatically after executing the             |

|         |                                         | command. Puts DIF into "ACTIVE" mode.                                       |

|         |                                         | start ext='0': no action                                                    |

| 0       | start_int                               | start data-taking synchronously for all DIFs (broadcast                     |

|         |                                         | command) with <u>internal trigger</u> :                                     |

|         |                                         | <u>start_int = '1'</u> : data taking is started (set by D2.1)               |

|         |                                         | start_int is reset by the DIF automatically after executing the             |

|         |                                         | command. Puts DIF into "ACTIVE" mode.                                       |

|         |                                         | <u>start_int='0':</u> no action                                             |

Table 5: start\_acquire register description

This register cannot be read from the LDA. Status bits of this command is in the general register (see section 2.2.X).

## 2.1.3 stop\_readout, FAST-command, set by D3.Y

| 15 2     | 1        | 0     |

|----------|----------|-------|

| reserved | CONTINUE | STOP  |

| +0       | S, +0    | S, +0 |

| Bit no. | Bit Field | Description                                                |

|---------|-----------|------------------------------------------------------------|

|         |           |                                                            |

| 15 - 2  | reserved  | reserved                                                   |

| 1       | CONTINUE  | continue readout synchronously for all DIFs (broadcast     |

|         |           | command):                                                  |

|         |           | CONTINUE = '1': readout is continued (set by D3.2)         |

|         |           | CONTINUE is reset by the DIF automatically after executing |

|         |           | the command.                                               |

|         |           | CONTINUE='0': no action                                    |

| 0       | STOP      | stop readout synchronously for all DIFs (broadcast         |

|         |           | command):                                                  |

|         |           | STOP = '1': readout is stopped (set by D3.1)               |

|         |           | STOP is reset by the DIF automatically after executing the |

|         |           | command.                                                   |

|         |           | STOP='0': no action                                        |

Table 6: stop\_readout register description

# 2.1.4 calibrate, FAST command, set by D11.Y, AHCAL specific

| 15 4     | 3      | 2      | 1      | 0      |

|----------|--------|--------|--------|--------|

| Reserved | CALIB3 | CALIB2 | CALIB1 | CALIB0 |

| +0       | S, +0  | S, +0  | S, +0  | S, +0  |

| Bit no. | Bit Field | Description                                                                                                                                                                                                                                                                                                        |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 4  | reserved  | reserved                                                                                                                                                                                                                                                                                                           |

| 3       | CALIB3    | start a calibration run synchronously for all DIFs (broadcast<br>command) <u>with charge injection, external trigger:</u><br>CALIB3 = '1': data taking is started (set by D11.4)<br>CALIB3 is reset by the DIF automatically after executing the<br>command. Puts DIF into "ACTIVE" mode.<br>CALIB3='0': no action |

| 2       | CALIB2    | start a calibration run synchronously for all DIFs (broadcast<br>command) <u>with LEDs, external trigger:</u><br>CALIB2 = '1': data taking is started (set by D11.3)<br>CALIB2 is reset by the DIF automatically after executing the<br>command. Puts DIF into "ACTIVE" mode.<br>CALIB2='0': no action             |

| 1       | CALIB1    | start a calibration run synchronously for all DIFs (broadcast<br>command) <u>with charge injection, internal trigger:</u><br>CALIB1 = '1': data taking is started (set by D11.2)                                                                                                                                   |

| Bit no. | Bit Field | Description                                                                                                                                                                                                                                                                                            |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | CALIB1 is reset by the DIF automatically after executing the command. Puts DIF into "ACTIVE" mode.<br>CALIB1='0': no action                                                                                                                                                                            |

| 0       | CALIBO    | start a calibration run synchronously for all DIFs (broadcast<br>command) <u>with LEDs, external trigger:</u><br>CALIB0 = '1': data taking is started (set by D11.1)<br>CALIB0 is reset by the DIF automatically after executing the<br>command. Puts DIF into "ACTIVE" mode.<br>CALIB0='0': no action |

#### Table 7: calibrate register description (AHCAL specific)

This register cannot be read from the LDA. Status bits of this command is in the general register (see section 2.2.X).

# 2.2 BLOCK TRANSFER address map

| Bock Transfer    | type_modifier  | data    | Operation                           | Change                                  |

|------------------|----------------|---------|-------------------------------------|-----------------------------------------|

| Name (command)   | (command def.) | 16-bit  |                                     | DIF                                     |

| see section 1.2  | 16-bit hex     | hex     |                                     | State?                                  |

| power_on         | 0x0002         | 0x0000  | turn power regulators off           | yes                                     |

| •                |                | 0x0001  | turn power regulators on            | , i i i i i i i i i i i i i i i i i i i |

|                  |                | 0x0002  | automatic: controlled by DIF        |                                         |

|                  |                | 0x1000  | read power register                 |                                         |

| reset            | 0x0004         | 0x0001  | reset of DIF                        | yes                                     |

|                  |                | 0x0002  | reset of slab                       | -                                       |

|                  |                | 0x0004  | reset all                           |                                         |

|                  |                | 0x0008  | reset slow-control registers        |                                         |

|                  |                | 0x1000  | read reset register                 |                                         |

| set_DIF_mode     | 0x0006         | 0x0001  | set detector into "SLEEP"           | yes                                     |

|                  |                | 0x0002  | set detector into "READY"           |                                         |

|                  |                | 0x1000  | read DIF_mode register              |                                         |

| power_pulsing    | 0x0008         | 0x0001  | turn pwr_analog <mark>ON</mark>     | no                                      |

|                  |                | 0x0002  | turn pwr_digital <mark>ON</mark>    |                                         |

|                  |                | 0x0004  | turn pwr_ss/pwr_sca <mark>ON</mark> |                                         |

|                  |                | 0x0008  | turn pwr_adc <mark>ON</mark>        |                                         |

|                  |                | 0x0010  | turn pwr_dac <mark>ON</mark>        |                                         |

|                  |                | 0x0020  | turn all <mark>ON</mark>            |                                         |

|                  |                | 0x1000  | read power_pulsing register         |                                         |

| transfer_sc_data | 0x000A         | sc_data | load data from LDA to DIF           | yes                                     |

|                  |                |         | (n data vectors)                    |                                         |

|                  |                | 0x1000  | read transfer_sc_data reg.          |                                         |

|                  |                |         | (1 data vector)                     |                                         |

| load_sc_data     | 0x000C         | 0x0001  | load set1_0 from DIF to slab1       | yes                                     |

|                  |                | 0x0101  | load set1_1 from DIF to slab1       |                                         |

|                  |                | 0x0002  | load set2_0 from DIF to slab2       |                                         |

|                  |                | 0x0102  | load set2_1 from DIF to slab2       |                                         |

|                  |                | 0x0004  | load set3_0 from DIF to slab3       |                                         |

|                  |                | 0x0104  | load set3_1 from DIF to slab3       |                                         |

|                  |                | 0x0008  | load set4_0 from DIF to slab4       |                                         |

|                  |                | 0x0108  | load set4_1 from DIF to slab4       |                                         |

| Bock Transfer         | type_modifier  | data             | Operation                          | Change      |

|-----------------------|----------------|------------------|------------------------------------|-------------|

| Name (command)        | (command def.) | 16-bit           | operation                          | DIF         |

| see section 1.2       | 16-bit hex     | hex              |                                    | State?      |

|                       | 10-ont nex     | 0x0080           | readback all sets from DIF         | State.      |

|                       |                | 0x0000<br>0x1000 | read load_sc_data reg.             |             |

| read_results          | 0x000E         | 0x1000           | read data slab via DIF to LDA      | yes         |

| read_results          | ONOUCL         | 0x1000           | read read_results reg.             | <i>y</i> es |

| set_control_reg       | 0x0010         | 16-bit           | set control register               | no          |

|                       | 0110010        | control-         |                                    |             |

|                       |                | register         |                                    |             |

| read_status_control   | 0x0012         | 0x0001           | readout of DIF control register    | no          |

|                       |                | 0x0002           | readout of DIF status1 register    |             |

|                       |                | 0x0003           | readout of DIF status2 register    |             |

| readout_info          | 0x0014         | 0x0001           | read DIF firmware date             | no          |

| _                     |                | 0x0002           | read DIF firmware version          |             |

|                       |                | 0x0004           | read board's production date       |             |

|                       |                | 0x0008           | read DIF board-ID                  |             |

|                       |                | 0x0010           | read board's version number        |             |

|                       |                | 0x0020           | read DIF serial number             |             |

|                       |                | 0x0040           | readout all infos                  |             |

| FPGA_firmware         | 0x0018         | firmware         | load data from LDA to DIF          | no          |

|                       |                | -data            | (n data vectors)                   |             |

|                       |                | 0x1000           | read transfer_sc_data reg.         |             |

|                       |                |                  | (1 data vector)                    |             |

| sel_command_input     | 0x001A         | 0x0000           | LDA-DIF link is used               | no          |

|                       |                | 0x0001           | DIF-DIF link is used               |             |

|                       |                | 0x0002           | reset input selection logic        |             |

|                       |                | 0x1000           | read sel_ command_input reg.       |             |

| pre_spill_indication  | 0x001C         | 0x0001           | indicates an upcoming              | yes         |

|                       |                |                  | "start_acquire"                    |             |

|                       |                | 0x1000           | read pre_spill_ind. register       |             |

|                       |                |                  | •                                  |             |

|                       | 0x0030         | ECAL specif      | 1C ####                            |             |

|                       |                | HCAL speci       | fic ####                           |             |

|                       | 0x0050         |                  |                                    |             |

|                       |                | HCAL speci       | fic ####                           |             |

| read_temp_power       | 0x0070         | 0x0000           | temp/power sensor readout:         | yes         |

|                       |                | 0x0001           | read temp. results $\mu C$ to DIF  |             |

|                       |                | 0x0002           | temp. results DIF to LDA           |             |

|                       |                | 0x0003           | read volt./currents $\mu C$ to DIF |             |

|                       |                | 0x0004           | volt./currents DIF to LDA          |             |

|                       |                | 0x1000           | read temp_power register           |             |

| read_calibrate_status | 0x0072         | 0x1000           | read calibration status register   | no          |

| load_calib_settings   | 0x0074         | calib_dat        | Set DACs (pulse heights) and       | no          |

|                       |                | а                | delay regs. of the calibration     |             |

| 1 111 1               | 0.0075         | n*16-bits        | system:                            |             |

| read_calib_settings   | 0x0076         | 0x0001           | Read current settings              | no          |

| 1 . 1                 | 0.0070         | 0x1000           | read calib_analog register         |             |

| readout_probe_regs    | 0x0078         | 0x0001           | Read ASICs probe regs              | yes         |

| 0.6                   | 0.007.1        | 0x1000           | read probe_regs register           |             |

| uC_firmware           | 0x007A         | controller       | load new $\mu$ C software          | no          |

|                       |                | data             | (see also: packettype)             |             |

|                       |                | n*16-bits        |                                    |             |

#### Table 8: Block transfers between LDA and DIF

type\_modifier:

ECAL specific (0x0030-0x004F), DHCAL specific (0x0050-0x006F), AHCAL specific (0x0070 – 0x008F)

<u>Change DIF State (last column table 3 and table 8) means:</u> If the DIF changes its state from "IDLE" to any other state by a received command, the respective operation should not be interrupted by following commands except for emergencies or resets. After completion of the tasks, the DIF changes back to "IDLE" automatically and is ready for new commands.

#### 2.2.1 power\_on, BLOCK Transfer command, address 0x0002

| 15 2     | 1         | 0          |

|----------|-----------|------------|

| reserved | automatic | slab_power |

| R, +0    | RW, +0    | RW, +0     |

| Bit no. | Bit Field  | Description                                                                                                                                                                                                                             |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 2  | reserved   | reserved                                                                                                                                                                                                                                |

| 1       | automatic  | <pre>automatic = '1': power signals (c.f. section 2.2.4) are<br/>controlled by DIF. slab_power has to be at '1' for automatic<br/>operation.<br/>automatic = '0': no action<br/>automatic is reset when slab_power is set to '0'.</pre> |

| 0       | slab_power | Switch on or off slab power:<br>slab_power = '1': slab power is on (set by data=0x0001)<br>slab_power = '0': slab power is off (set by data=0x0000)                                                                                     |

Table 9: power\_on register description

#### 2.2.2 reset, BLOCK Transfer command, address 0x0004

| 15 5     | 4          | 3        | 2         | 1          | 0         |

|----------|------------|----------|-----------|------------|-----------|

| reserved | reset_BCID | reset_SC | reset_all | reset_slab | reset_DIF |

| R, +0    | R, +0      | RS, +0   | RS, +0    | RS, +0     | RS, +0    |

| Bit no. | Bit Field  | Description                                                      |

|---------|------------|------------------------------------------------------------------|

| 15 – 4  | reserved   | reserved                                                         |

| 4       | reset_BCID | Reset bunch counters of the ASICs, set by FAST Command           |

|         |            | (see section 2.1.1), read only.                                  |

|         |            | reset_BCID = '1': reset is active for 4 clock cycles,            |

|         |            | reset_BCID = '0': reset is not active.                           |

| 3       | reset_SC   | reset of the slow control registers of the ASICs:                |

|         |            | reset_SC = '1': reset active for 6 clock cycles, afterwards the  |

|         |            | DIF resets this bit automatically (set by data=0x0008)           |

|         |            | $reset_SC = '0'$ : reset not active.                             |

| 2       | reset_all  | general reset of DIF and slab electronics:                       |

|         |            | reset_all = '1': reset active for 6 clock cycles, afterwards the |

|         |            | DIF resets this bit automatically (set by data=0x0004)           |

|         |            | $reset_all = '0'$ : reset not active.                            |

| Bit no. | Bit Field  | Description                                                                                                                                                                                      |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | reset_slab | reset of slab electronics:<br>reset_slab = '1': reset active for 6 clock cycles, afterwards<br>the DIF resets this bit automatically (set by data=0x0002)<br>reset_slab = '0': reset not active. |

| 0       | reset_DIF  | reset of DIF electronics:<br>reset_DIF = '1': reset active for 6 clock cycles, afterwards<br>the DIF resets this bit automatically (set by data=0x0001)<br>reset_DIF = '0': reset not active.    |

Table 10: Reset register description

## 2.2.3 DIF\_mode BLOCK Transfer command, address 0x0006

| 15 | 7        | 6 4               | 3     | 2      | 1      | 0      |

|----|----------|-------------------|-------|--------|--------|--------|

|    | Reserved | current_mode(2:0) | LOO   | P SYNC | READY  | SLEEP  |

|    | R, +0    | R, +000           | R, +0 | R, +0  | RS, +0 | RS, +0 |

| Bit no. | Bit Field    | Description                                                                                                                                                                                                                                              |

|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 7  | reserved     | reserved                                                                                                                                                                                                                                                 |

| 6 - 4   | current_mode | Shows the actual mode, the DIF is in, defined by the last<br>"DIF_mode" command from the LDA (read-only):<br>current_mode = '000' DIF is in SLEEP mode,<br>current_mode = '001' DIF is in IDLE mode,<br>current_mode = '010' DIF is in SYNC mode,        |

| 2       | LOOD         | current_mode = '011' DIF is in LOOP mode                                                                                                                                                                                                                 |

| 3       | LOOP         | puts DIF into LOOP mode (debugging)<br>LOOP = '1' : DIF is in LOOP mode with LDA, after<br>accepting, the DIF resets this bit automatically and<br>'current_mode is set to '011' (set by FAST Command)<br>LOOP = '0' : no mode change                    |

| 2       | SYNC         | puts DIF into SYNC mode (DIF synchronization)<br>SYNC = '1' : DIF is in SYNC mode, after accepting, the DIF<br>resets this bit automatically and 'current_mode is set to '010'<br>(set by FAST Command)<br>SYNC = '0' : no mode change                   |

| 1       | READY        | puts DIF into IDLE mode (general wait and ready state):<br>IDLE = '1' : DIF is in IDLE mode, after accepting, the DIF<br>resets this bit automatically and 'current_mode is set to '001'<br>(set by data = 0x0002)<br>IDLE = '0' : no mode change        |

| 0       | SLEEP        | puts DIF into SLEEP mode (powered-down wait state)<br>SLEEP = '1' : DIF is in SLEEP mode with LDA, after<br>accepting, the DIF resets this bit automatically and<br>'current_mode is set to '000' (set by data = 0x0001)<br>SLEEP = '0' : no mode change |

Table 11: DIF\_mode register description

### 2.2.4 power\_pulsing BLOCK Transfer command, address 0x0008

This command is for debugging only. The power pulsing control should be done automatically by the DIF in order to guarantee a timing-precise switching. E.g., on a "start\_acquire"-command from the LDA, the DIF switches-on the slab before starting the data-taking.

| 15  | 6     | 5      | 4      | 3      | 2      | 1       | 0      |

|-----|-------|--------|--------|--------|--------|---------|--------|

| Res | erved | SLAB   | DAC    | ADC    | SS_SCA | DIGITAL | ANALOG |

| R   | , +0  | RW, +0 | RW, +0 | RW, +0 | RW, +0 | RW, +0  | RW, +0 |

| Bit no. | Bit Field | Description                                                |

|---------|-----------|------------------------------------------------------------|

|         |           |                                                            |

| 15 – 6  | reserved  | reserved                                                   |

| 5       | SLAB      | Switch the power of the complete slab, namely the power-   |

|         |           | pulsing control signals: pwr_analog, pwr_digital,          |

|         |           | pwr_ss/pwr_sca, pwr_adc, pwr_dac.                          |

|         |           | SLAB = '1' SLAB is switched ON (set by data = 0x0020)      |

|         |           | SLAB = '0' SLAB is switched OFF                            |

| 4       | DAC       | $DAC = '1' pwr_dac$ is switched ON (set by data = 0x0010)  |

|         |           | $DAC = '0' pwr_dac$ is switched OFF                        |

| 3       | ADC       | $ADC = '1' pwr_adc$ is switched ON (set by data = "0x0008) |

|         |           | $ADC = '0' pwr_adc$ is switched OFF                        |

| 2       | SS_SCA    | SS_SCA = '1' pwr_ss/pwr_sca is switched ON (set by         |

|         |           | data = 0x0004)                                             |

|         |           | SS_SCA = '0' pwr_ss/pwr_sca is switched OFF                |

| 1       | DIGITAL   | DIGITAL = '1' pwr_digital is switched ON (set by           |

|         |           | data = 0x0002)                                             |

|         |           | DIGITAL = '0' pwr_digital is switched OFF                  |

| 0       | ANALOG    | ANALOG = '1' pwr_analog is switched ON (set by             |

|         |           | data = $0x0001$ )                                          |

|         |           | ANALOG = '0' pwr_analog is switched OFF                    |

Table 12: power\_pulsing register description

#### 2.2.5 transfer\_sc\_data, BLOCK Transfer command, address 0x000A

| 15 2     | 1     | 0       |

|----------|-------|---------|

| reserved | CRC   | LDA_DIF |

| R, +0    | R, +0 | RS, +0  |

| Bit no. | Bit Field | Description                                                |

|---------|-----------|------------------------------------------------------------|

| 15 – 2  | reserved  | reserved                                                   |

| 1       | CRC       | CRC = '1' CRC-check ok for last LDA-DIF data transfer      |

|         |           | CRC = '0' transmission errors in current data set          |

| 0       | LDA_DIF   | LDA_DIF = '1' slow-control data is transferred from LDA to |

|         |           | DIF (set by data = $0x0001$ ). Bit is reset by DIF after   |

|         |           | completition automatically.                                |

|         |           | $LDA_DIF = '0'$ no action                                  |

#### Table 13: transfer\_sc\_data register description

By this command, all slow\_control configuration data sets that are stored in the Flash memory of the DIF are overwritten. The first 16-bit data block arriving with the block transfer is stored @ the base address of the Flash memory. See section 2.3.

| 15 9        | 8      | 7        | 6 4      | 3      | 2      | 1      | 0      |

|-------------|--------|----------|----------|--------|--------|--------|--------|

| STATUS[6:0] | SET    | READBACK | reserved | SLAB4  | SLAB3  | SLAB2  | SLAB1  |

| R, +0       | RW, +0 | RS, +0   | R, +0    | RS, +0 | RS, +0 | RS, +0 | RS, +0 |

| Bit no. | Bit Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 9  | STATUS[6:0] | <pre>if the slabs (partitions) are programmed twice with sc_data,<br/>the readback data can be used to identify problems.<br/>STATUS[6:4]: reserved for later use<br/>STATUS[3] = '1': sc_programming slab4 does not work<br/>STATUS[3] = '0': sc_programming slab4 ok<br/>STATUS[2] = '1': sc_programming slab3 does not work<br/>STATUS[2] = '0': sc_programming slab3 ok<br/>STATUS[1] = '1': sc_programming slab2 does not work<br/>STATUS[1] = '0': sc_programming slab2 does not work<br/>STATUS[1] = '0': sc_programming slab2 ok<br/>STATUS[0] = '1': sc_programming slab1 does not work<br/>STATUS[0] = '0': sc_programming slab1 does not work</pre> |

| 8       | SET         | defines which sc-data set shall be used for slab (partition):<br>SET = '0' <u>default</u> configuration is used<br>SET = '1' alternative configuration is used<br>See section 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7       | READBACK    | LDA reads back the slow-control data currently stored in the<br>DIF Flash memory. Bit is reset by DIF after completion.<br>LDA_readback = '1' readback is active (set by data =<br>0x0100)<br>LDA_readback = '0' no action                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6 - 4   | reserved    | can be used to define more partitions if needed later                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3       | SLAB4       | SLAB4 = '1' configure slab3 (partition3) with the sc-data set<br>defined by 'SET'. Bit is reset by DIF after completion. (set<br>by data = 0x0008)<br>SLAB4 = '0' no action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2       | SLAB3       | SLAB3 = '1' configure slab3 (partition3) with the sc-data set<br>defined by 'SET'. Bit is reset by DIF after completion. (set<br>by data = 0x0004)<br>SLAB3 = '0' no action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1       | SLAB2       | SLAB2 = '1' configure slab3 (partition3) with the sc-data set<br>defined by 'SET'. Bit is reset by DIF after completion. (set<br>by data = 0x0002)<br>SLAB2 = '0' no action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0       | SLAB1       | SLAB1 = '1' configure slab3 (partition3) with the sc-data set<br>defined by 'SET'. Bit is reset by DIF after completion. (set<br>by data = 0x0001)<br>SLAB1 = '0' no action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### 2.2.6 load\_sc\_data, BLOCK Transfer command, address 0x000C

Table 14: load\_sc\_data command register

#### 2.2.7 read\_results, BLOCK Transfer command, address 0x000E

| 15 2     | 1       | 0        |

|----------|---------|----------|

| reserved | DIF_LDA | SLAB_DIF |

| R, +0    | RS, +0  | RS, +0   |

| Bit no. | Bit Field | Description                                                                                                                                              |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 2  | reserved  | reserved                                                                                                                                                 |

| 1       | SLAB_DIF  | SLAB_DIF = '1' results are read from slab via DIF to LDA<br>(set by data = $0x0001$ ). Bit is reset by DIF after completion.<br>SLAB_DIF = '0' no action |

Table 15: read\_results register description

## 2.2.8 DIF Control Register: set\_control\_reg, BLOCK Transfer command, address 0x0010

By this command the DIF control register is set. A read-access to this register is done by the command read\_status\_control (see next section).

# The DIF CONTROL REGISTER (16-bit, RW, +0):

| Bit no. | Bit Field | Description                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-6    | CR15-CR6  | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 5       | CR5       | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 4       | CR4       | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 3       | CR3       | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 2       | CR2       | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 1       | CR1       | to be defined                                                                                                                                                                                                                                                                                                                                          |

| 0       | CR0       | <ul> <li>CR0 = '1' pre-spill signal is used to indicate an upcoming 'start_acquire'. DIF prepares for data taking (ACTIVE MODE). start_acquire is sent exactly at spill start.</li> <li>CR0 = '0' pre-spill signal is not used. "start_acquire" is sent from DAQ well in advance before the spill, so that DIF can prepare for data taking.</li> </ul> |

Table 16: DIF Control Register

| start_acquire        | synchronous to bunch clock | П |

|----------------------|----------------------------|---|

| pre_spill_indication | prepare for data taking    |   |

| 1ms bunch<br>train   |                            |   |

| 4                    | 200ms ~25µs                | → |

Figure 2: Usage of control register bit 0 (CR0). With CR0='1', the command pre\_spill\_indication is used from the DIF to prepare for a measurement (e.g. turn on slab power). The start\_acquire is used for synchronous indication of the start of the bunch-train.

| <b></b>                                   | 200ms 21.0                                            |          |

|-------------------------------------------|-------------------------------------------------------|----------|

| 1 1ms bunch<br>1 1ms bunch<br>1 1ms bunch | prepare for data taking,<br>duration XXX clock cycles |          |

| pre_spill_indication                      | sed (e.g. testbeam?)                                  | <b>,</b> |

| start_acquire                             | synchronous to bunch clock                            |          |

Figure 3: Usage of control register bit 0 (CR0). With CR0='0', the command pre\_spill\_indication is not used. The DIF prepares for a measurement (e.g. turn on slab power) following the start\_acquire that is sent XXX clock cycles (to be defined) before the start of the bunch-train.

2.2.9 read\_status\_control, BLOCK Transfer command, address 0x0012

| 15 2     | 1      | 0       |

|----------|--------|---------|

| reserved | STATUS | CONTROL |

| R, +0    | R, +0  | R, +0   |

| Bit no. | Bit Field | Description                                                                                                                      |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| 15 – 2  | reserved  | reserved                                                                                                                         |

| 1       | STATUS    | STATUS = '1' read DIF Status Register (set by data = 0x0002). Bit is reset by DIF after completion.<br>STATUS = '0' no action    |

| 0       | CONTROL   | CONTROL = '1' read DIF Control Register (set by data = 0x0001). Bit is reset by DIF after completion.<br>CONTROL = '0' no action |

Table 17: read\_status\_control register description

The DIF STATUS1 REGISTER (16-bit, R, +0):

| Bit no. | Bit Field  | Description                                                                                                                                                          |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 - 9  | ST12 – ST9 | ST12-ST9 = `0000' DIF is in SLEEP mode,<br>ST12-ST9 = `0001' DIF is in IDLE mode,<br>ST12-ST9 = `0010' DIF is in SYNC mode,<br>ST12-ST9 = `0011' DIF is in LOOP mode |

| Bit no. | Bit Field | Description                                                   |

|---------|-----------|---------------------------------------------------------------|

|         |           | ST12-ST9 = '0100' DIF is in ACTIVE mode,                      |

|         |           | ST12-ST9 = '0101' DIF is in READOUT mode,                     |

|         |           | ST12-ST9 = '0110' DIF is in CONFIG mode current_mode          |

|         |           | ST12-ST9 = `0111' DIF is in DEBUG mode,                       |

|         |           | ST12-ST9 = '1000' DIF is in CALIBRATE mode                    |

|         |           | ST12-ST9 = `1111' DIF is in ERROR mode                        |

| 8       | ST8       | ST8 = '1': current operation caused timeout (watchdog         |

|         |           | triggered)                                                    |

|         |           | ST8 = '0': no timeout                                         |

| 7       | ST7       | ST7 = '1': some supply voltages/currents show bad values      |

|         |           | ST7 = '0': power consumption ok                               |

| 6       | ST6       | ST6 = '1': commands from LDA are sent to DIF-DIF link         |

|         |           | ST6 = '0': DIF-DIF link not active                            |

| 5       | ST5       | ST5 = '1': Commands from DIF-DIF link are used                |

|         |           | ST5 = '0': Commands from LDA-DIF interface are used           |

| 4       | ST4       | ST4 = '1': Slow Control programming of ASICs (slabs)          |

|         |           | shows errors (readback). See which partition in section 2.2.6 |

|         |           | ST4 = '0': SC_programming ok                                  |

| 3       | ST3       | ST3 = '1': temperature too high (in-detector or DIF)          |

|         |           | ST3 = '0': temperature ok                                     |

| 2       | ST2       | ST2 = '1': Command rejected: DIF is active with other         |

|         |           | command.                                                      |

|         |           | ST2 = '0': incoming command is executed                       |

| 1       | ST1       | ST1 = '1': incoming command unknown                           |

|         |           | ST1 = '0': incoming command ok                                |

| 0       | ST0       | ST0 = '1': CRC of incoming frame shows errors                 |

|         |           | ST0 = '0': Incoming frame is valid (no transmission errors)   |

Table 18: DIF Status Register

# The DIF STATUS2 REGISTER (16-bit, R, +0):

| Bit no. | Bit Field  | Description                                               |

|---------|------------|-----------------------------------------------------------|

| 10 0    |            |                                                           |

| 12 - 9  |            |                                                           |

| 8       |            |                                                           |

| 7       |            |                                                           |

| 6       |            |                                                           |

| 5       |            |                                                           |

| 4       |            |                                                           |

| 3       |            |                                                           |

| 2       |            |                                                           |

| 1       | EndReadout | EndReadout='1': The last ASIC in readout chain has sent a |

|         |            | EndReadout to DIF. This bit is cleared by DIF on a        |

|         |            | 'start_readout' command.                                  |

|         |            | EndReadout='0': no EndReadout has arrived at DIF          |

| 0       | SCASat     | SCASat='1': One of the ASICs has sent a SCASat to DIF.    |

|         |            | This bit is cleared by DIF on a 'start_acquire' command   |

|         |            | SCASat='0': no SCASat from ASICs arrived at DIF           |

Table 18: DIF Status Register

#### 2.2.10 readout\_info, BLOCK Transfer command, address 0x0014

| 15 7     | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|----------|---------|---------|---------|---------|---------|---------|---------|

| reserved | ALL     | SERIAL  | VERSION | ID      | DATE    | FWvers  | FWdate  |

| R, +0    | R, +def |

| Bit no. | Bit Field | Description                                                                                                                              |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 7  | reserved  | reserved                                                                                                                                 |

| 6       | ALL       | ALL = '1' read all 'info' registers (set by data = $0x0040$ ). Bit<br>is reset by DIF after completion.<br>ALL = '0' no action           |

| 5       | SERIAL    | SERIAL = '1' read DIF SERIAL number (set by data =<br>0x0020). Bit is reset by DIF after completion.<br>SERIAL = '0' no action           |

| 4       | VERSION   | VERSION = '1' read DIF board version number (set by data<br>= 0x0010). Bit is reset by DIF after completion.<br>VERSION = '0' no action  |

| 3       | ID        | ID = '1' read DIF board ID number (set by data = 0x0008).<br>Bit is reset by DIF after completion.<br>ID = '0' no action                 |

| 2       | DATE      | DATE = '1' read DIF production date (set by data =<br>0x0004). Bit is reset by DIF after completion.<br>DATE = '0' no action             |

| 1       | FWvers    | FWvers = '1' read DIF Firmware version number (set by data<br>= 0x0002). Bit is reset by DIF after completion.<br>FWvers = '0' no action |

| 0       | FWdate    | FWdate = '1' read DIF Firmware date (set by data = 0x0001). Bit is reset by DIF after completion.<br>FWdate = '0' no action              |

#### Table 19: readout\_info register description

Each of the information (DIF SERIAL number, DIF board version number, DIF board ID number, DIF production date, ...) are 16-bit and part of the DIF firmware (cannot be changed via LDA).

#### 2.2.11 FPGA firmware, BLOCK Transfer command, address 0x0018

| 15 2     | 1     | 0       |

|----------|-------|---------|

| reserved | CRC   | LDA_DIF |

| R, +0    | R, +0 | RS, +0  |

| Bit no. | Bit Field | Description                                                                                                                                         |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 2  | reserved  | reserved                                                                                                                                            |

| 1       | CRC       | CRC = '1' CRC-check ok for last LDA-DIF data transfer<br>CRC = '0' transmission errors in current data set                                          |

| 0       | LDA_DIF   | LDA_DIF = '1' DIF firmware data is transferred from LDA<br>to DIF (set by data = $0x0001$ ). Bit is reset by DIF after<br>completion automatically. |

| Bit no. | Bit Field | Description             |

|---------|-----------|-------------------------|

|         |           | LDA_DIF = '0' no action |

Table 20: FPGA firmware download register description

2.2.12 sel\_command\_input, BLOCK Transfer command, address 0x001A

| 15 2     | 1       | 0         |

|----------|---------|-----------|

| reserved | RES_SEL | INPUT_SEL |

| R, +0    | RS, +0  | RW, +0    |

| Bit no. | Bit Field | Description                                                                                                                                                               |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 2  | reserved  | reserved                                                                                                                                                                  |

| 1       | RES_SEL   | RES_SEL = '1' input selection logic is reset for 4 clock<br>cycles. Bit is reset by DIF after completion automatically.<br>(set by data=0x0002)<br>RES_SEL= '0' no action |

| 0       | INPUT_SEL | INPUT_SEL = '1' DIF-DIF input is used<br>(set by data = 0x0001).<br>INPUT_SEL = '0' LDA-DIF input is used ( <b>standard conf</b> .)<br>(set by data = 0x0000).            |

Table 21: select command input register description

2.2.13 pre\_spill\_indication, BLOCK Transfer command, address 0x001C

| 15 1     | 0         |

|----------|-----------|

| reserved | PRE_SPILL |

| R, +0    | RS, +0    |

| Bit no. | Bit Field | Description                                                                                                                                                                                                       |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 – 1  | reserved  | reserved                                                                                                                                                                                                          |

| 0       | PRE_SPILL | PRE_SPILL = '1': a "start_acquire is expected within XXXX<br>clock cycles. Puts DIF into "ACTIVE" mode. Bit is reset by<br>DIF after completion automatically. (set by data=0x0001)<br>PRE_SPILL = '0': no action |

Table 22: pre\_spill\_indication register description

## 2.3 address map information

The addresses in this section refer to the type\_modifier sent in the incoming **BLOCK Transfer** commands. So the addresses are the same as in table 8.

| type_modifier address range | function                       | remarks |

|-----------------------------|--------------------------------|---------|

| (16-bit hex)                |                                |         |

| 0x0000 - 0x0090             | <b>Block Transfer Commands</b> |         |

| 0x1000 - 0x1FFF             | slab1: default sc_data set     |         |

| 0x2000 – 0x2FFF             | slab1: alternative sc_data set |         |

| 0x3000 – 0x3FFF             | slab2: default sc_data set     |         |

| 0x4000 - 0x4FFF             | slab2: alternative sc_data set |         |

| 0x5000 – 0x5FFF             | slab3: default sc_data set     |         |

| 0x6000 – 0x6FFF             | slab3: alternative sc_data set |         |

| 0x7000 - 0x7FFF             | slab4: default sc_data set     |         |

| 0x8000 - 0x8FFF             | slab4: alternative sc_data set |         |

Table 23: address map of the type\_modifier for the BLOCK Transfers. Preliminary!!

# **3 DIF States and State Diagram**

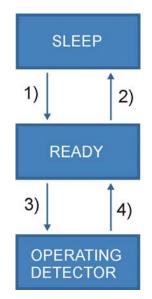

In the first DIF version, the top level finite-state-machine (FSM) has a simple structure with only three general (top-level) states as shown in Fig. 4. Additionally, the system can make use of "programmed" config/status registers. The global DAQ supervises global command sequencing and ensures that current operations are not disturbed by other operations. More complex FSMs could be used for the DIF-ASICs (ASICs inside the detector) interface modules, but these are "independent" to ensure the sequencing of the chips operation would not be disturbed/interrupted by other DIF functions (in a given global state of the DIF).

Figure 4: DIF States

SLEEP: Detector is powered-down, DIF still communicates with the DAQ (LDA). DIF configuration (register write and read) is possible. ASICs slow-control configuration can take place in this mode. READY: All operations are allowed. ASICs slow-control configuration can take place in this mode. Measurements can only be started if the detector is properly configured (slow control data is loaded into ASICs), no errors have occurred.

OPERATING DETECTOR: DIF can only execute commands that do not disturb the current datataking/data-conversion/readout operation (i.e. no slow-control loading, no debugging). ASICs are operated autonomously by the DIF-ASIC interface. All necessary functions for operation (e.g. trigger) are generated by hardware.

State Transitions: Commands & Conditions (see Fig. 4):

1) Transition executed on: power\_on, pre\_spill\_indication (asynchronous, see Fig. 2), set\_DIF\_mode, power\_pulsing (debugging)

2) Transition executed on: "turn power regulators off" set by option of power\_on command, set\_DIF\_mode, power\_pulsing (debugging)

3) this transition is allowed only when slow\_control configuration is done and no errors occured.

Transition executed on: start\_acquire, pre\_spill\_indication (synchronous, see Fig. 3), read\_results command.

4) Transition executed on: "stop\_data taking" set by option of start\_acquire command, RAMFull/SCASat condition, "readout\_results done" condition, reset command (all options)

# References

[1] Marc Kelly's web page:

http://www.hep.manchester.ac.uk/u/mpkelly/calice/lda/Calice\_LDA\_Overview.html

[2] Matthew Warren et al. "DAQ Status and Overview", CALICE week Manchester, Electronics Readout session II, Sept. 8<sup>th</sup>-10<sup>th</sup>, 2008

# **Revision History**

| Version / Date   | Changes with respect to last version                                     |  |

|------------------|--------------------------------------------------------------------------|--|

| 1.7 (3.12.2008)  | Reference document                                                       |  |

| 1.8 (5.1.2009)   | - Revision History added                                                 |  |

|                  | - DIF Status Register defined partly (section 2.2.9)                     |  |

|                  | - stop_readout added (FAST Command, new section 2.1.3)                   |  |

|                  | - reset_SC (reset of slow-control data only) added (section 2.2.2)       |  |

|                  | - Figure2 and Figure3 added (section 2.2.8)                              |  |

| 1.9 (6.2.2009)   | - power_on command extended (section 2.2.1)                              |  |

|                  | - DIF FSM changed (section 3)                                            |  |

| 1.10 (24.2.2009) | - STATUS2 register has been added (see section 2.2.9)                    |  |

|                  | - command 'read_results' changed to "send while receive" (section 2.2.7) |  |

|                  | - State 'IDLE' was renamed to 'READY' (section 2.2.3)                    |  |

|                  | - 'ALL' option added to readout_info command (section 2.2.10)            |  |

|                  | - State transitions have been defined (section 3, preliminary)           |  |

|                  |                                                                          |  |

|                  |                                                                          |  |

|                  |                                                                          |  |