In2p3

## Status of the DCC and DAQ Test Bench at LLR

Vincent Boudry Rémi Cornat David Decotigny Antoine Mathieu Franck Gastaldi

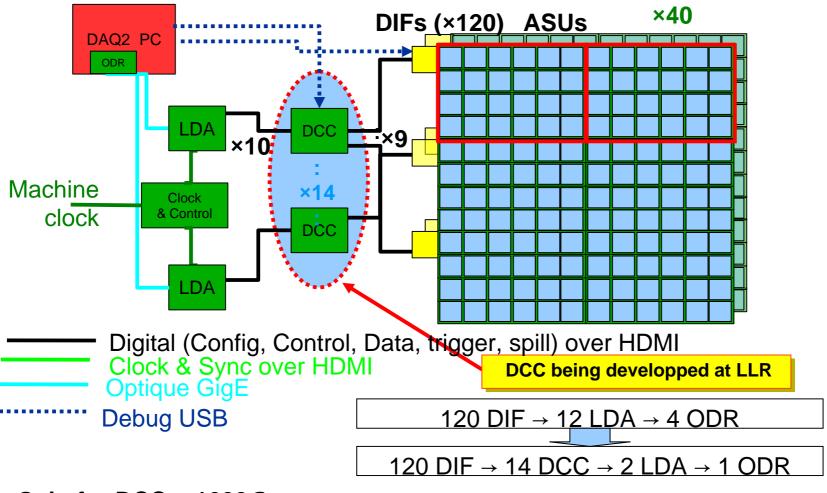

#### **DAQ** overview

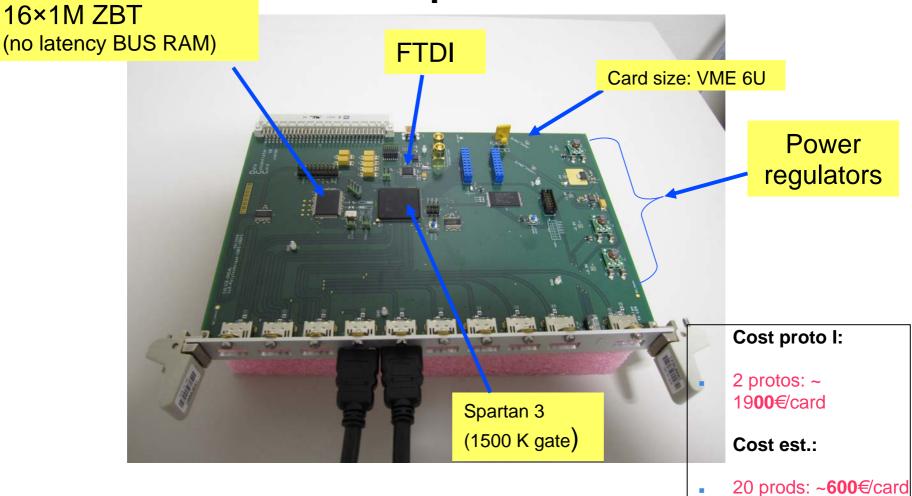

Gain for DCC ≤ 1600€

LYON, Sept. 17th 2009

## Everything is resumed here

• Main specification :

Reduce the number of LDA and ODR for the DHCAL & optimize the data flux

- Without DCC :

- 3 Difs/layer (40 Layers)

- 10 Difs/LDA => 12 LDA and 3 ODR

- With DCC, we need :

- 9 DIFs/DCC => 14 DCC => 2 LDA and 1 ODR

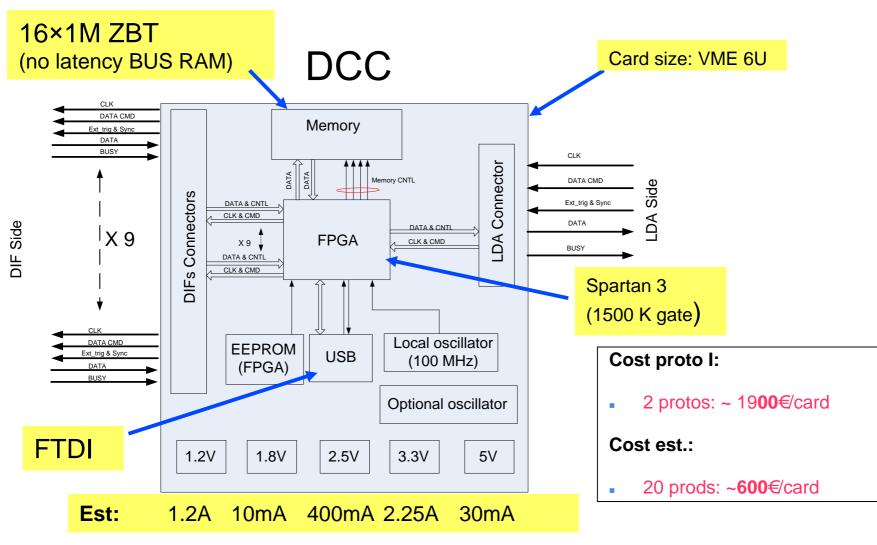

- Characteristics :

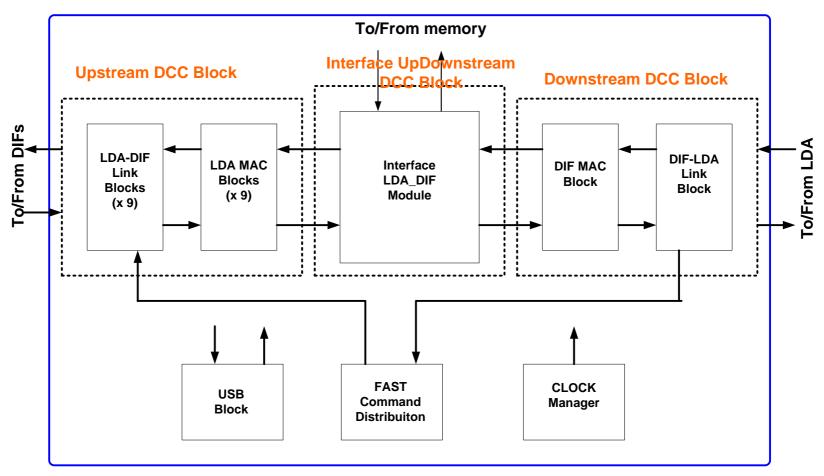

- To be transparent between DIF and LDA

- Broadcast all fast commands from LDA to all DIFs

- Send the packet R/O one after the other

- Read 9 DIFs (objective)

- Availability of USB access

- Firmware : Re-use as far as possible existing VHDL blocks (Marc)

- Homemade card

- Cheaper: objective (max 600 €/card) for the production

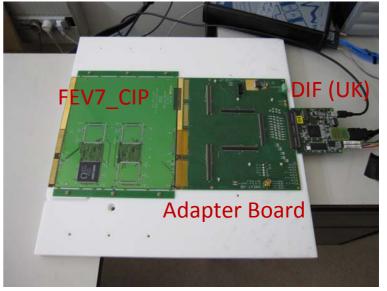

## **DCC** picture

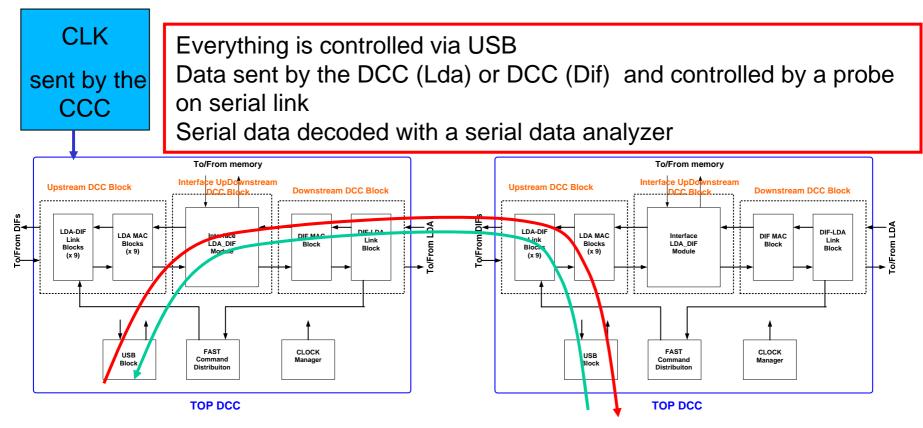

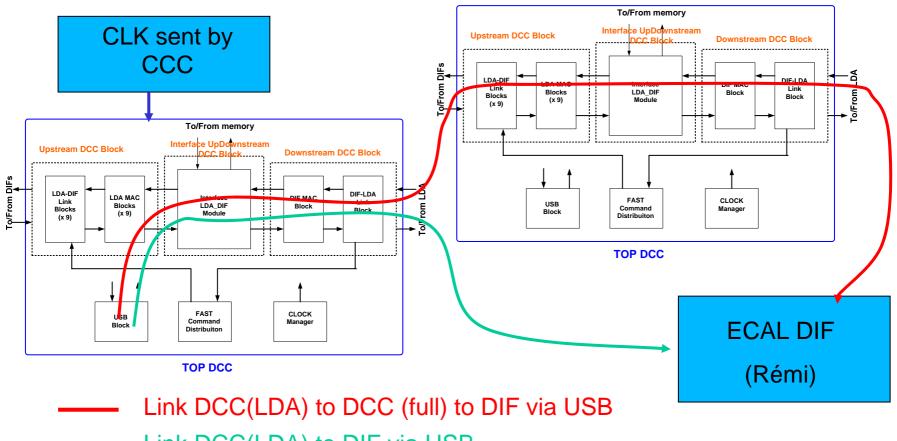

## FPGA architecture by functionalities

#### **TOP DCC**

LYON, Sept. 17th 2009

### **VHDL Blocks**

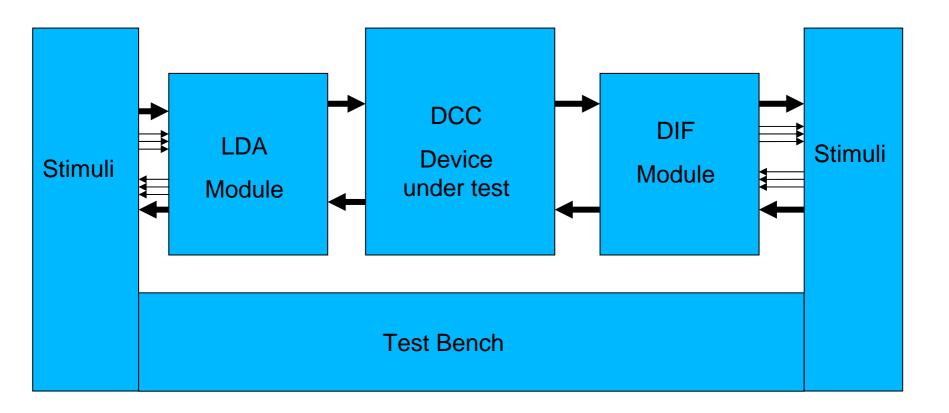

- •All VHDL blocks are designed

- •Some bugs are still present but all are identified

- End Oct. : Bug resolved

- End Nov. : Validation of VHDL in test bench

- End Dec. : Full validation of DCC

#### **VHDL** Test Bench

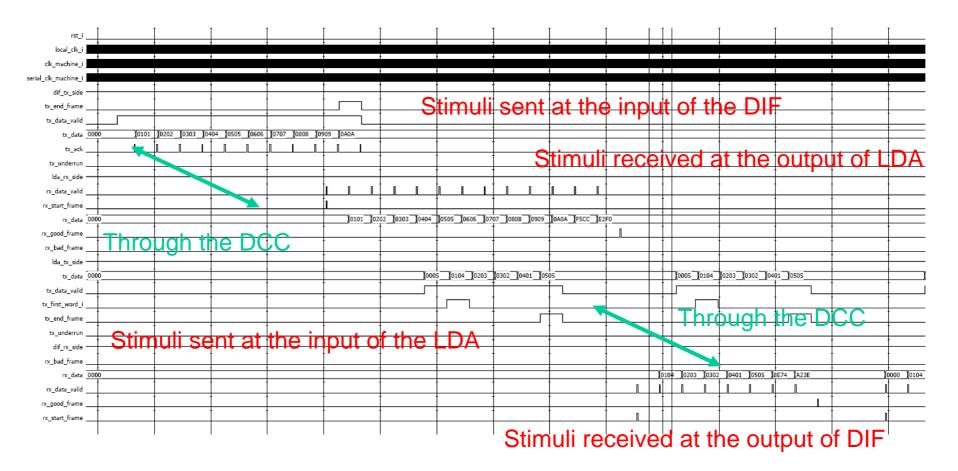

#### Example of simulation

# ECAL : First SLAB prototype assembled (03/07/09)

- Basic firmware for the DIF is developed

- 50 MHz

- HDMI/USB multiplexed

- Unique interface inside DIF

- Hardware test have started by the end

```

of August

FCMD

BTCMD

```

- Connexion to SPIROC2 should be effective within 2 weeks

- More details in ECAL session

CALICE week, Lyon, 17/09/09, Rémi Cornat

#### Test bench at LLR

#### Test Bench overview

#### CCC & DCC Chassis

LYON, Sept. 17th 2009

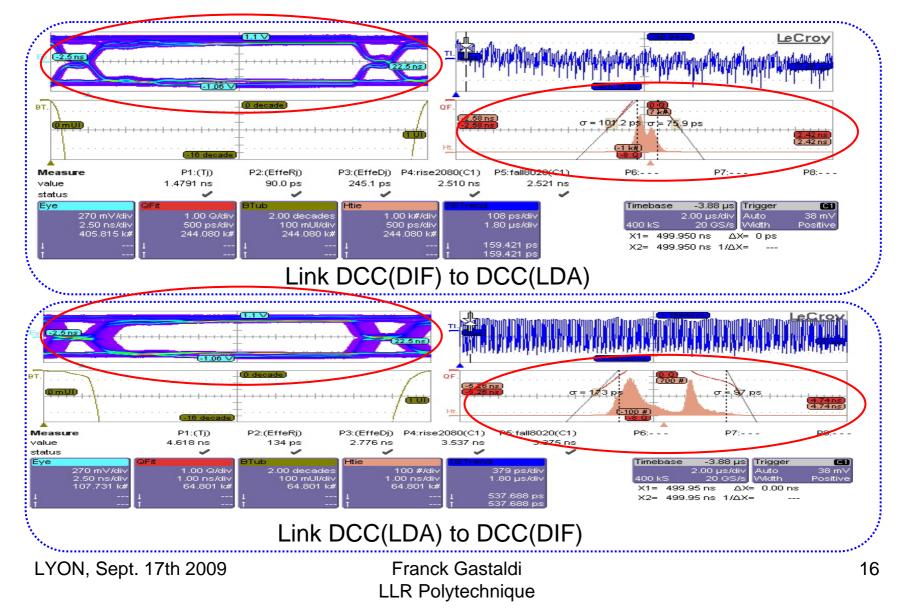

## Test with two DCC

Link DCC(LDA) to DCC(DIF) via USB Link DCC(DIF) to DCC(LDA) via USB

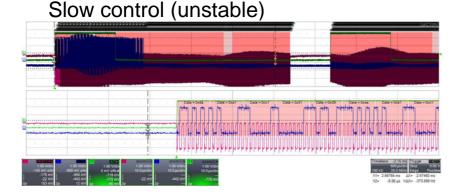

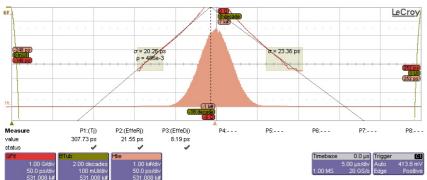

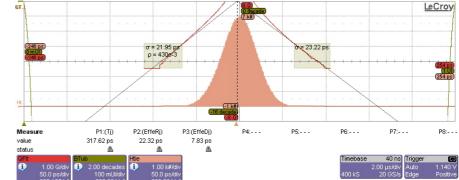

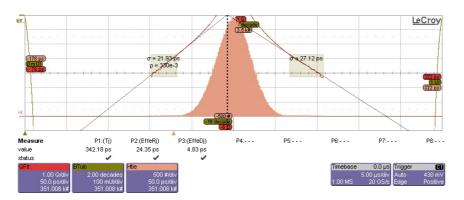

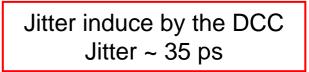

#### First test (clock) ccc => dcc => dif

Jitter at the input of DCC : Tj = 317 ps

Jitter at the input of CCC : Tj = 307 ps

Jitter at the input of DIF : Tj = 342 ps

LYON, Sept. 17th 2009

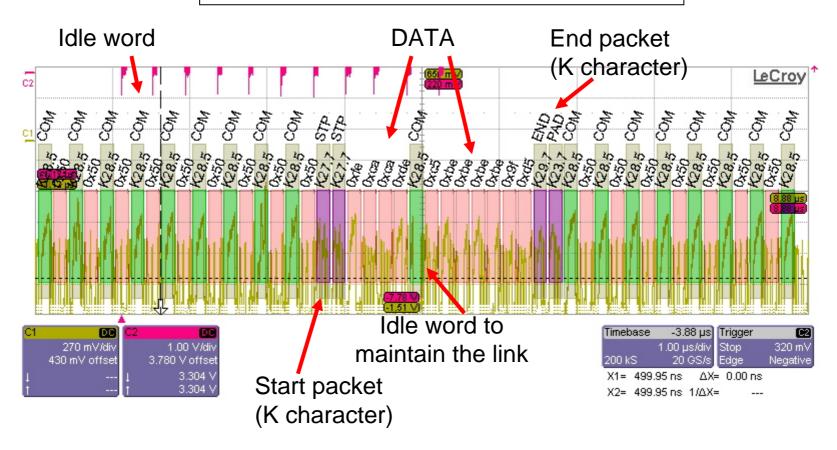

#### Some results on serial link

Data sent from DCC(DIF) to DCC(LDA)

## Data sent from DCC(DIF) to DCC(LDA)

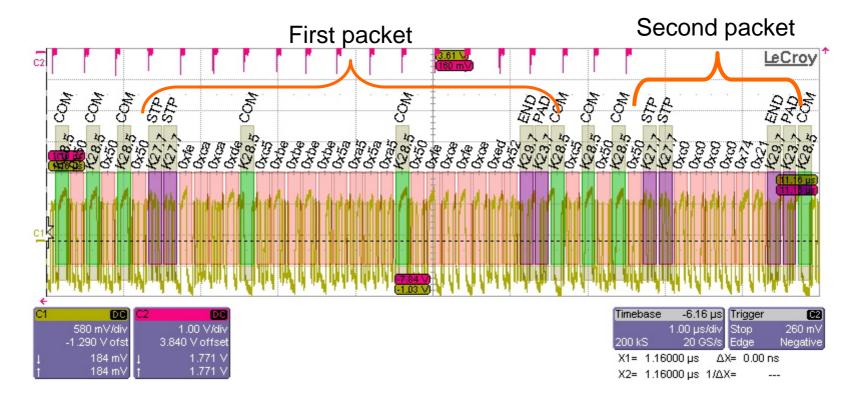

2 packets data sent

# Data sent from DCC(LDA) to DCC(DIF)

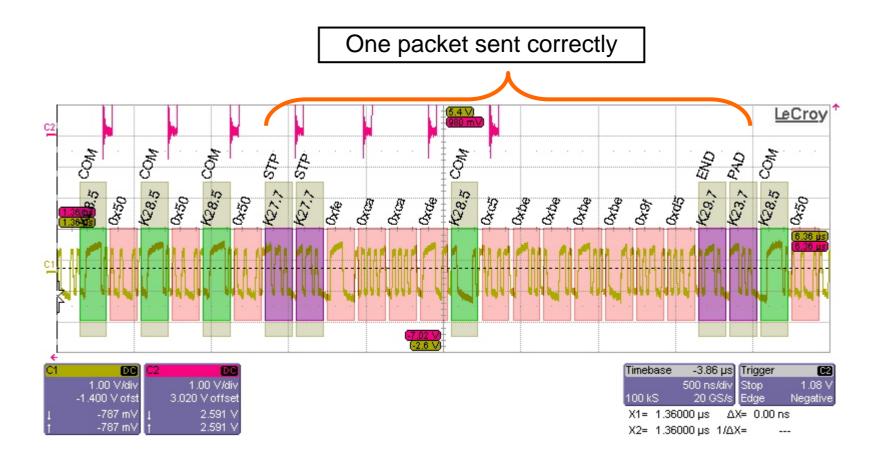

## Test with two DCC and one DIF

Link DCC(LDA) to DIF via USB

## Results

| Link                                                               | Fast<br>Command | Block<br>Transfer | Data  |

|--------------------------------------------------------------------|-----------------|-------------------|-------|

| DCC (Ida) →DIF                                                     | $\checkmark$    | $\checkmark$      |       |

| DCC (Ida) $\rightarrow$ DCC (full) $\rightarrow$ DIF               | $\checkmark$    | $\checkmark$      |       |

| DIF → DCC (Lda)                                                    |                 |                   | To do |

| $DIF \rightarrow DCC \text{ (full)} \rightarrow DCC \text{ (Lda)}$ |                 |                   | To do |

| $DIF \rightarrow DCC \rightarrow LDA$                              | To do           | To do             | To do |

| $LDA \rightarrow DCC \rightarrow DIF$                              | To do           | To do             | To do |

✓ : Validate

#### $\checkmark$ : do not work for the moment

### Conclusion

- Firmware is running on the DCC

- Until end of year:

- Tests & validation of VHDL code implemented on the DCC

- Test of Multi-channel on the DCC

- Test of a real DAQ Chain (ODR,LDA,DCC,DIF)

- Improvement of DCC card (layout) before production

- DCC Production (early of next year)

- February 2010 : PCB production

- March 2010 : PCB cabling

- April June 2010: tests at LLR

- Full DAQ : summer 2010

## Remarks for the thinking

- Where the LDA will be installed in test beam?

- What is the optimal length between the DIF and the DCC or LDA chassis ?

$(\rightarrow$  the length of HDMI cable)

- Should we use a special HDMI cable ?

- Who is responsible for power distribution ?

Should we go with our power supply ?

- Should we think of EMC and grounding problem ?

## Back up

LYON, Sept. 17th 2009

#### Card overview

LYON, Sept. 17th 2009