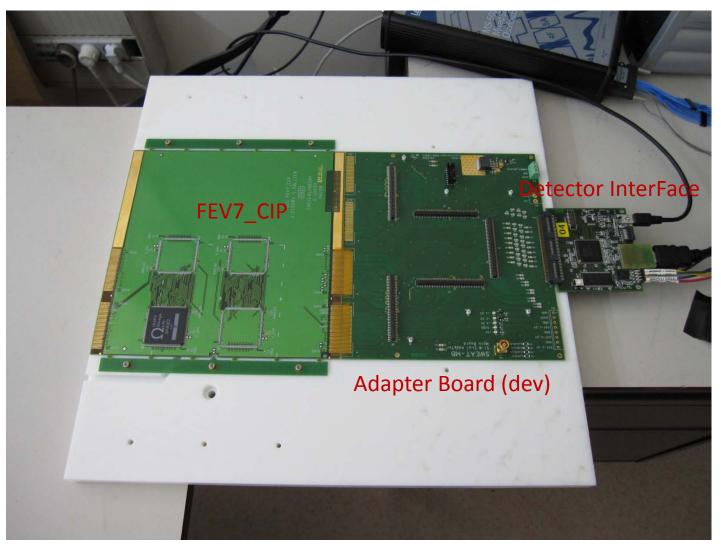

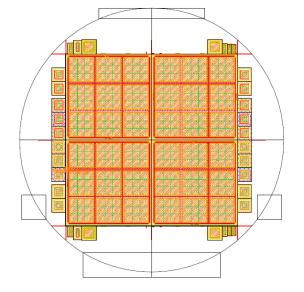

# First SLAB prototype assembled (03/07/09)

## ECAL : First SLAB prototype assembled (03/07/09)

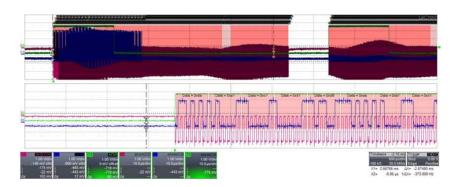

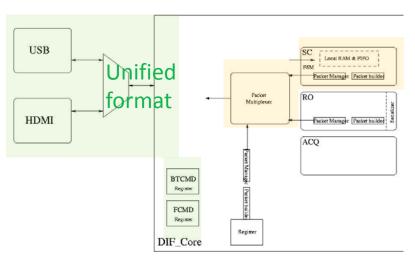

- Basic firmware for the DIF is developed

- 50 MHz

- Multiplexed HDMI/USB

- USB tested over few millions 256 B transfers

**From HDMI**

- Unique interface inside DIF

- Hardware tests have started by the end of August

- FCMD

- BTCMD

- Slow control (unstable)

- Connection to SPIROC2 should be effective within 2 weeks

- Slow control interface to the ROCs

- Packet formatter and packet multiplexer

are being tested

## Silicon Sensors

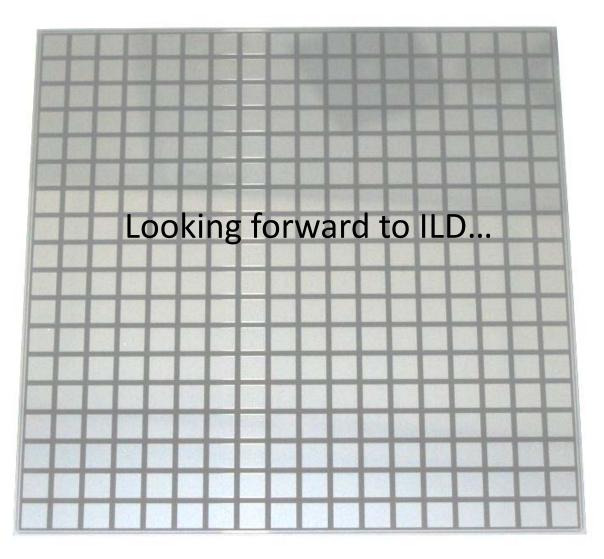

## Si design

#### P++ implants (pixels)

- The simplest design to control the cost

- Few thousands of m<sup>2</sup> needed for ILD

- Minimize the number of steps of the processing procedure

- Guard rings = same as pixels

- Glued on PCB : Floating GR

- Drawbacks : lack of optimization

- Large dead zone at the edges

- Crosstalk (Square Events)

- But...cost is still too high

- 70 keur (including NRE) for 40 pcs of this hamamatsu prototype = 22 € / cm2 (14 w/o NRE)

- Cost estimate for ILD : ~2 € /cm<sup>2</sup>

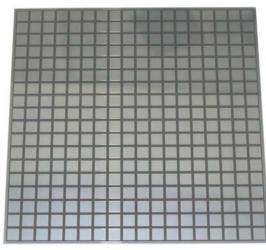

9x9 cm<sup>2</sup>, 324 pixels

## Si overview

- Experience with Czech, Russian and Korean sensors on the physics prototype

- 500 nm, 6x6 cm<sup>2</sup>, 36 pads

- Square events : understood to come from guard rings

- Dead area at the edges

- Search for new design techniques

- Reducing crosstalk due to the GR

- Segmented guard rings to avoid square events

- Lowering Dead space (at the border)

- Improved design for the technological prototype (& particle flow physics)

- Hamamatsu design: 300 nm, 9x9 cm<sup>2</sup>, 256 pads

- Have guard rings ! External charge injection shows square events...

- Large dead space

- Cost of prototypes: 70 k€ = 40 wafers(EUDET needs 160) batch received at LLR! NEW : Production) at LLR!

NEW : Prototypes are measured !

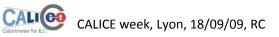

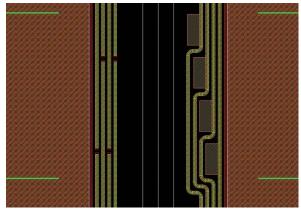

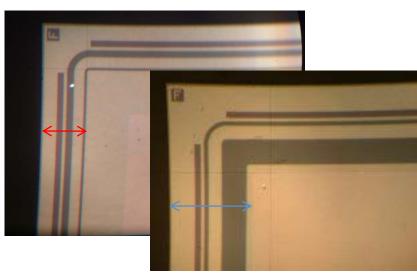

## Segmented guard ring

- Should avoid the signal propagation along the border of the wafer

- Idea tested thanks to PCBs and test bench at LPC (CALOR'08, NSS'08 talks)

- Segmented topology helps to prevent SqEvt (factor) 50 on signal intensity)

- What about current leakage & breakdown ?

- Prototype wafers have been manufactured (LLR made layout)

- OnSemi/Institute of Physics (Prague), Cz

- NEW : Prototypes received at BARC ! BhaBha Atomic Research Centre, India

- Tests are ongoing

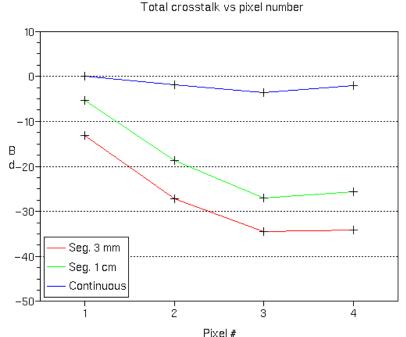

### CNIS R&D on segmented guard rings

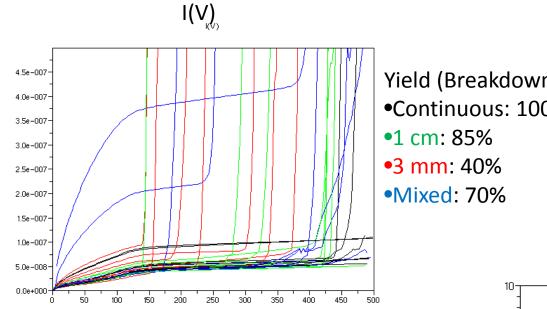

Yield (Breakdown >250V) •Continuous: 100%

Sum of GRs contribution Xtalk lowered by a factor 80 (with 3 mm segments (measurements made at LPC)

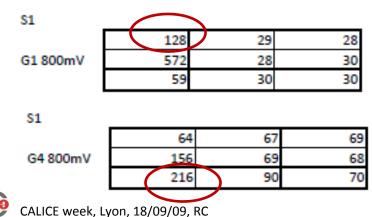

CALICE week, Lyon, 18/09/09, RC

## Next R&D prototypes of segmented guard rings

Vary Inter segment gap : 1 cm segment with 5, 10, 25 (actual: 50 um)

Distributed capacitance: Mixed: inner 2cm, 1 cm , outer 3mm - 1mm 2 conferences IEEE NSS'09 IEEE Sensors'09

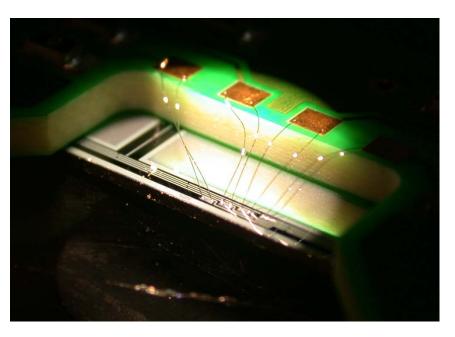

bounding attempt at CERN in order to ease the measurements But it adds some Xtalk

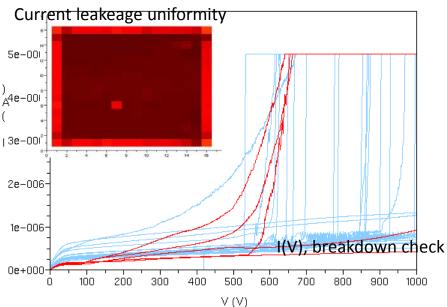

## Hamamatsu sensor V2

- Dead area decreased to 750 um (1200 μm previous)

- Leakage current issue seen at Hamamatsu

- Level: x 5-10 wrt previous sensors , bad uniformity

- They developed a new test setup : better!

- 5 samples + production batch of 35 pcs

Current leakeage

(received this week)

- Breakdown ok but seems to be slightly ) Iower

- Have 40 sensors to start EUDET SLAB assembly (160 needed)

I(V)

## Silicon Sensors

## Some optimizations

**3D sensors** : lower Vbias, internal current flow, low sensibility to edge effects : can be ~edgeless (100 um)

## tor Vertex detectors Cut through edge

Integration same technology as for 3D but used only at the edge no saw cuts, 3D edges 4-side abuttable ~*no dead space*, Deep trench etch, n doped polysilicon fill provides edge doping

**Trenches + saw cut** : cost of trenching, post processing of every sensors, bad control of current.

#### Dry etching cut

#### **Current terminating ring** two rings but biased : thin contact needed, gluing not applicable edge width less than ½ wafer thickness **Double sided GR Doped edges** Crosstalk + ~edgeless ③ (300 um) **Punch-through biasing** Integration 😕 **Biased GR** edge 🙁 (800 um) Segmented GR : need further tests CALICE week, Lyon, 18/09/09, RC

12

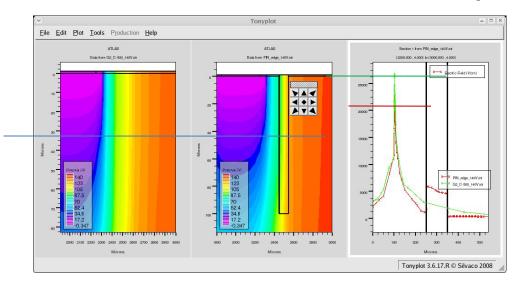

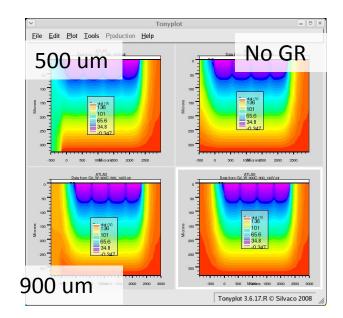

# Simulation tools examples

Disclaimer : an simulations included in this talk are doubtful, simplistic and wrong

100 x 100 um

Lower Max E with a trench (red)

#### Double sided GR

# Contributors to the previous prototypes

**ON Semiconductor®**

Governmert of India Department of Atomic Inergy SHABHA ATOMIC RESEARCH CENTRE

HAMAMATSU

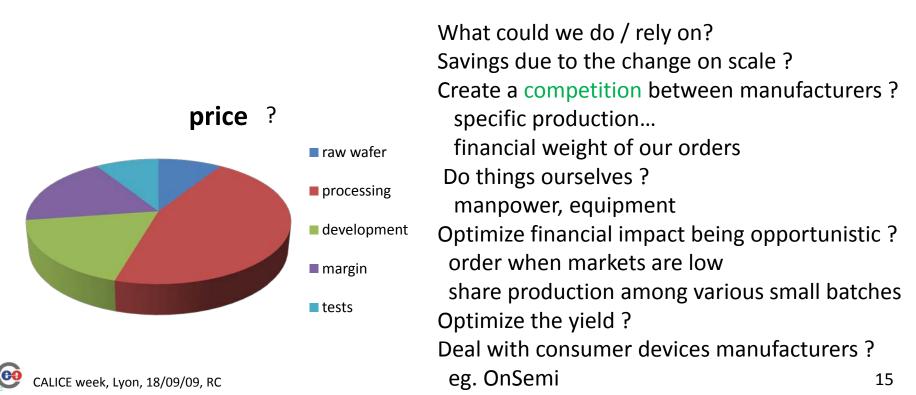

## The cost issue

The cost estimate of a financially viable ECAL for

ILD assumes this input :

A cost at the level 2  $\pounds$  / cm<sup>2</sup>

Now we are at the level of 10 to  $20 \notin /cm^2$

About 2500 m<sup>2</sup> of sensors needed for SiW ECAL of ILD = 300 000 sensors (actual design)

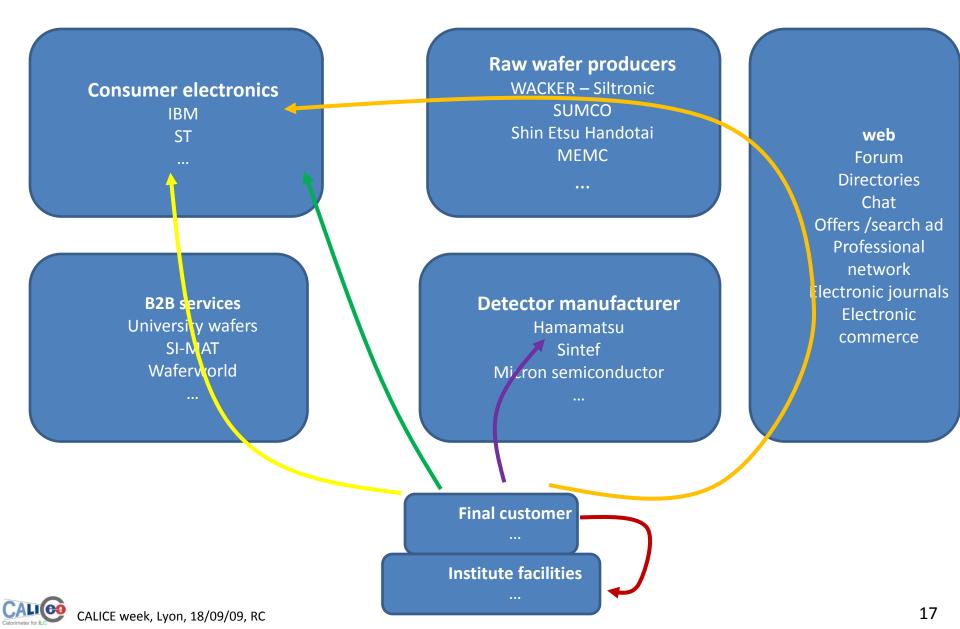

## Some market trends

- High resistivity silicon : RF & wireless, power devices

- New method to produce HiRes silicon with CZ process

- Manufacturing tools for 300mm

- R&D to produce 300 mm FZ ingots : 4 sensors

- Market is dominated by electronics and photovoltaic silicon, resistivity below 10 Ohms.cm

- Our production is rather small

- Some specific features

- Passivation (Ileak, compatibility with glue)

- Guard rings

## Si Market Overview

## The cost issue

**Commercial market**

- Market analysis

- Increase our visible weight to start bargaining

- Develop our contacts in the industry

- Find the necessary funding to invest in R&D with a panel selected of manufacturers

#### Institutional organizations

- Have the necessary knowledge of the manufacturing processes, develop our own R&D or production facilities ?

- Silicon factory at fermilab

- Association with existing European platform for micro/nano tech

- Eg. MINERVE at Orsay, CEA-LETI, ...

- European programs for technological platforms

- Buy or loan an obsolete industrial production chain (eg. AMS 0.35 ?)

- Show that we could do it ourselves

## Conclusion

- Invest for future cost optimization

- Funding (and manpower) for R&D

- Opportunity of technological prototype

- Several batches of sensors from various manufacturer

- Establish relationship

- Allow consumer devices manufacturers

- Market study

- Avoid a dependence in a single design / manufacturer

- Increase our visible weight

- Collaboration & network (CERN...)

- Bargaining

- Generate interest from consumer electronics manufacturers (ST, Samsung, OnSemi,...)

- Improve our tests / qualification procedure

- Test beams

- Test equipment

- Exhibit a reasonable knowledge of the sensors to enable discussion and avoid the trap of dependence