ΪĿ

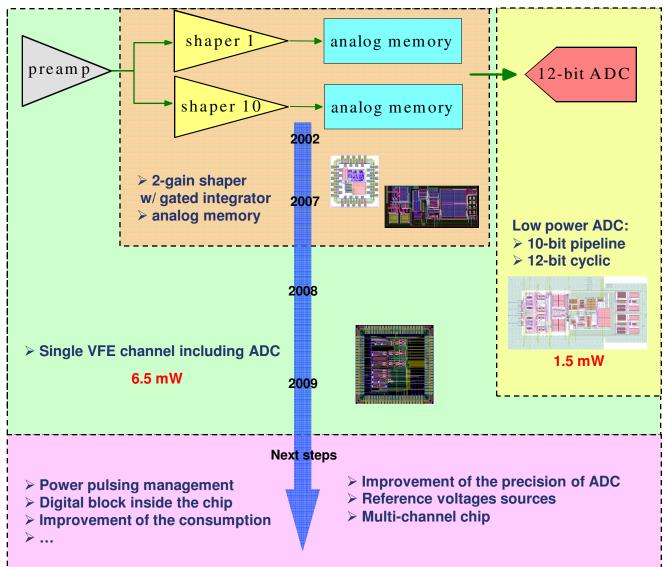

## **R&D** activity dedicated to the VFE of the Si-W Ecal

L.Royer, S.Manen

L.Royer- Calice week @ Lyon - Sept. 16-18, 2009

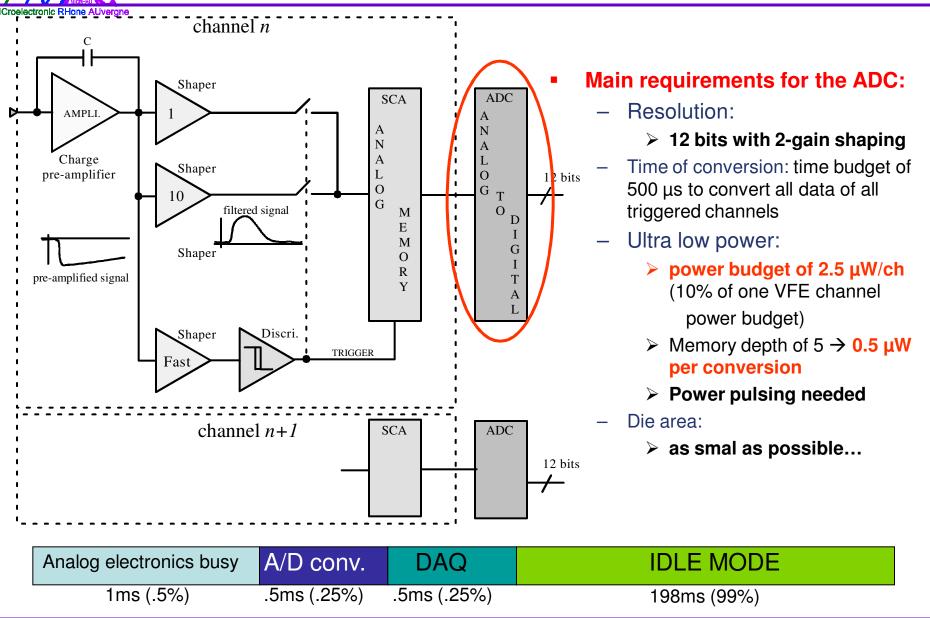

# **ADC development**

L.Royer- Calice week @ Lyon - Sept. 16-18, 2009

## The cyclic ADC designed (03/08)

✓ Clock frequency: 1MHz

✓ Supply voltage : 3.5V

Die area of the core = 0.12mm2

✓ Technology: 0.35 µm CMOS Austriamicrosystems (reliable and cheap !!)

✓ ADC designed with the validated building blocks (Amplifier & Comparator) of a 10-bit pipeline ADC (published in IEEE NSS in June 08) but optimized for the 12-bit precision requirement

- ✓ Power pulsing system implemented

- ✓ Digital process of the bits (1.5 bit/stage algorithm) performed by an external FPGA

- ✓ Fully differential ADC: analog signal, reference, clock...

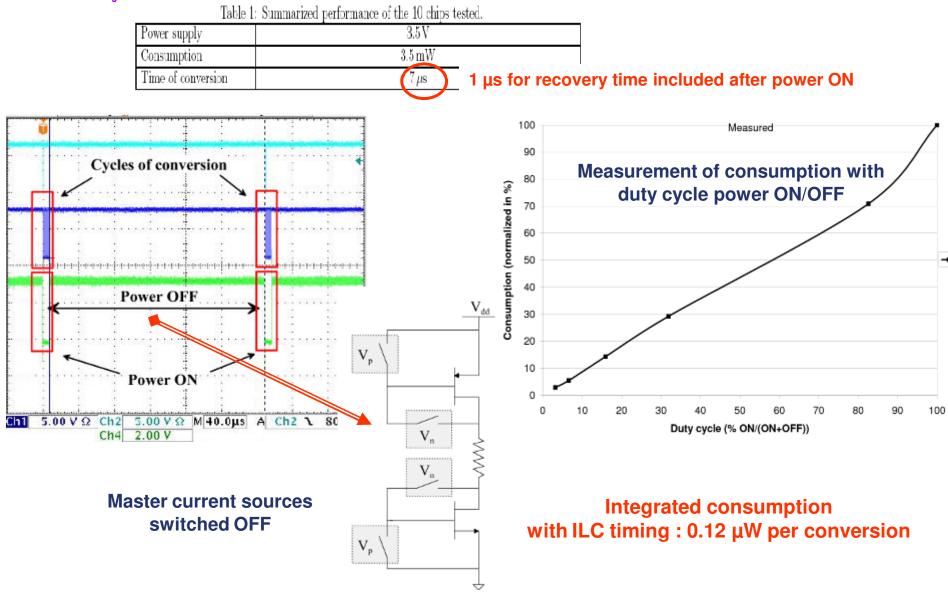

## Power pulsing measurement

| ADC version | Yield | INL of 6 chips<br>(mean ± σ) | Noise<br>(rms) | Consumption***               | Die area*           |

|-------------|-------|------------------------------|----------------|------------------------------|---------------------|

| March 08    | 6/10  | (3.6 ± 1.2) LSB              | 0.84 LSB       | 3.5 mW *<br>0.12 μW w/ PP ** | 0.12mm <sup>2</sup> |

\* without the digital block

\*\* power pulsing with duty ratio of 1%

\*\*\* for one conversion

#### Improvement of the performance of the ADC

New cyclic ADC submitted to run in 03/09:

- ✓ Reduction of power supply voltage: 3.5V to 3.0V

- $\checkmark$  Optimization (reduction) of BW performance of the amplifier

- $\checkmark$  Improvement of the yield: reduction of biasing variation versus process

fluctuation  $\rightarrow$  single stage amplifier

| ADC version                                                                                                                                           | Yield | INL of 10 chips<br>(mean ± σ) | Noise<br>(rms) | Consumption***                      | Die area*           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|----------------|-------------------------------------|---------------------|--|--|

| March 08                                                                                                                                              | 6/10  | (3.6 ± 1.2) LSB               | 0.84 LSB       | 3.5 mW *<br>0.12 μW w/ PP **        | 0.12mm <sup>2</sup> |  |  |

| March 09                                                                                                                                              | 10/10 | (3.0 ± 0.8) LSB               | 0.3 LSB        | <b>1.5 mW *</b><br>0.05 μW w/ PP ** | 0.12mm <sup>2</sup> |  |  |

| * without the digital block<br>** power pulsing with duty ratio of 1% Equivalent to a Capacitance mismatch of about 1 fF !!<br>*** for one conversion |       |                               |                |                                     |                     |  |  |

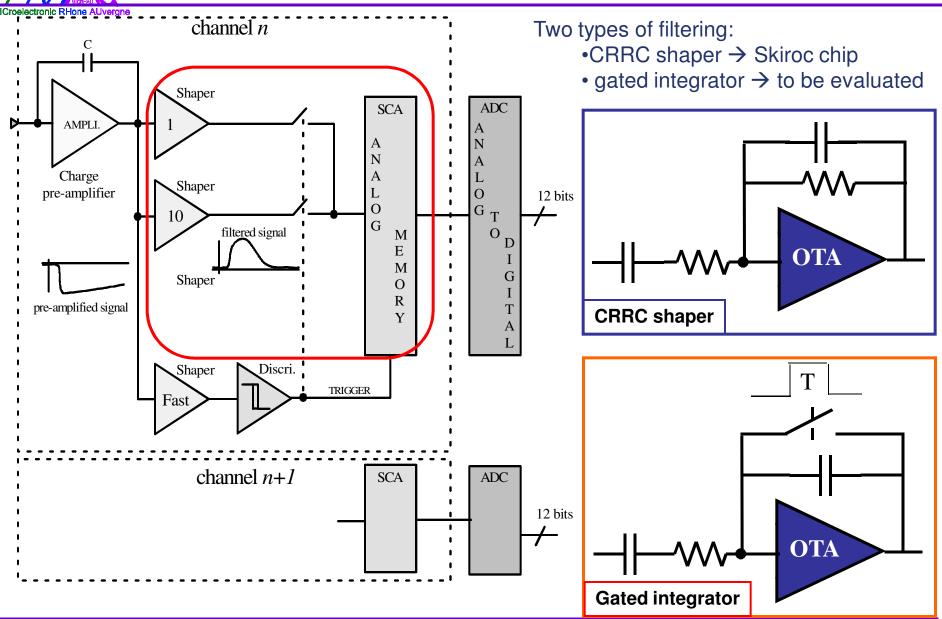

# Shaper & analog memory

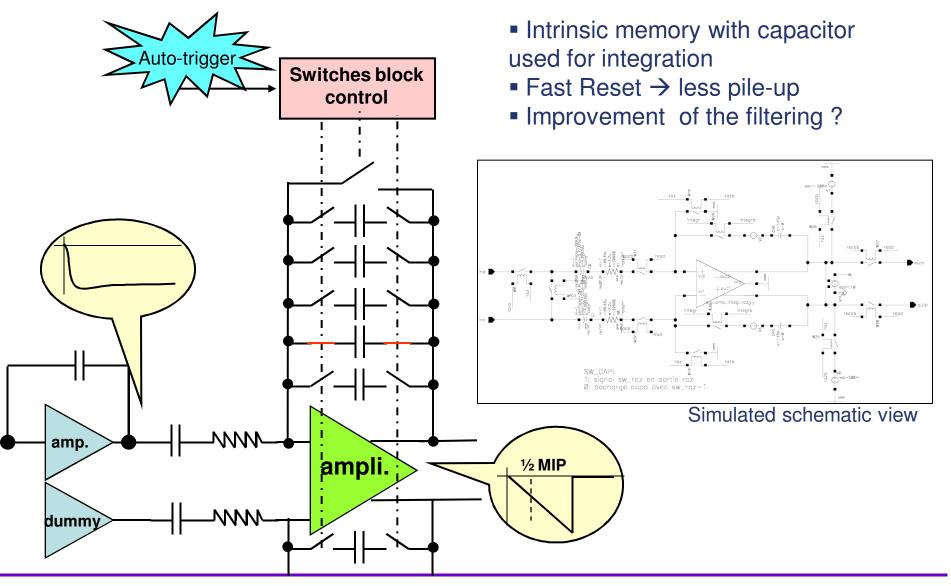

## The gated integrator

## Channel designed for evaluation

### Conclusion

#### "Long is the road ..."