# CALICE/EUDET FEE status

C. de LA TAILLE

Orsay Micro Electronic Group associated

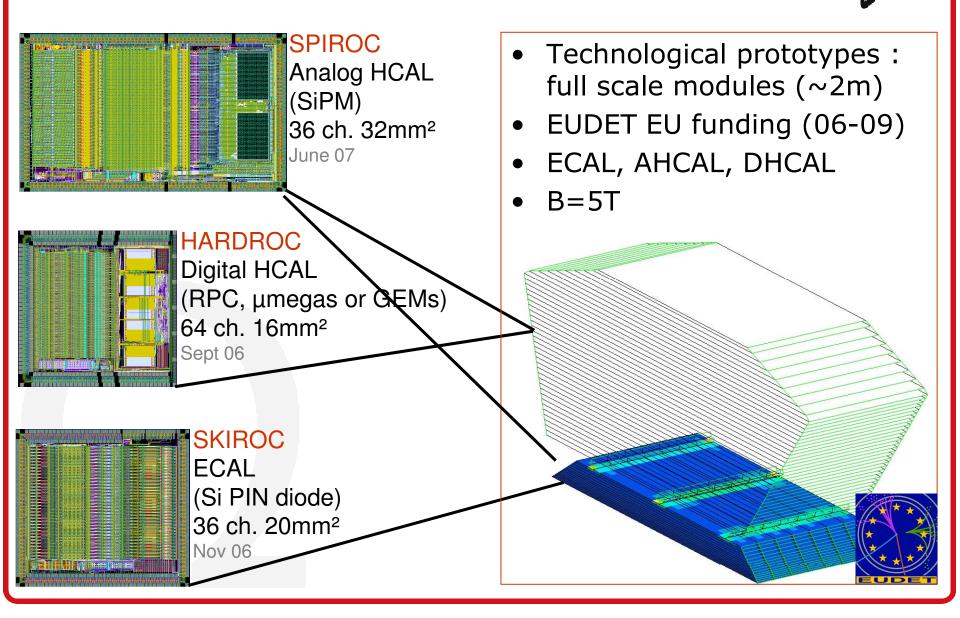

# ILC front-end ASICs : the ROC chips

<u>(mega</u>

# HaRDROC status

- 240 chips HARDROC1 produced in june 2007 to equip 4-chip and 24-chip RPC and Micromegas detectors

- Package PQFP240

- Not completely power-pulsed

- 400 chips HARDROC2 produced in june 2008 to equip 24-chip RPC and Micromegas for square meter

- 3 thresholds (0.1-1-10 pC)

- Power pulsed to 5-8  $\mu$ W/ch

- Package TQFP160

- Essential for readout + DAQ2 validation

- Full production run : end 2009

- After validation on detector

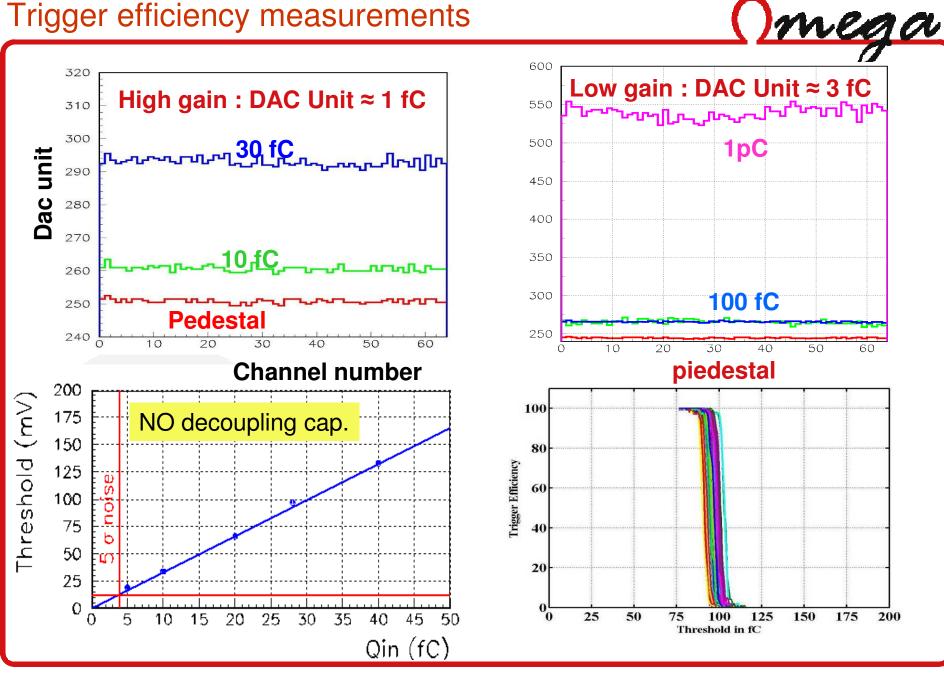

# Trigger efficiency measurements

31 aug 2009 EUDET SC

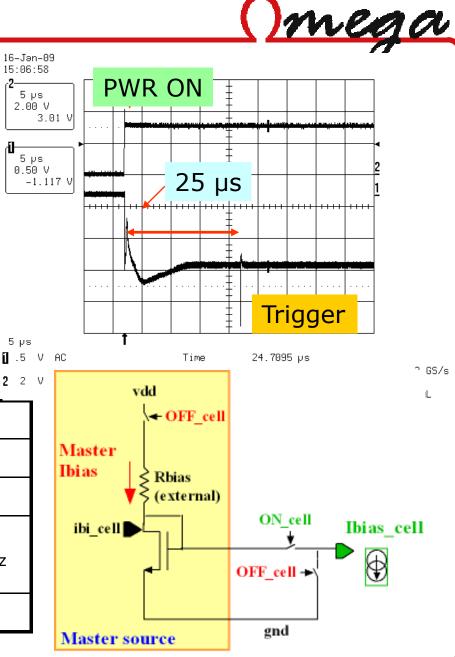

# Power pulsing

- Total power on : 100 mW

- Total power off : 10 μW

- Power dissipation

- 1.5 mW/ch continuous

- 25 µs awake time

- 7.5  $\mu$ W/ch with 0.5% duty cycle

- 10 µW/ch = 24h operation of ful slab with 2 AAA batteries !

| PA        | 5.46mA | DAC   | 0.84mA                               |

|-----------|--------|-------|--------------------------------------|

| 3 FSB     | 12.3mA | BG    | 1.2mA                                |

| SS        | 9.3mA  | vddd  | 0.67mA                               |

| 3 Discris | 7.3mA  | vddd2 | <b>0.4mA</b><br>(=0 if 40MHz<br>OFF) |

| TOTAL     | 38mA   |       |                                      |

|           |        |       |                                      |

31 aug 2009 EUDET SC

# Readout validation with HARDROC

### Assembled(IPNL)

Fichier

Vertical

Base de temps

Déclenchement

Affichage

Curseurs

Mesure

Math

Analyse

Utilitaires

Aide

| C1  | DCIM          | C2 | DCIM          | C3  | (DICHM)       | C4 | DIGIM         |

|-----|---------------|----|---------------|-----|---------------|----|---------------|

|     | 1.00 V/div    |    | 1.00 V/div    |     | 1.00 ∀/div    |    | 1.00 V/div    |

|     | -1.010 ∨ ofst |    | -1.500 ∨ ofst |     | -3.560 ∨ ofst |    | 570 mV offset |

| 1   | 12 m∨         | 1  | 3.310 V       | 1   | 558 m∨        | 1  | 26 mV         |

| 1 T | 5 m∨          | t  | 536 mV        | ΙŤ. | 536 m∨        | Ť  | 48 m∨         |

| Δy  | -7 m∨         | Δy | -2.774 V      | Δy  | -22 m∨        | Δy | 22 m∨         |

| Le( | Croy          |    |               |     |               |    |               |

Tbase

-616 μs

Déclenchem C1 De

200 μs/div

Normal

1.19 V

200 kS

100 MS/s

Front

Positive

X1=

325.79 μs

ΔX=

-160.00 μs

X2=

165.79 μs

1/ΔX=

-6.2500 kHz

<u> Mega</u>

aiting for Trigger

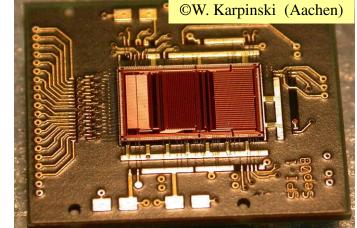

120 2 1 Fully equipped large scalable detector to be soon tested in cosmic rays bench and in test beam at CERN in summer 09 [I. Laktineh et al.] Similar development with µMEGAS [C. Adloff et al.] **A NICE PROOF of INFRASTRUCTURE**

31 aug 2009 EUDET SC

Status of JRA3 Front End Electronics

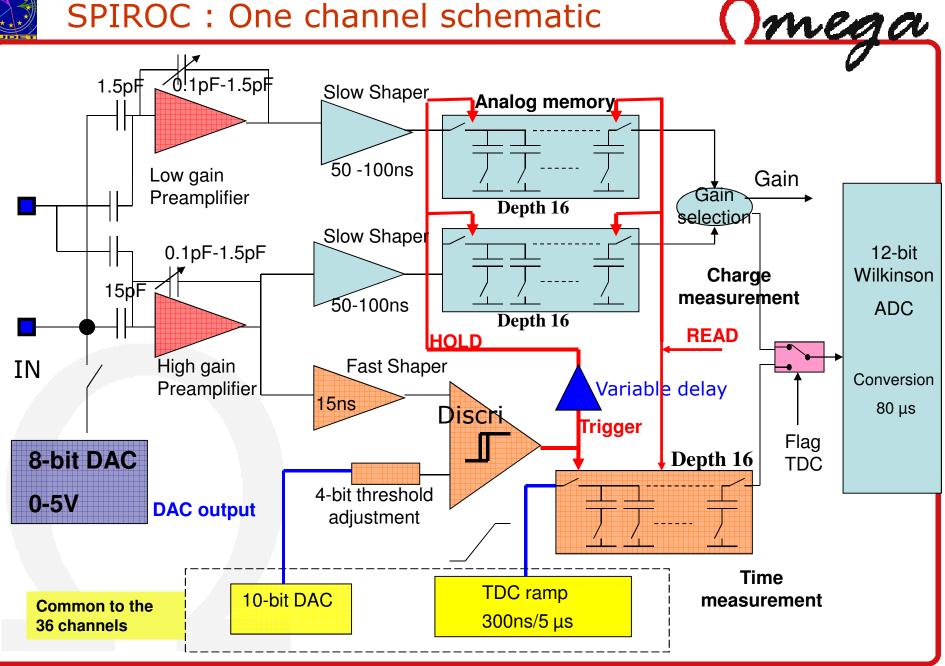

# SPIROC for AHCAL

- Internal input 8-bit DAC (0-5V) for individual SiPM gain adjustment

- Energy measurement : 14 bits

- 2 gains (1-10) + 12 bit ADC 1 pe  $\rightarrow$  2000 pe

- Variable shaping time from 50ns to 100ns

- pe/noise ratio : 11

- Auto-trigger on 1/3 pe (50fC)

- pe/noise ratio on trigger channel : 24

- Fast shaper : ~10ns

- Auto-Trigger on ½ pe

- Time measurement :

- 12-bit Bunch Crossing ID

- 12 bit TDC step~100 ps

- Analog memory for time and charge measurement : depth = 16

- Low consumption :  $\sim 25 \mu W$  per channel (in power pulsing mode)

- Individually addressable calibration injection capacitance

- Embedded bandgap for voltage references

- Embedded 10 bit DAC for trigger threshold and gain selection

- Multiplexed analog output for physics prototype DAQ

- 4k internal memory and Daisy chain readout

nega

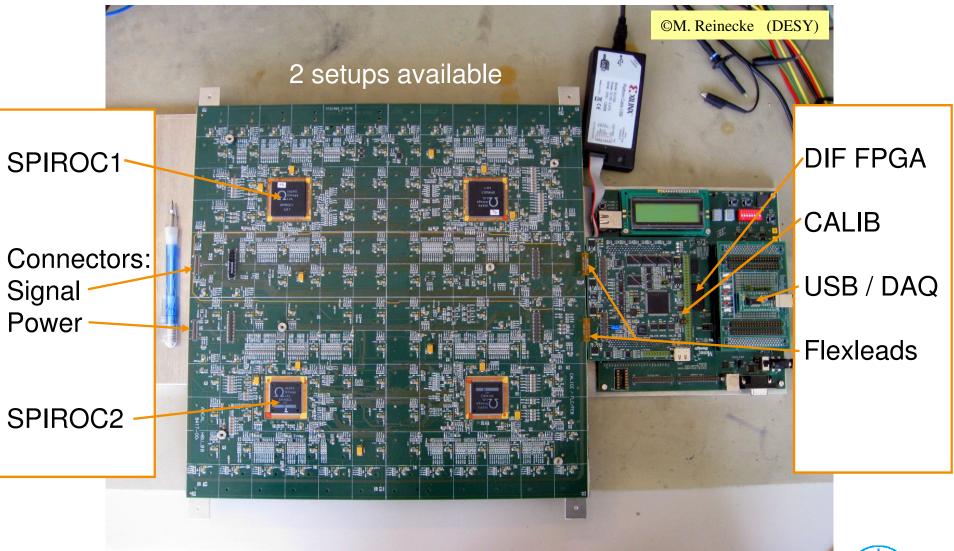

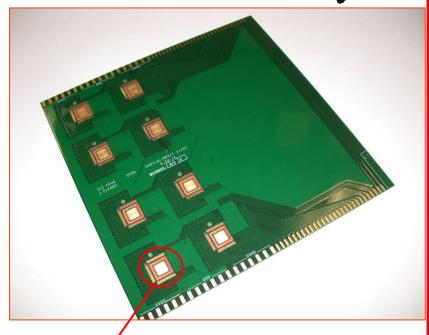

### ECAL board FEV7 with SPIROC2

31 aug 2009 EUDET SC

# SPIROC status

- 200 chips SPIROC1 produced in nov 2006

- Package PQFP240

- Good analog performance

- Bug in ADC ramp : no digital data out !

- 50 chips SPIROC2 produced in june 2008 to equip AHCAL and ECAL EUDET modules

- Fulfiled EUDET milestone

- Package TQFP208

- Difficult slow control loading

- Measurements (slowly) coming in

- Complex chip

- Collab LAL, DESY, Heidelberg

- External requests :

- astrophysics PEBS (Aachen), medical imaging (Roma, Pisa, Valencia...), nuclear physics (IPNO), Vulcanology (Napoli)

#### **HBU0 status**

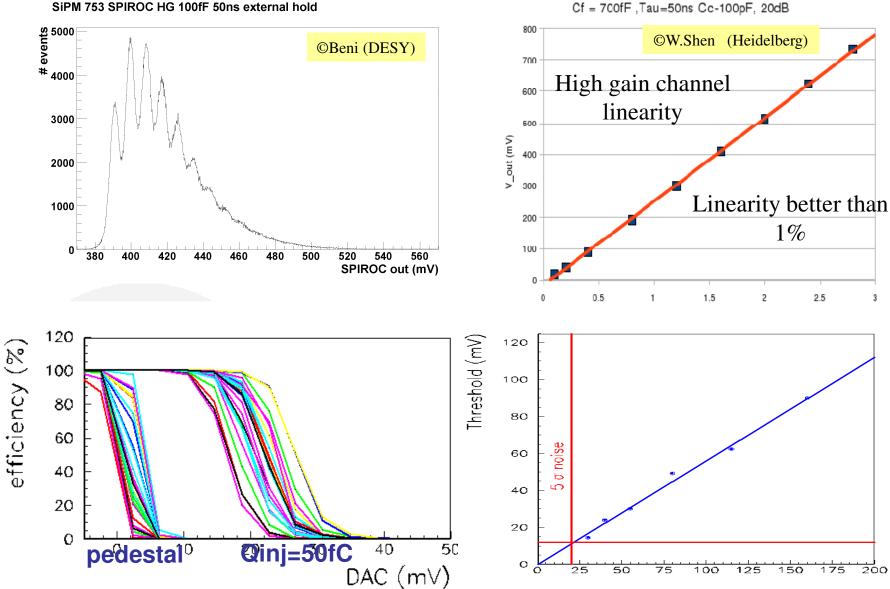

### Performance

<u>(mega</u>

SiPM 753 SPIROC HG 100fF 50ns external hold

31 aug 2009 EUDET SC

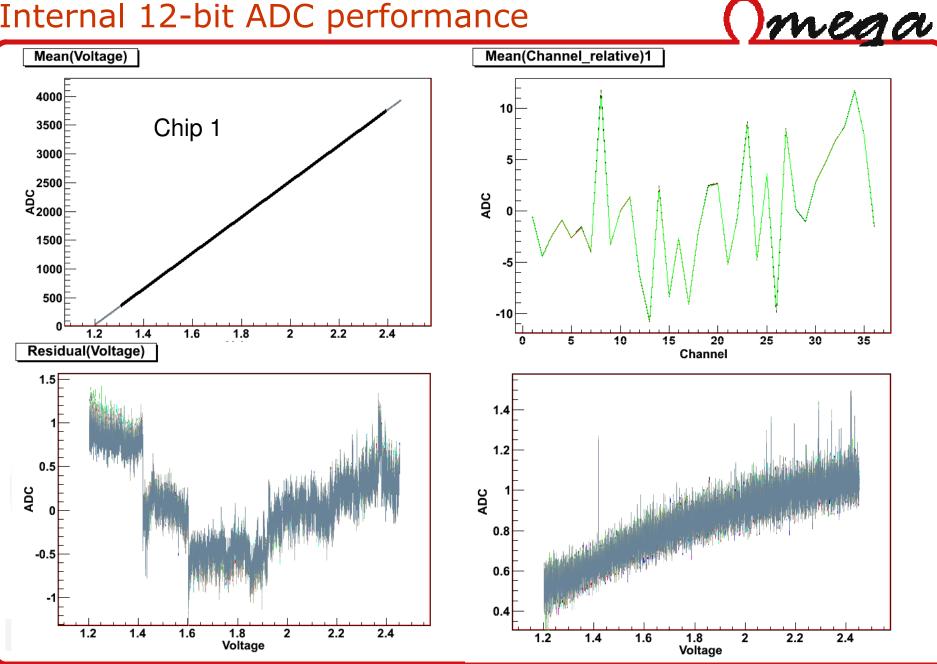

### Internal 12-bit ADC performance

EUDET SC 31 aug 2009

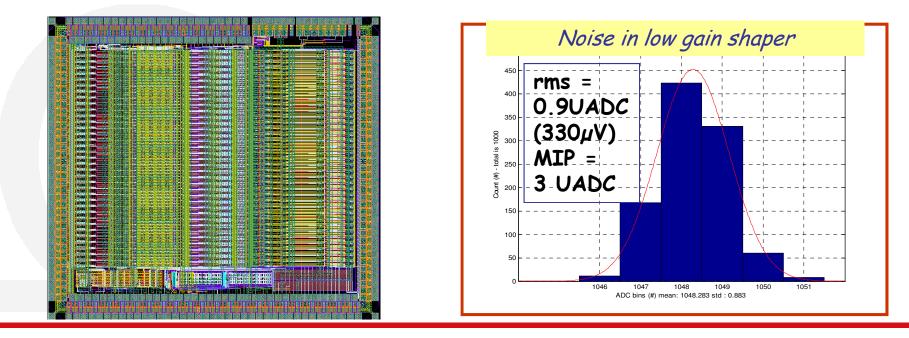

- Silicon Kalorimeter Integrated Read Out Chip (Nov 06)

- 36 channels with 15 bits Preamp + bi-gain shaper + autotrigger + analog memory + Wilkinson ADC

- Digital part outside in a FPGA for lack of time and increased flexibility, but cannot be used on an ASU or FEV

- Collaboration with LPC Clermont

31 aug 2009 EUDET SC

#### Status of JRA3 Front End Electronics

- SKIROC1 useless with detector (no readout)

- SPIROC2 used as SKIROC emulator

- 36 channels only

- Limited dynamic range (~500 MIPs)

- Tests starting with FEV7

- Noise tests on testboard proceeding (ENC  $\sim$  1 ke-)

- R&D will continue within CALICE

- SKIROC2 to be submitted with production run

- Expensive ASIC (70 mm2 = 70 k€) => MPW not worth it

- 64 channels

- 95% identical to SPIROC (only preamp differs)

# Test beam with technological prototype

- Data rate (Spiroc/Skiroc) : naive estimate

- Volume : 36ch\*16sca\*50bits=30 kbit/chip

- Conversion time :  $16*80 \ \mu s = 1.5 \ ms$

- Readout speed 5 MHz (could be increased to 10-20 MHz)

- 8 chips/DIF line (one FEV only)

- Total : 1.5ms + 30000\*200ns\*8 = 50 ms/16 events = 3 ms/evt => 300 Hz during spill

- Overall readout rate

- « Add » 1-10% power pulsing : 3-30 Hz effective rate

- Pessimistic as assuming all chips full

- Note : readout electronics designed for ILC lowoccupancy, low rate detector **#Testbeam** !!

### Summary

- 2<sup>nd</sup> prototypes of HARDROC (DHCAL) and SPIROC (AHCAL+ECAL) submitted in june 08

- DAQ part being validated with HaRDROC

- Power pulsing tests essential now at system level

- Front-end boards first prototypes coming in

- DAQ interface (DIF boards) prototyped

- Tests are very complex and essential

- Still need to validate noise, autotrigger, ADC, power pulsing with detector.

### Backup slides

31 aug 2009 EUDET SC

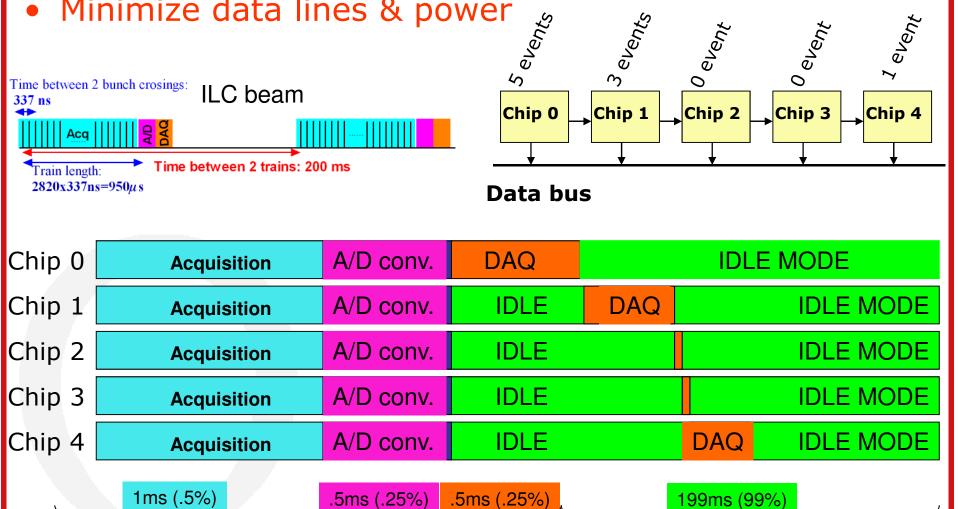

# Read out: token ring

- Readout architecture common to all calorimeters

- Minimize data lines & power

1% dutý cycle 99% duty cycle Status of JRA3 Front End Electronics 31 aug 2009 EUDET SC

# **SPIROC** : One channel schematic

31 aug 2009 EUDET SC

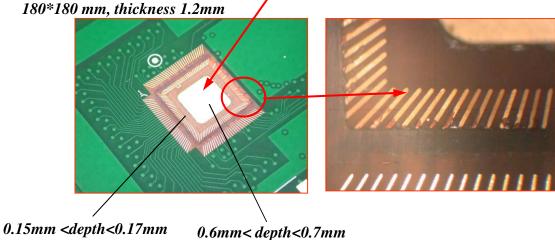

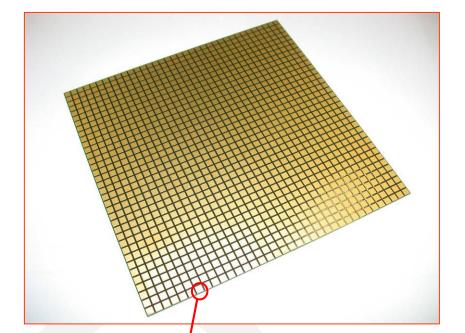

#### FEV5 : new PCB for ECAL

<u> Mega</u>

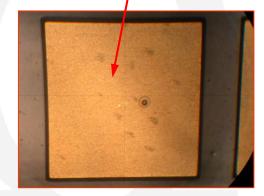

Global dimensions : 180\*180 mm, thickness 1.2mm

pixel dimensions : 4\*4 mm

31 aug 2009 EUDET SC