# Update report on SiPM Charge Readout Chip (KLauS) in Heidleberg

Title

Tobias Harion Wei Shen

Kirchhoff Institüt für Physik Universität Heidelberg

March 11 . 2010

Tobias Harion Wei Shen

KLauS update

March 11 . 2010 1

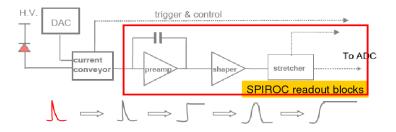

## Diagram of KLauS

- AMS  $0.35 \mu m$  CMOS technology , 4 channels

- shaping 25ns,50ns, 100ns ; scale factor 1,10,50

- SPI interface, 30 bits slow control

Tobias Harion Wei Shen

▲ ■ > < ■ > ■ >

March 11. 2010 2

Image: A math a math

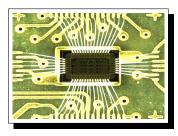

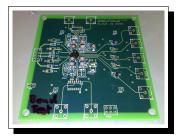

## Wire-bonded KLauS & test PCB

- FPGA connect via USB with PC

- slow control controlled by commands in Linux

- SPI to FPGA , normal 6 pins connector

(日) (同) (三) (三)

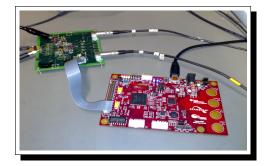

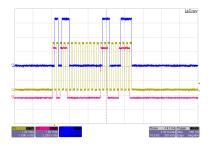

## Slow control & function test

SPI configured with FPGA

#### function test via charge injection

- Xilinx SPARTAN 3

- SPI data in = data out

- reponse after the shaper

- TTL trigger from CVY unit

(日) (周) (三) (三)

3

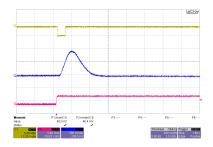

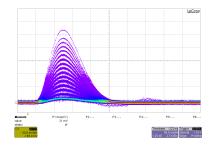

## Shaping, scaling & charge injection test

current scaling factor 1

shaping time & gain switch

- 3 sets of wfms, 25ns,50ns,100ns

- shaper gain : factor 2

#### charge injection test @ 40 fC

イロト イヨト イヨト

- assume gain  $2.5 \cdot 10^5$

- 1 pxl to 20 pxls

Tobias Harion Wei Shen

KLauS update

March 11 . 2010 5

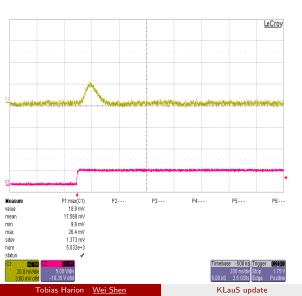

## Signal to Noise Ratio - current scaling factor 1

- charge injection 47pF

- input voltage

1mV, Q = 47pC

- $\bullet \ {\rm peak} = 17.6 \ {\rm mV}$

- RMS = 1.4 mV

- $\bullet~SNR$  for  $2.5\cdot10^5$

$$\frac{17.6mV\cdot40pC}{1.4mV\cdot47pC} > 10$$

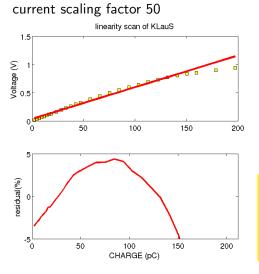

## Dynamic range & linearity

- dynamic range is related to linearity

- charge injected via 470pF

- dynamic range up to 150pC(±5% residual)

- ullet total range is  $12\sim13$  bits

5 · 10<sup>5</sup> gain 1600 pxls charge 128 pC

< □ > < ---->

## Trigger quality & SiPM bias tune

first tests on trigger walk and jitter

- THRD @ 0.5 pixel (20 fC)

- time walk 4.5 ns from 1 pxl to 20 pxls (40 fC/pxl)

- time jitter  $\sim$  700 ps

SiPM bias tune

- 0.8 V to 2.8 V range (3.3 V power supply)

- ullet in the whole range, peak variation < 1.5%

### Summary and Outlook

Summary

- Charge Readout Scheme is imeplemented and first results are positive

- SNR >~10 for gain  $2.5\cdot10^5$

- dynamic range goes up to 150 pC (linearity  $\leq$  5%)

- trigger walk  $\sim 5 ns$ , jitter < 1 ns, delay < 5 ns

- SiPM bias tune range of 2V

Outlook

- more measurements in the near future

- SiPM will be connected to the chip