# Developments and Planning towards 1 m<sup>3</sup> Technological DHCAL Prototype

Didier BON, Luigi CAPONETTO, Christophe COMBARET Didier DELAUNAY, Rodolphe DELLA-NEGRA, Hervé MATHEZ, Imad LAKTINEH, William TROMEUR

(CNR5 IN2P3 IPNL)

Collaboration with LAL

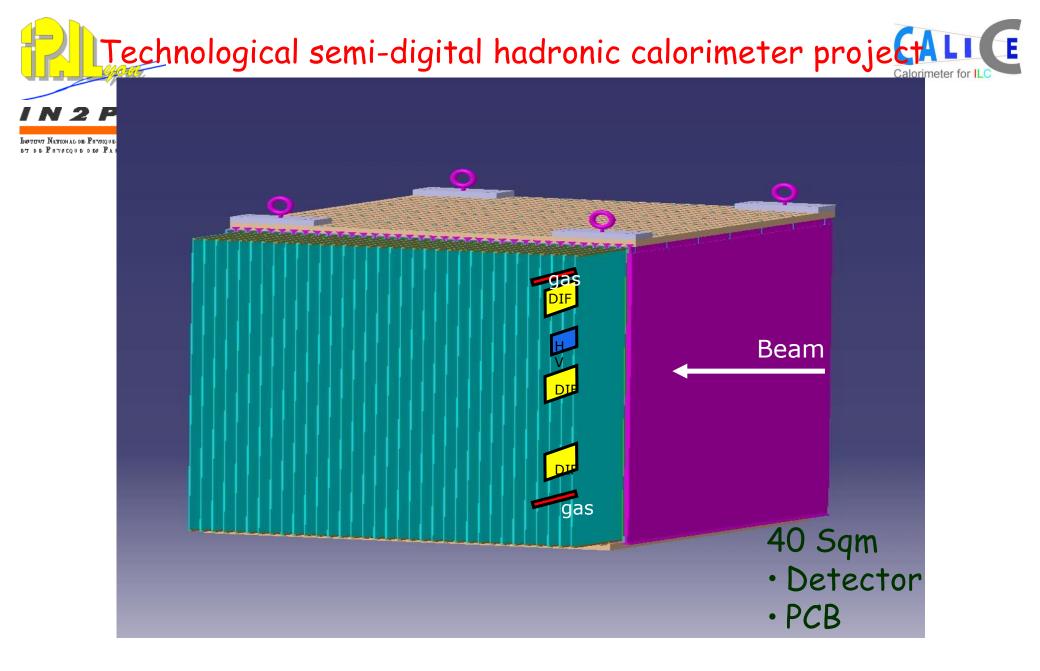

# 1 m<sup>2</sup> PCB MAIN SPECIFICATIONS

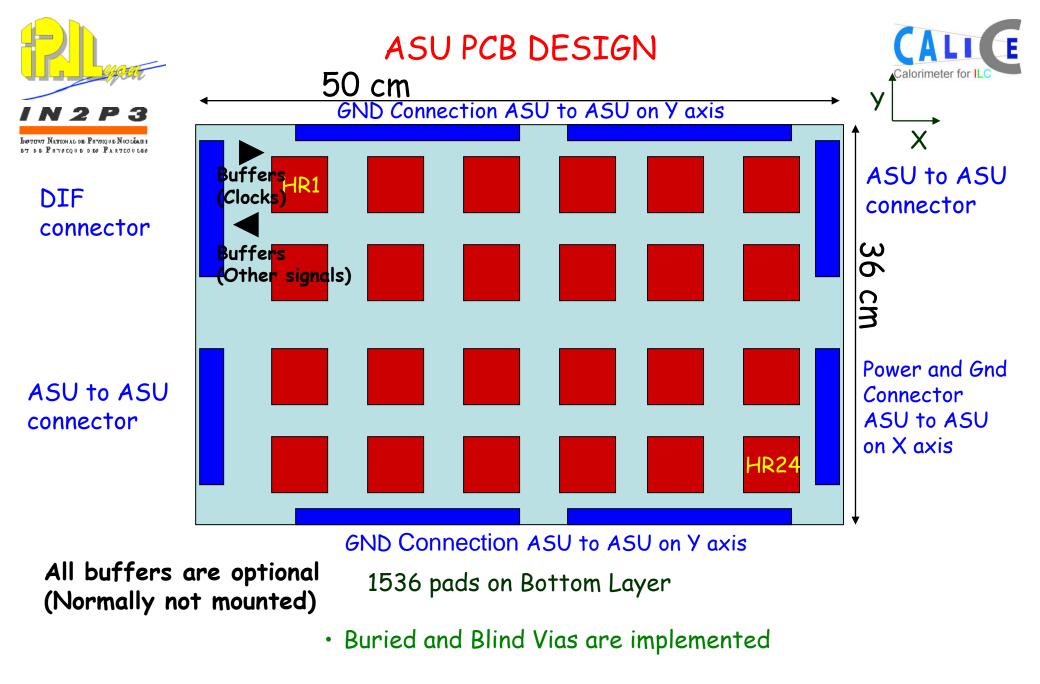

ASU PCB Design :

- 24 x 64 1 sq cm pads

- 24 Hardrocs Asics chained

- Plastic package (very thin 1.2 mm)

- 1 Sqm PCB board :

- 6 ASUs

- 144 Hardroc2

- DIF boards :

- 1 DIF for 2 ASU : 3 DIFs for 1 Sqm

#### HR2:

- $\checkmark$  All modifications are implemented from HR1 to HR2- HR2b

- ✓ SC bypass

- ✓ SC Clocking .....

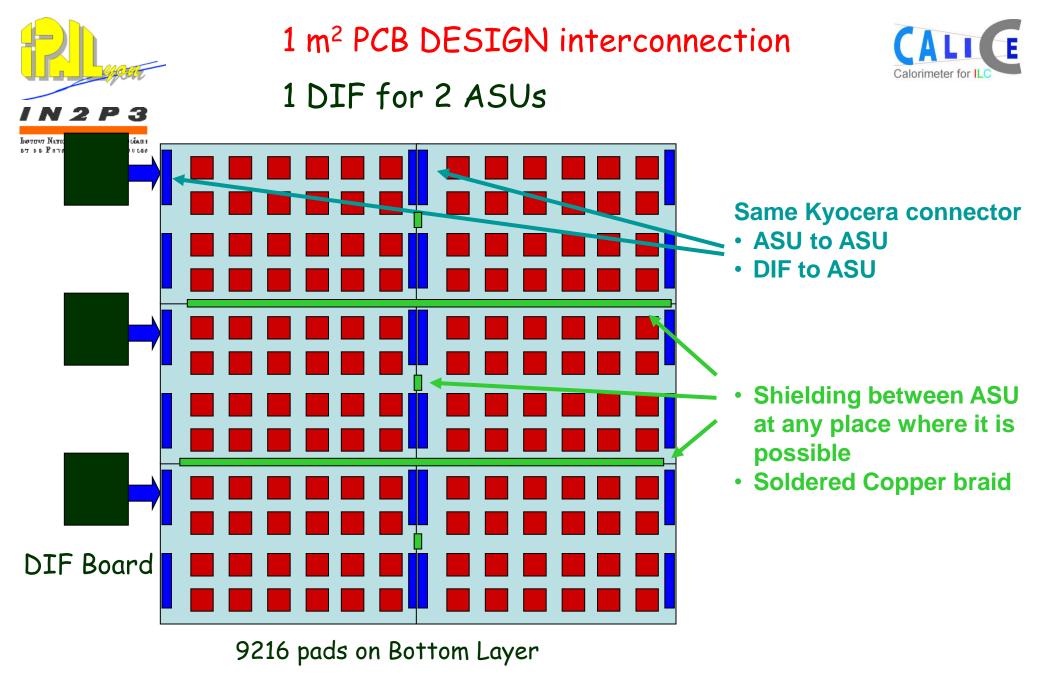

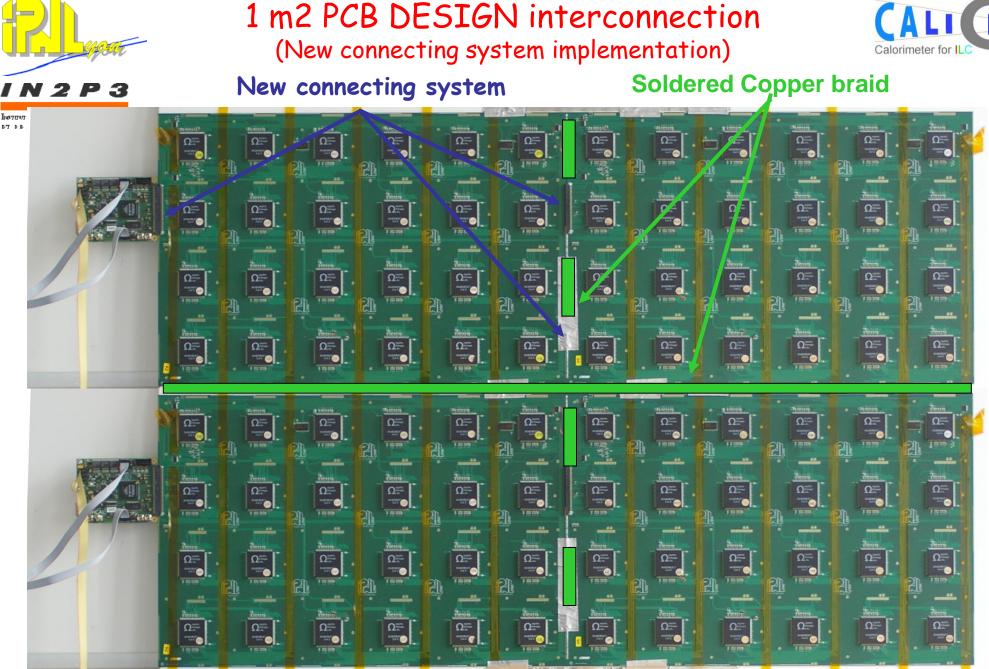

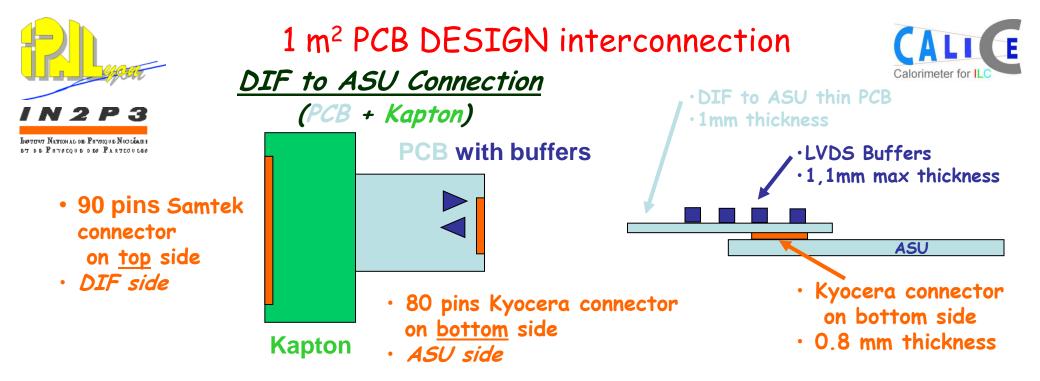

# 1 m2 PCB DESIGN interconnection

CALICE ECAL/AHCAL Electronics 5-6 July 2010 @ DESY L.Caponetto, H.Mathez

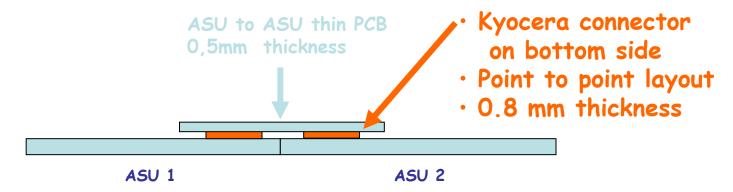

ASU to ASU Connection

#### 1 m<sup>2</sup> PCB DESIGN (Layers and upgrade)

Layer 1 (TOP) : interconnect Layer 2 : GND

NATION AL DE PHYSIQUE NUCCÉARE PHYSCOUL DES PARTCOULES

- Layer 3 : Digital signal 0

- Layer 4 : Power 0

- Layer 5 : GND 0

0

- Layer 6 : PADs to Hardroc

- Layer 7 : GND 0

- Layer 8 (BOTTOM) : PADs 0

o Pads to HR interconnects are the same for the entire PCB (hierarchical design)

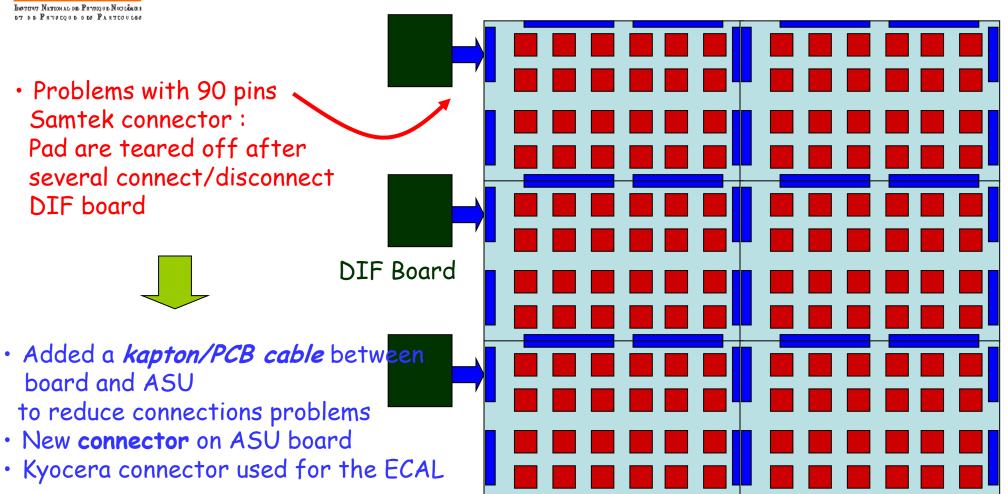

<u>ASU\_V2 upgrade to ASU\_V3</u>: mains modifications

- Samtek connector changed to kyocera connector

- DIF to ASU

- ASU to ASU

- Removed some buffers from ASU to "DIF to ASU" board

- LVDS buffers with enable power on

- SC clock buffer

- Added "Select" Pin (2 shift registers)

- Added holes to fix ASU during copper braid soldering (1 every 2 cm)

Powered by DIF board

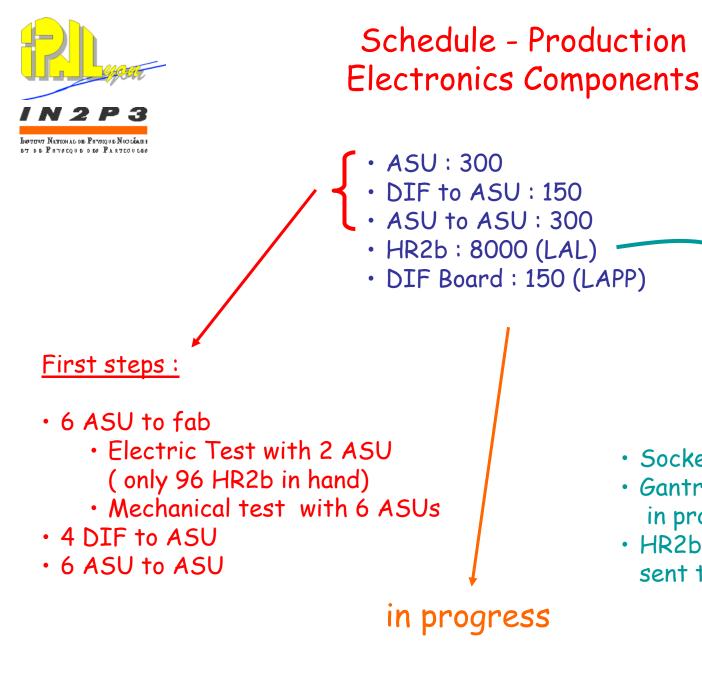

- Socket and Test board are OK

- Gantry and Socket modification in progress

- HR2b returned from foundry and sent to packaging

### ASIC HR2b testing

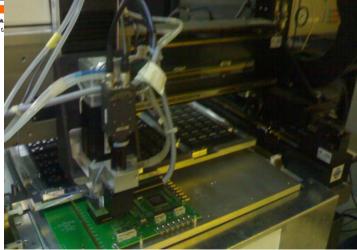

#### Gantry with and old PCB and Socket

LUTTUT NATIONAL DE PRIVIQUE NUCLÉR ET DE PRIVEQUE DES PARTCOUL

New PCB (designed @ LAL) and Socket from ARIES company

ASIC side

Spring probes connector PCB side

Socket Modifications are needed for Gantry use

## Companies Choice for PCBs and kaptons

ASU :

- Company : TECHCI COFIDUR group

- Mass production delocalized in China

- TECHCI usually works with this delocalized company

- First prototype (6 ASU) will be fabricated there

#### DIF to ASU, ASU to ASU :

• Company : TECHCI COFIDUR group

#### TECHCI had already fabricated all the previous ASUs and Kapton

- 4 HR1, 0.8mm thickness

- ASU\_V1

- ASU\_V2

- ASU to ASU kapton prototype

# Less risky choice : TECHCI

## Companies choice for assembling

- KEP Electronic (Paris-France)

- EMS COFIDUR Group (Périgueux-France)

- ProDesign (Paris)

- New company for us

- More risky

- Kep Electronic had fabricated all the previous ASUs

- 18 ASUs assembled and problems on 3 of them

- EMS is in the same group as TECHCI

- We hope the same quality !

```

Choice is still open

Less risky ??

```

# Planning

#### <u> Aggressive planning :</u>

- 6 ASUs return from Fab on 14 or 21 of July (3 weeks after purchase order)

- 2 ASU to ASU PCB (5 weeks after purchase order)

- 2 DIFF to ASU (3 weeks after purchase order)

- 2 ASUs + Interconnect assembling in <u>few days</u> !!!

- Testing before the end of July

- Send purchase order for the whole production before vacation

#### More realistic planning :

- 6 ASUs return fron Fab by the end of July

- 2 ASU to ASU PCB

- 2 DIFF to ASU

- 2 ASUs + Interconnect assembling during August

- Testing : beginning of September

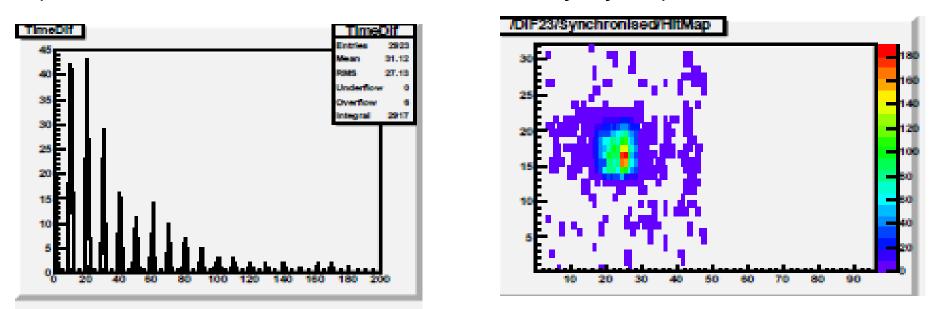

## Few results on Power Pulsing on large scale

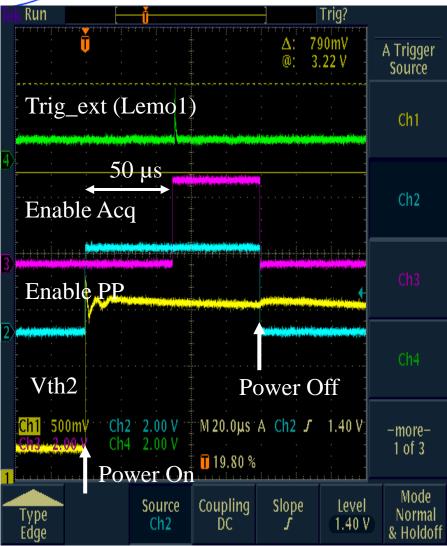

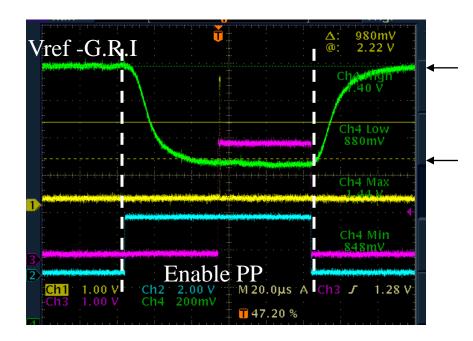

- Power pulsing was successfully tested on a 24-ASIC electronic board

- The board associated to a GRPC Was successfully tested in a 3-Tesla

B field in June (SPS-H2)

# Cycle of 2 ms power pulsing every 10 ms (100 Hz rather than cool 5 Hz ILC duty cycle)

Efficiency is almost the same (2% less) but this probably due to the acquisition starting time which is to be fine-tuned.

# Electronics: Power Pulsing on large scale

#### IN2P3

DEFTORT NATION OF PHYMICULATION 8 June 2010

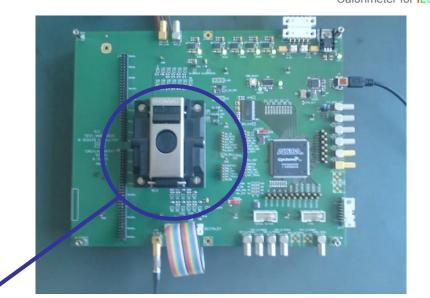

A small (50X34 cm2) detector was associated to a 24-ASIC board and put into a cassette.

The structure was put inside the supra magnet of

H2 beam line (3-Tesla solenoid)

# Conclusion

#### <u>ASU\_V3</u> • Mechatronic

- Modified Connector (Samtek , Kyocera)

- Added DIF to ASU board

- Added ASU to ASU board

- Added holes for 1 sqm assembly

- Electrical modifications to reduce power supply

- LVDS buffers with enable

- "Select" pin implementation

- Time to manufacturing increase due to this main modifications :(2 months)

- Technical study with TECHCI

- before mass production

- Delocalization required more detailed fabrication data exchange with TECHCI

Test bench for HR production characterization : in progress