#### AIDA Meeting Heidelberg

H.C. Schultz-Coulon Kirchhoff-Institut für Physik Universität Heidelberg

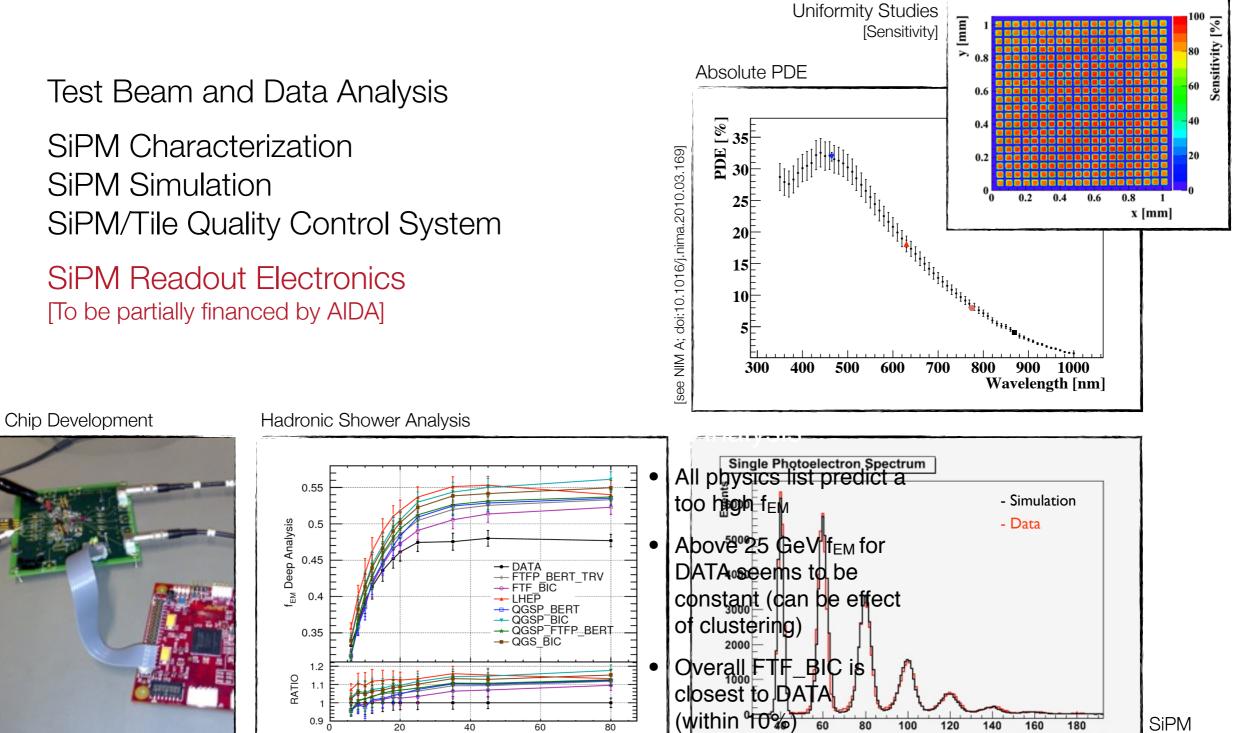

## CALICE Work in HD

Beam Energy [GeV]

Simulation

**QDC-Channels**

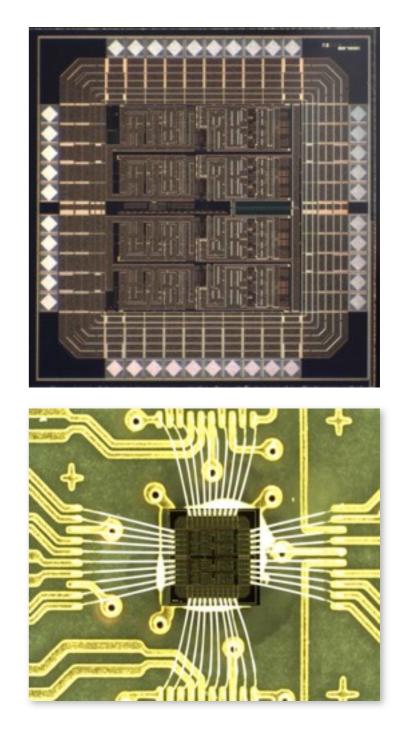

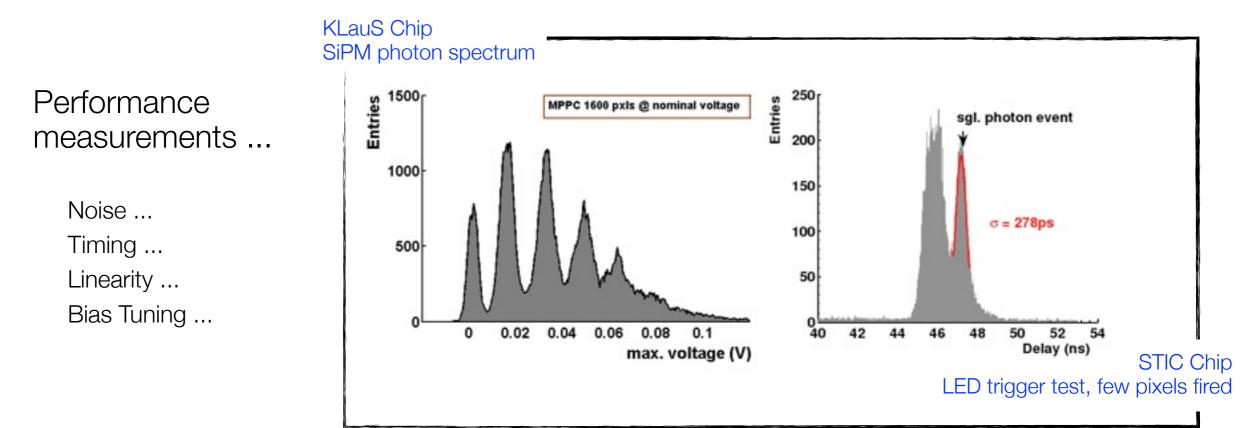

### ASIC Development in HD

#### Heidelberg:

Two test chips produced ... [financed by Helmholtz-Alliance]

KLauS: Kanäle für Ladungsauslese von SiPMs [Channels for Charge Readout of SiPMs]

AMS 350 nm CMOS technology; 4 channels; SPI interface controlled by FPGA; Bias DAC tunable; High signal/noise ratio [>10, 40 fC signal charge]; Fast trigger available [pixel signal jitter < 500 ps]; Large dynamic range up to 150pC

STIC: SiPM Timing Chip [Fast Discrimination for ToF]

AMS 350 nm CMOS , 4 channels; Leading edge & constant fraction trigger; Bias DAC tunable ~ 1 V; power < 10 mW/channel Pixel jitter ~300 ps, time of flight capability

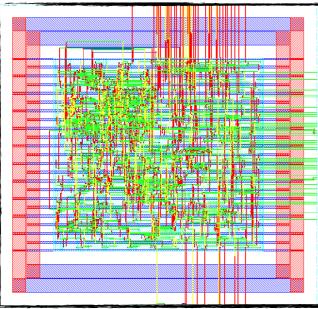

### ASIC Development in HD

#### I<sup>2</sup>C for KLauS 2.0

# Further upgrade plans ...

#### STiC 2.0:

. . .

Differential readout Tunable hysteresis

#### KLauS 2.0:

...

Power reduction Power pulsing I<sup>2</sup>C Interface Integration with SPIROC