In2p3

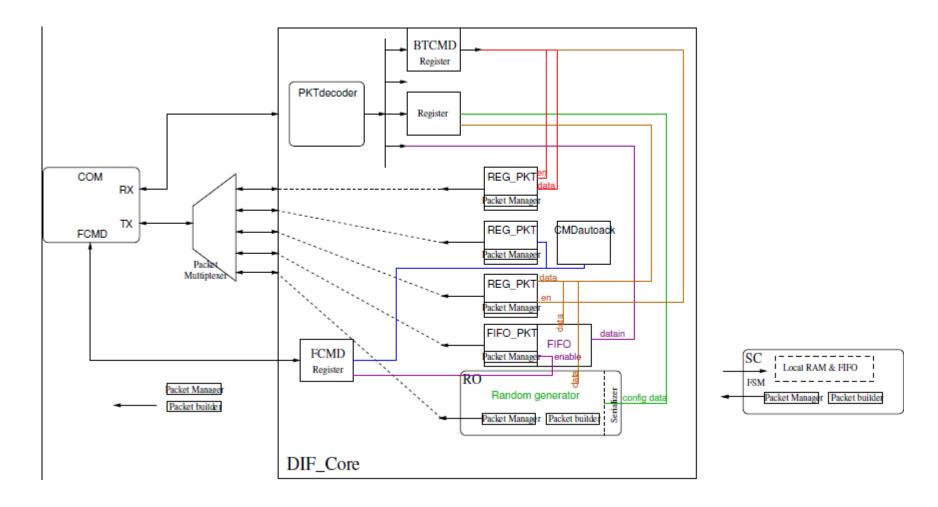

### DIF : basic version

# DIF firmware for testing DAQ

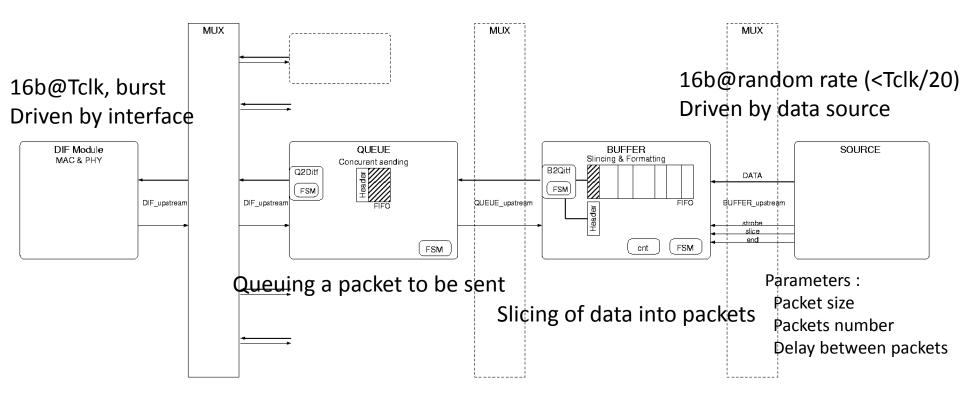

## TX buffers

Two levels of buffers Modular design with similar interfaces Handshake protocols, optional MUXs Random data source to perform system tests

Template code will exist by the end of July on our SVN repository

# Status of DIF tests

none March'10 : DIF working with a DCC board

- Serial link tested and validated

- Part of specifications of the hdmi side implemented

- Jugone : DIF working with a Dec + LDA Almo (almost) full specification

- - Including ROC chips functions (from Guillaume/Mathias)

- Ethernet I/O of the LDA

- September'10 : more that for the second working with a DCC +

- Synchronization with "final" poetes SW

- Full use of CCC

- Later on : to be discussed

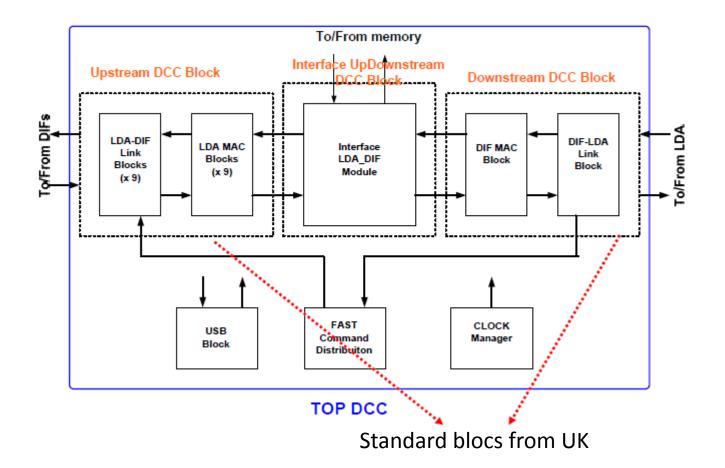

### **DCC** Firmware

- Firmware is under debug to manage 9 DIFs

- 2 kinds of access on DCC :

- USB : DCC is like a LDA

- DCC sends BTCMD or FCMD

- DCC read-out DATA from DIFs

- HDMI : True DAQ link

- LDA sends BTCMD or FCMD to the DIFs via the DCC

- Currently, only broadcasts are realized (no ID for the DIFs)

- LDA read-out the DATA from DIFs (one packet after the others)

6

### DCC firmware

The DCC is 99% transparent

### **DCC Schedule**

- Until August

- DCC (prototypes) tests on DAQ chain

- DCC Firmware:

- Everything works correctly

- Improvements (if necessary) will be always possible for the firmware on DCC production.

- Since two weeks :

- DCC boards in production

- 2 boards will be (in theory) received by the end of July before a "green light" for the launch of all the production

- We expected all boards at mid-October (it depends on the schedule of the company)

- By the end of the year : Boards should be ready for a test beam

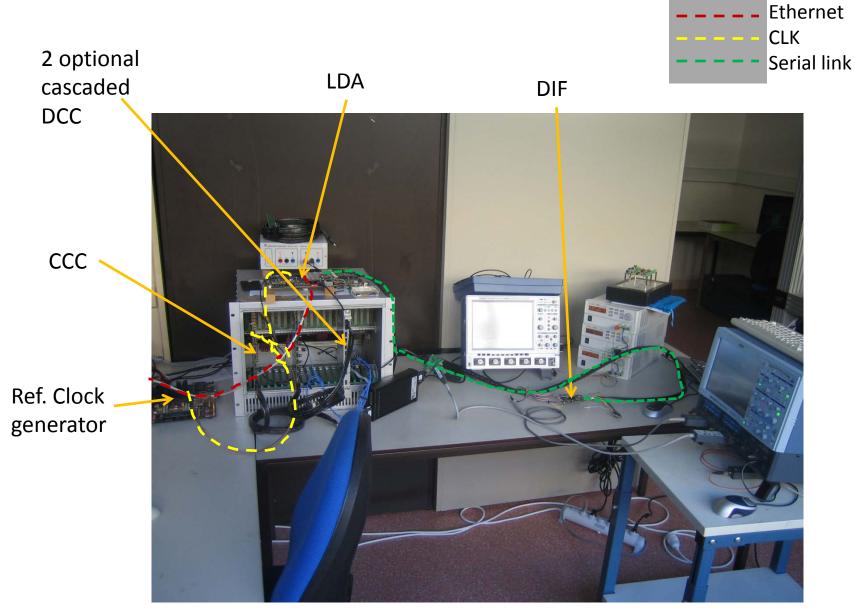

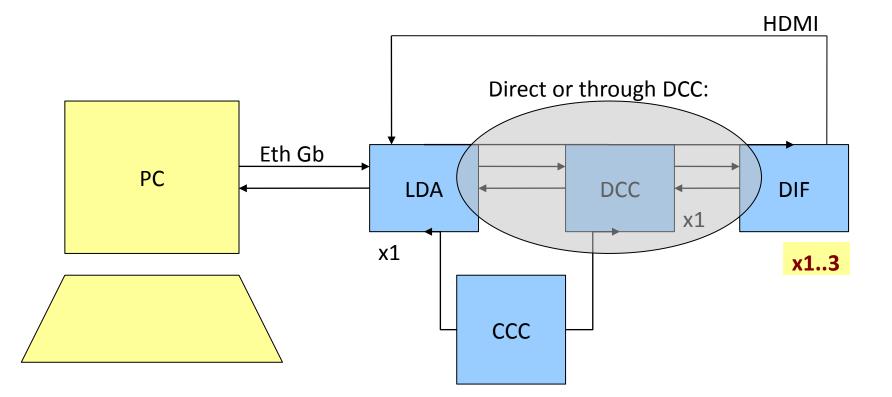

#### Tests with LDA/DCC/DIF (aka. "DAQ 2") at LLR

David Decotigny Franck Gastaldi

#### Test setup at LLR

### Test setup at LLR (cont.)

Tested data paths: PC(Ethernet) – LDA – DIF : 1x serial link PC(USB) – DCC – DIF : 1x serial link PC(USB) – DCC – DCC – DIF : 2x serial link PC(Ethernet) – LDA – DCC – DIF : 2x serial link

Clock from CCC replacing the local oscillator (TTL adapt.)

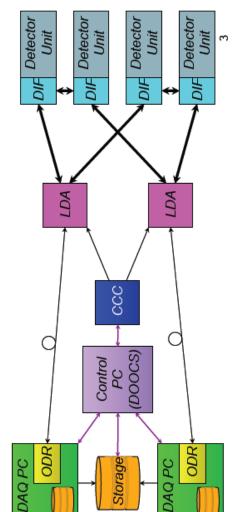

# Setup overview

Note: everything in this talk related to the HDMI+ethernet links (USB already validated in the past)

# Basic functionality tests (1/3) Methodology

• Done by hand using a GUI

|                   |                                                                                           | DIF2_remi.py                                                                                 |                                                             |                                                                 |

|-------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|

| Messages          | LDA_version                                                                               | LDA_get_DIF_status                                                                           | LDA_en_restart_links                                        | LDA_send_fast_command                                           |

|                   |                                                                                           |                                                                                              | Reset the LDA DIF links according to the mask               | Send a fast command to the<br>DIF(s)/DCC<br>Ida_out_mask 0x8    |

|                   | Send a packet to get the<br>LDA version                                                   | Read the 19 registers from bank 1<br>(DIF bank) of the LDA                                   | lda_out_mask 0x8                                            |                                                                 |

|                   |                                                                                           |                                                                                              |                                                             | comma 0x7c                                                      |

|                   |                                                                                           |                                                                                              | host_mac_addr :9d:49:71:8e                                  | data 0x22                                                       |

|                   | Run                                                                                       | Run                                                                                          | Run                                                         | Run                                                             |

|                   | send_FC_DCC_reset                                                                         | send_FC_DCC_get_status                                                                       | send_FC_DCC_init_links                                      | send_FC_DIF_reset                                               |

|                   | Send a fast command to reset the DCC (7c/10)                                              | Send FCMD K28.3/D15.0 (aka.<br>7C/D15.0, DCC get status)                                     | Send FCMD K28.3/D15.1<br>(aka. 7C/D15.1, DCC init<br>links) | Send FCMD K28.3/D1.1 (aka.<br>7C/21, reset DIF)                 |

|                   | lda_out_mask 0x8                                                                          | Ida_out_mask 0x8                                                                             | lda_out_mask 0x8                                            | lda_out_mask 0x8                                                |

|                   | Run                                                                                       | Run                                                                                          | Run                                                         | Run                                                             |

|                   | send_BT_DIF_command                                                                       | send_BT_DIF_write_debug_fifo                                                                 | send_FC_DIF_read_debug_fife                                 | send_BT_DIF_read_debug_fifo                                     |

|                   | Send a block transfer<br>command (DIF type<br>modifier) + 1 data word<br>Ida out link 0x3 | Write some data (24B pattern,<br>repeated num_patterns times) to<br>the<br>DIF internal fifo | Send FCMD K28.3/D2.1 (aka.<br>7C/22, read debug fifo)       | Send BT 0xe to read the<br>contents of the DIF internal<br>FIFO |

|                   | dcc_pkttype_nibble 0x5                                                                    | Ida_out_link 0x3                                                                             | lda_out_mask 0x8                                            | lda_out_link 0x3                                                |

|                   | command 0x12                                                                              | dcc_pkttype_nibble 0x5                                                                       |                                                             | dcc_pkttype_nibble 0x5                                          |

|                   | data Oxffff                                                                               | num_patterns 1                                                                               |                                                             |                                                                 |

|                   | Run                                                                                       | Run                                                                                          | Run                                                         | Run 🥥                                                           |

|                   | send_BT_DIF_config_rndger                                                                 | n_send_BT_DIF_read_bank                                                                      |                                                             |                                                                 |

|                   | Load Register bank 1 (DIF<br>peseudo-random packet<br>generator)                          | Read DIF REG bank (BTCMD X0012)                                                              |                                                             |                                                                 |

|                   | Ida out link 00x3                                                                         | lda_out_link 0x3                                                                             |                                                             |                                                                 |

|                   | dcc pkttype nibble (0x7)<br>rndpkt size (0x40)                                            | dcc_pkttype_nibble 0x5                                                                       |                                                             |                                                                 |

|                   | num mdpkts Z                                                                              | select_bank                                                                                  |                                                             |                                                                 |

| Reload<br>Script  | Run                                                                                       | Run                                                                                          |                                                             |                                                                 |

| Get_Status FCMD s | sent                                                                                      |                                                                                              |                                                             |                                                                 |

Each button = a custom python function, easy to write

EUDET, 05/07/SUPPOrts USB ARARS232 and Ethernet devices + remotely controlled devs (XML-RPC)

# Basic functionality tests (2/3) Tests descriptions

- Implemented and validated end-to-end tests:

- "FIFO":

- PC sends a "WRITE" block transfer to DIF, with data

- DIF stores data in its test FIFO

- PC sends a "READ" block transfer or fast-command request to DIF

- PC receives a block containing the full contents of the DIF's test FIFO

- "RNG" (pseudo-random generator) test:

- PC sends a block transfer to DIF to configure DIF's pseudorandom generator (nb blocks + size block)

- PC receives the requested number of blocks + with pseudorandom sequence

- Makes sure the pseudo-random is correct wrt RNG polynome

# Basic functionality tests (3/3) Outcome

- Validated "by hand" with the GUI:

- <u>Without</u> DCC, single DIF:

- Fast-Commands PC->DIF

- Block transfers PC->DIF

- Block transfers DIF->PC

- <u>Through</u> DCC, **single** and **dual** DIF:

- Fast-Commands PC->DIF

- Block transfers PC->DIF

- Block transfers DIF->PC

#### Basic connectivity with LDA + DCC is here !

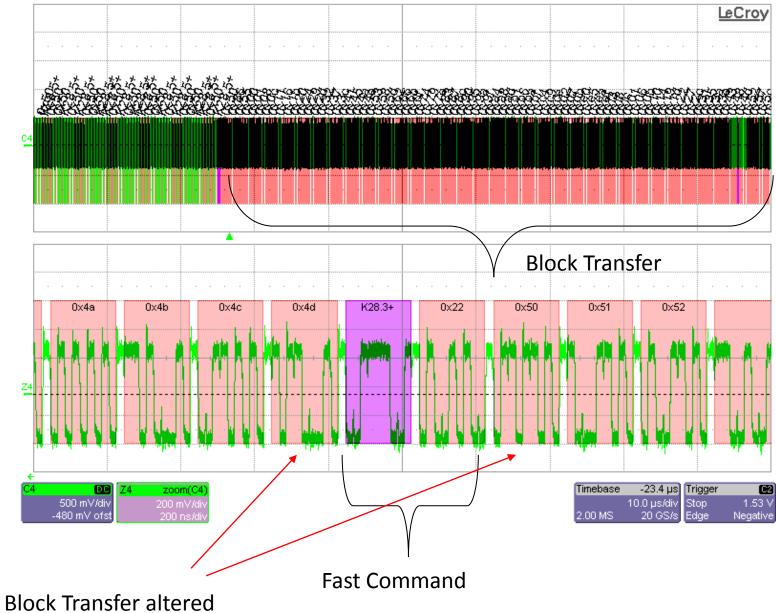

# More intensive tests (1/2) Methodology

- A series of C/C++ low-level tests

- FIFO tests:

- In a tight loop: write data to DIF test FIFO + read-back and compare

- Data = random number of random bytes

- Needed to insert a small delay between packets due to firmware issues (=> impairs throughput)

- RNG tests:

- In a loop: request 300 packets of 0x22 16b words from DIF and compare with reference pseudo-random sequence

« Infinite » number of packets is being tested now at LLR

# More intensive tests (2/2) Outcome

- With and without DCC, single DIF:

- FIFO test:

- BER < 5.10<sup>-12</sup> (full weekends, no error)

- Mean throughput = 4.7 Mbps in each direction (readjusted to hide the 1ms delay; 3Mbps not readjusted)

- RNG test:

- Full weekends tests, no error

# Issue 1

#### Issues

- Need of a mezzanine to connect LDA and CCC

- Hardware available, require firmware modifications

- Trigger and busy fan out/in

- HDMI mezzanine of the LDA may need some modifications to enable all the channels

- Cable adaptation

Our colleagues from UK are working on that

- Routing & Pins assignment

- System tests and data integrity

- Under some condition, failure to acquire data correctly. It is under investigation (using various data generation parameters to change the mean/peak data rate).

# Work ahead

- UCL/Cambridge:

- LDA firmware updates Our colleagues from UK are working on that

- Multi-link support (for now 6 channels available, one at a time)

- Various timing and buffer issues (data corruption observed)

- A few features needed (eg. DIF link identification)

- LLR:

- Single DIF intensive tests, ctd:

- "Continuous" RNG: would allow to measure precise 1-way throughput

- Multi-DIF intensive tests through DCC

- Not working yet (data corruption), but may be a buffer or a clocking issue (will investigate with firmware triggers and/or premium scope)

- Multi-DIF intensive tests without DCC (direct LDA)

- Original firmware: data corruption observed, LDA freezing

- May need to upgrade when new firmware released

But firmware of DIF, DCC and LDA is at a development stage

# Outcome

- Firsts steps toward the CALICE DAQ

- Main mechanisms of data exchange have been tested

- 50 MHz clock

- Data integrity with SW loop

- DIF Firmware is being developed

- Functions to store SC data and manage ROCs

- Common work done within the DIF task force

- Newcomer at LLR to work on DIF & DAQ (Oct.)

- Very first detector operation foreseen this summer on Si-W ECAL prototype (1 ASU, 1 chip)

- Could be extended to other detectors

- Please wait for the system to be fully debugged

- Support from LLR possible

- We do not work on LDA for the moment

- updated code ?

- Sharing of responsibilities to be clarified