#### ASU boards for RPC detectors

Production status

### Presentation outline

- Active Sensor Unit electronic board for GRPC detectors

- quick reminder

- board functional decomposition

- testing issues

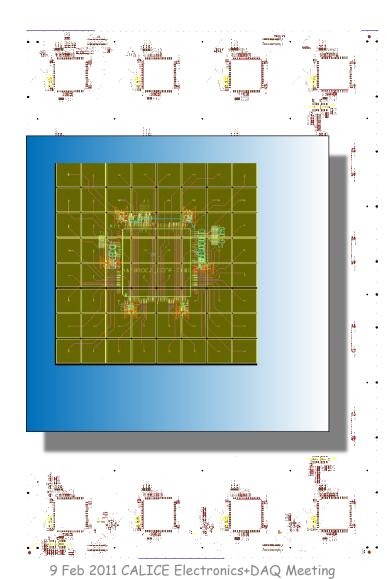

- square meter (m2) board

- reminder

- integration scenario

- m2 boards production: provisional plan

#### ini The ASU board: reminder

- 2 main functions:

- interface

- front-end electronics <-> GRPC

- functional support for 24 HARDROCs

- boards production outsourcing:

- 2 different firms for PCB + board manufacturing

- boards checked and reconfigured at IPNL

- products quality checks:

- PCB: production samples

- board manufacturing: visual inspection

- functional checks performed at IPNL

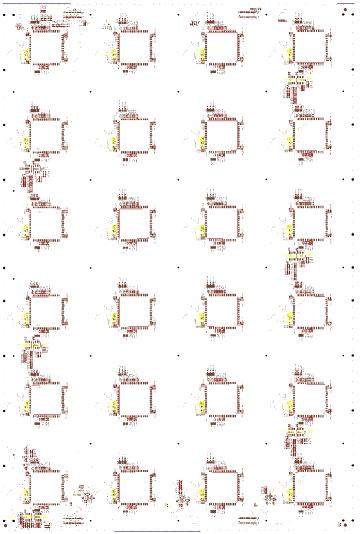

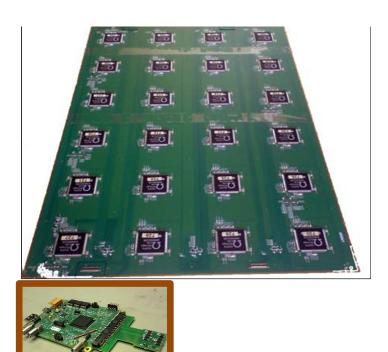

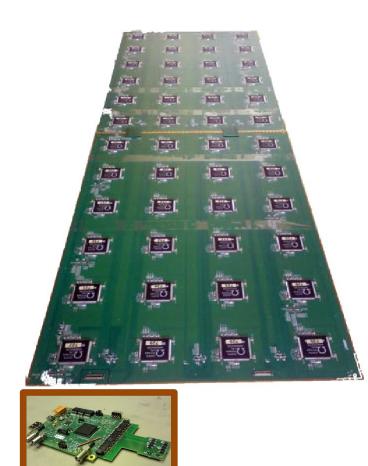

#### HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

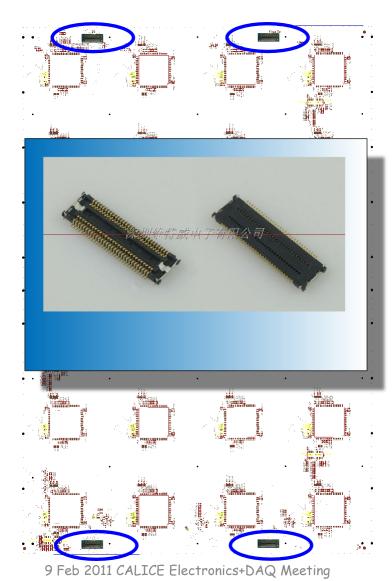

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 3 ASU board configurations

- 310 closed straps (362 total)

- 22 matched lines terminations

#### HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

#### • HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

- HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

- HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

- HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

- HARDROC (HR)

- 24 asics/board

- all asics daisy chained

- only active device

- input pads

- 64 pads/HARDROC (1 cm2)

- board BOTTOM side

- interconnections

- 4x 80pin smd connectors

- pwr supply + HR ctrl data

- board configurability

- 310 closed straps (362 total)

- 22 matched lines terminations

- 3 ASU board configurations

# ASU board: 3 configurations

#### only 2 cfg used for m3 integration

- "production" cfg only used for single board testing

- "slab 1st" + "slab 2nd" used in slab integration

- different configurations made by straps and passive components

- test strategy:

- all configurations need to be checked

- all integration steps need to be tested

## 💬 ASU board: test strategy

- functional test at each integration stage:

- the "production" board must pass a functional test

- boards are reconfigured either as "slab 1st" or "slab 2nd"

- the slab is functionally tested

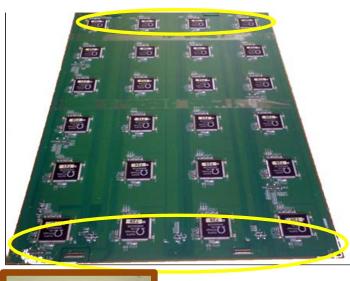

- 3 slabs are integrated in a m2 board

- the m2 board is functionally tested before integration with the GRPC

- the m2 is integrated into his cassette

- the integrated cassette must pass a complete functional test

- two separate test benches will be used

- functional tests: GO / NO GO strategy

## MSU board: test strategy

- functional test at each integration stage:

- the "production" board must pass a functional test

- boards are reconfigured either as "slab 1st" or "slab 2nd"

- the slab is functionally tested

- 3 slabs are integrated in a m2 board

- the m2 board is functionally tested before integration with the GRPC

- the m2 is integrated into his cassette

- the integrated cassette must pass a complete functional test

- two separate test benches will be used

- functional tests: GO / NO GO strategy

### ASU board: test strategy

- functional test at each integration stage:

- the "production" board must pass a functional test

- boards are reconfigured either as "slab 1st" or "slab 2nd"

- the slab is functionally tested

- 3 slabs are integrated in a m2 board

- the m2 board is functionally tested before integration with the GRPC

- the m2 is integrated into his cassette

- the integrated cassette must pass a complete functional test

- two separate test benches will be used

- functional tests: GO / NO GO strategy

# Masu board: test strategy

|   |    |     |          | æ, |     |                        |             |               |               |  |

|---|----|-----|----------|----|-----|------------------------|-------------|---------------|---------------|--|

|   |    |     |          |    |     |                        |             |               | , <u>E</u> ]. |  |

| E |    |     |          |    |     | <b>,</b> [ <b>1</b> ], | E           |               | <b>.</b>      |  |

|   |    |     |          |    |     |                        | Ð           | Ш.            | <u>E</u>      |  |

| E | E. | .13 |          |    |     |                        | 1           | <b>([</b> ]). | , 🛄 ,         |  |

|   |    |     |          | .0 |     |                        | <u>, II</u> |               |               |  |

|   |    |     |          |    |     | . <b>D</b> .           |             | E.            | <b>.</b>      |  |

|   |    |     |          |    |     | E.                     |             | E.            | E.            |  |

|   |    |     |          |    | E   |                        |             | E)            |               |  |

|   |    |     |          | E. |     | E.                     | <u>, E</u>  | <b>.</b>      | . <u>E</u>    |  |

| E |    |     | <b>(</b> |    |     | E                      |             | Æ.            | <u>الله</u>   |  |

| 1 |    |     |          |    | .D. | E.                     | <b>D</b>    |               | ,E            |  |

- functional test at each integration stage:

- the "production" board must pass a functional test

- boards are reconfigured either as "slab 1st" or "slab 2nd"

- the slab is functionally tested

- 3 slabs are integrated in a m2 board

- the m2 board is functionally tested before integration with the GRPC

- the m2 is integrated into his cassette

- the integrated cassette must pass a complete functional test

- two separate test benches will be used

- functional tests: GO / NO GO strategy

### ASU board: test strategy

|     |            |  |          | E |     |                |               | .D            |              |   |

|-----|------------|--|----------|---|-----|----------------|---------------|---------------|--------------|---|

|     |            |  |          |   | E.  | E.             | ,E            |               |              |   |

|     |            |  |          |   |     | <b>.</b>       | <b>.</b> []   | <b>([</b> ]). | . <u>E</u> . |   |

| in. |            |  |          |   |     |                |               | Ш.            | <u>, E</u>   |   |

|     | . <b>D</b> |  |          |   |     |                |               |               | E.           |   |

|     |            |  |          |   |     | , <b>E</b> ).  |               | <b>, []</b>   |              |   |

|     |            |  |          |   |     | . <u>II</u> ). |               |               | E.           |   |

| -   |            |  |          |   | (D. |                | D.            | E.            |              |   |

|     | E          |  |          |   |     | E              |               |               |              |   |

|     |            |  |          |   |     | JE)            | E             |               |              |   |

|     |            |  | <b>1</b> |   |     | . <u>II</u> ). | . <b>E</b> }. | E.            |              |   |

| D   |            |  | II.      | E |     | .III           |               |               | . <u>E</u>   | Ē |

- functional test at each integration stage:

- the "production" board must pass a functional test

- boards are reconfigured either as "slab 1st" or "slab 2nd"

- the slab is functionally tested

- 3 slabs are integrated in a m2 board

#### • the m2 board is functionally tested before integration with the GRPC

- the m2 is integrated into his cassette

- the integrated cassette must pass a complete functional test

- two separate test benches will be used

- functional tests: GO / NO GO strategy

•

#### in board/slab/m2 test benches

- two separate test benches:

- 1 pc with XDAQ

- DIF + DIF-ASU boards

- 1 GRPC + HV

- DAQ software

- GO / NO GO strategy

- no debugging

- only functional tests:

- power consumption

- HR slow control

- pedestal acquisition runs

- HR calibration feature (CTEST) goals:

- checking all functionalities/connections

- electronics checks at each integration step

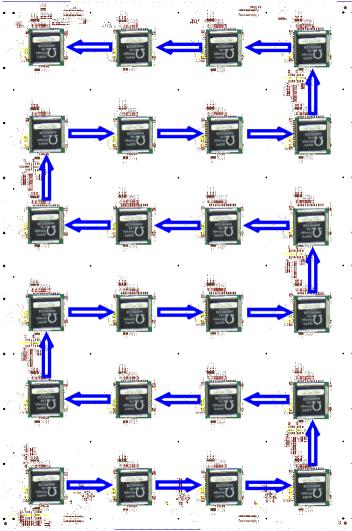

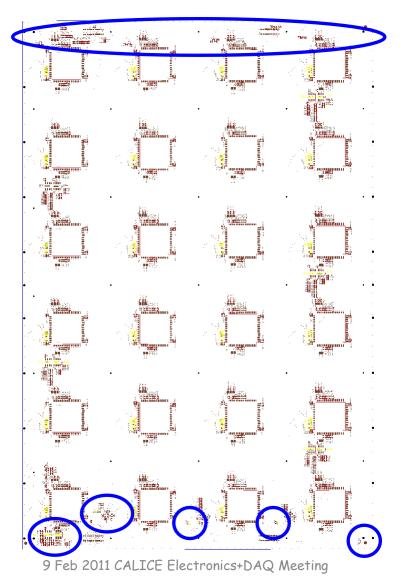

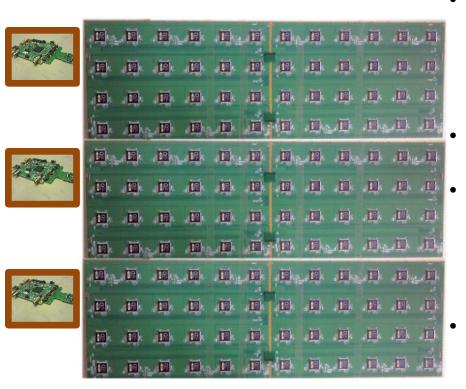

### m2 integration scenario

- components:

- 6x ASU boards

- 6x ASU-ASU interlinks

- boards and interlinks already configured and tested before integration

- integration procedure:

- ASU boards soldered together by the mean of copper gasket

- m2 board tested as a whole

- goal: one m2 board/day

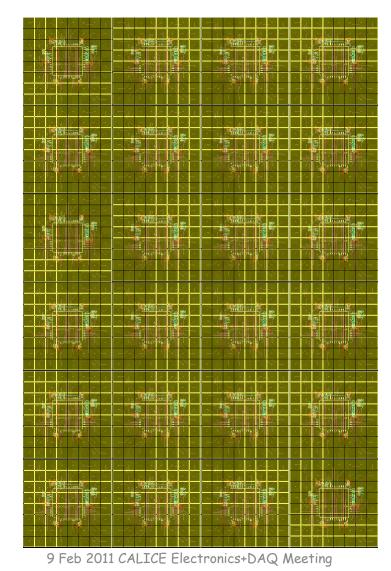

# m2 boards mass production

- production numbers:

- prototypes + 300x ASU + 330 ASU-ASU + 152 DIF-ASU

- prototypes:

- 6 ASU V3.1 + 6 ASU-ASU V2 + 6 DIF-ASU V2

- pre-series (mass production conditions):

- 20 ASU + 30 ASU-ASU + 12 DIF-ASU

- series:

- 280 ASU + 300 ASU-ASU + 140 DIF-ASU

- pre-series validates mass-production (integrated into M3)

- tests:

- ongoing tests of ASU preseries show unexpected HR mortality

- 6 + 20 boards tested: 25 / 624 asics found defectives

- symptom: "floating" pads

- investigations ongoing with Omega designers

### provisional planning and conclusion

- status:

- ASU(PCB) series launched

- HR mortality -> failure analysis ongoing

- ASU test bench protocol for early identification

- DIF-ASU and ASU-ASU preseries (manufacturing) launched

- provisional planning:

- ASU series (1st lot availabile on week 12)

- AST + radiography to assess infant mortality of HARDROCs

- test of the DIF-ASU and ASU-ASU preseries

- launching of the DIF-ASU and ASU-ASU series (board manufacturing)

- ASU boards mass production (capability: 60boards/week)

- start m2 boards integration and test (1m2/day)