MICROMEGAS Read-Out Chip

CALICE electronics meeting LLR-Palaiseau, France feb 9<sup>th</sup>, 2011

#### R. Gaglione and N. Seguin for the MICROMEGAS DHCAL team

Laboratoire d'Annecy-le-Vieux de Physique des Particules, Université de Savoie, CNRS/IN2P3 FRANCE

February 9<sup>th</sup>, 2011

#### Introduction

Tests at LAPP

Tests at LAL

#### Introduction

Tests at LAPP

Tests at LAL

## Introduction

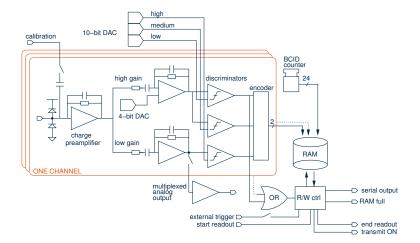

MICROROC is a 64 channels integrated circuit packaged in TQFP160 intended to be used with MPGD-based DHCAL (MICROMEGAS or GEM).

- MICROROC is a fruit of the collaboration between LAPP and LAL/OMEGA based on the experience of previous ASICs (DIRAC and HARDROC) and on multiple test beam results

- Same Digital part as HARDROC2b, but charge preamplifier input stage + sparks protection [R. Gaglione] and slower shaping + 4-bit DAC offset correction per channel [N. Seguin]

MICROROC is pin a pin compatible with the HARDROC2b to minimize boards modifications (see Cyril's talk).

gaglione@lapp.in2p3.fr feb 2010

### Global architecture

## Performances

- Technology: AustriaMicroSystem SiGe 0.35 µm

- Die size: 4.85×4.3 mm

- Dynamic range: 500 fC

- C<sub>det</sub>: 80 pF

- Preamplifier gain: 2.38 mV/fC

- Noise rms: 1 fC at preamplifier output, 0.24 fC with 200 ns shaping

- Peaking times: 30, 50, 100 and 200 ns

- Minimum threshold:  $\sim 2 \text{ fC}$

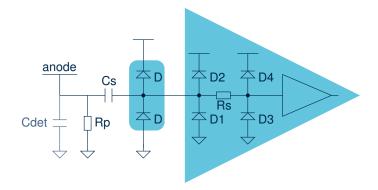

### Protection against sparks

Rp=1 M $\Omega$ , Rs=10  $\Omega$ , Cs=470 pF, D are ON-Semiconductor NUP 4114, Dx are integrated fast diodes.

#### Introduction

#### Tests at LAPP

Tests at LAL

### Test bench

# The test board and labview software have been provided by $\mathsf{OMEGA}/\mathsf{LAL}.$

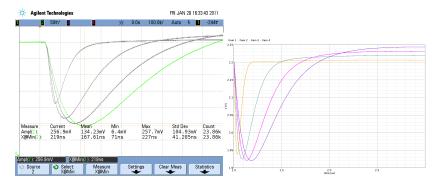

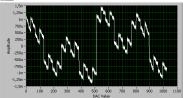

### Waveforms

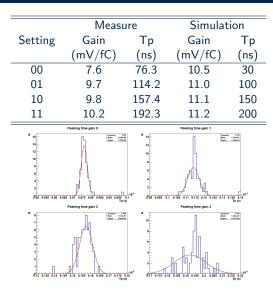

This is the output of high gain shaper, for the for settings (measure against simulation), with 25 fC charge injection (MIP-MPPV):

Good agreement between simulation and real behaviour.

### Shapers

Good agreement between simulation and real behaviour.

Tests at LAPP

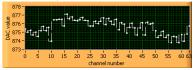

### Thresholds DAC

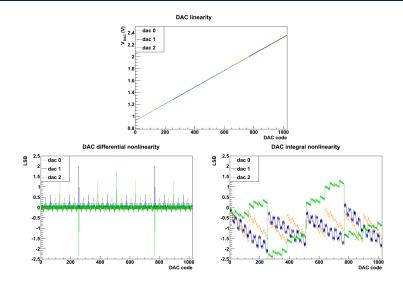

For each DAC, the linearity is about 3 DACU.

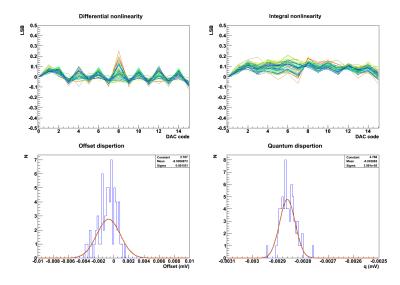

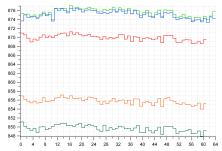

### Offset correction DAC

The linearity is better than 1 DACU and q=2.8 mV.

Tests at LAPP

#### Introduction

Tests at LAPP

Tests at LAL

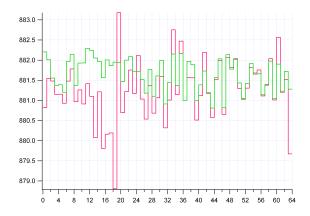

#### Pedestals compensation

V\_avg= 881.2 DACU V\_sdev= 0.74 DACU V\_avg= 881.6 DACU V\_sdev= 0.4 DACU

Difference before and after correction, for high gain shaper: 2 factor on pedestal dispertion !

gaglione@lapp.in2p3.fr feb 2010

Tests at LAL

### Threshold DAC tests

#### dac0 slope: 1.37 mV/*DACU* 942.06 mV to 2.34 V

dac1 slope: 1.38 mV/*DACU* 943.32 mV to 2.35 V

#### dac2 slope: 1.37 mV/*DACU* 943.35 mV to 2.34 V

#### INL: $\pm$ 1.5 mV

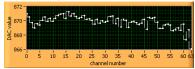

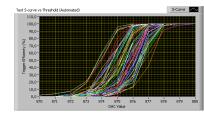

### Scurves measurements Cdet=88 pF

50% estimation per channel

Pedestal:  $V_avg = 875.6$ ;  $V_sdev = 0.85$

pedestal, 1 fC,2 fC, 4 fC,5 fC

50% estimation per channel

2 fC:  $V_avg = 869.9$ ;  $V_sdev = 0.65$

#### Introduction

Tests at LAPP

Tests at LAL

## Status

#### Prototypes tests

The chip has been sent in MPW run in June 2010 and 5 prototypes have been received in September 2011. The behaviour of the prototypes is very satisfaying.

#### Production

After prototypes tests in LAL and LAPP, an order has been placed for 350 chips. 341 chips have been received last week, and tests should be started very soon !

A production HR2b board has flashed with DIF firmware (see Guillaume's talk) and is used with LAPP Labview to test the 341 chips.