# Second generation DAQ for CALICE test beam

Vincent Boudry LLR, École polytechnique

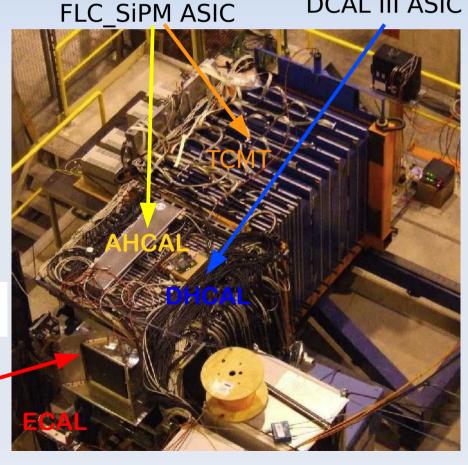

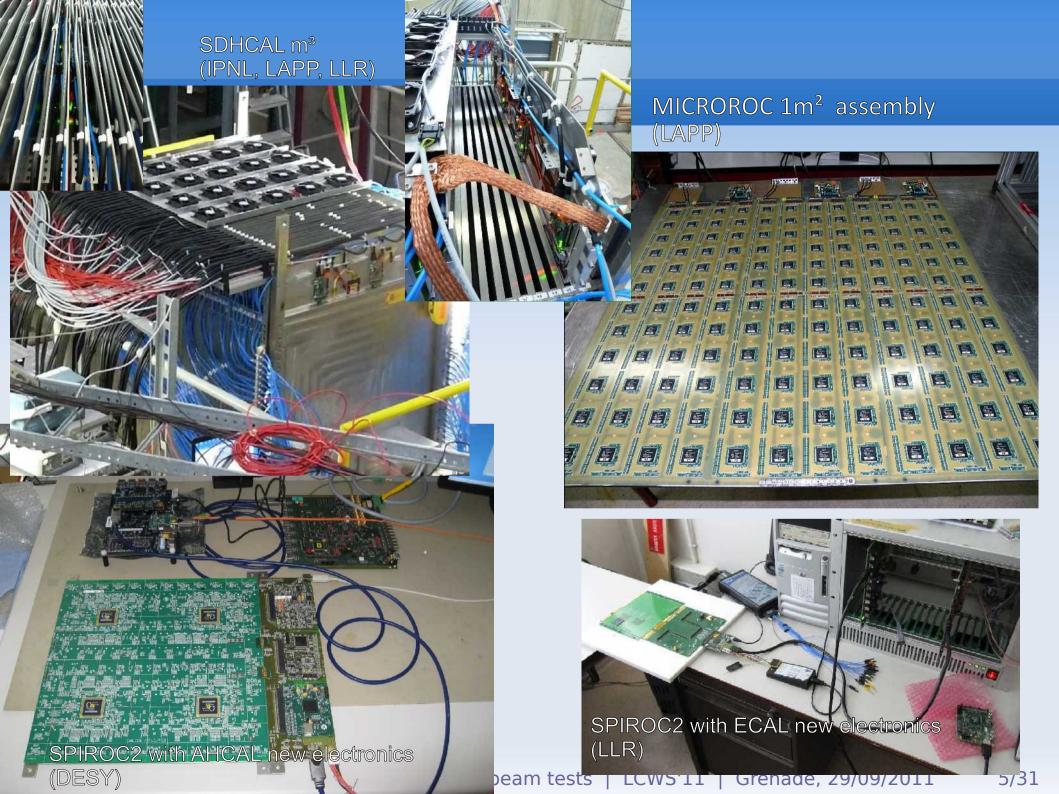

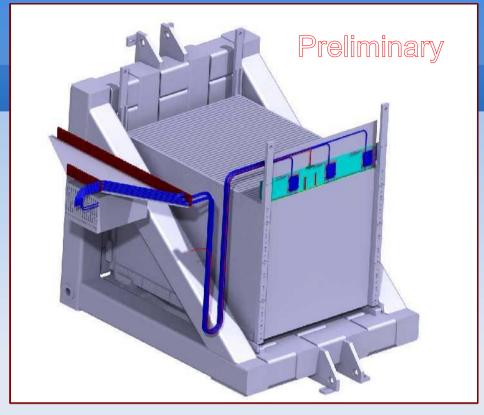

# **CALICE** collaboration Physical prototypes

### **Prototypes**

- ► Si-W ECAL, ScW ECAL (Scint+MPPC)

- ► AHCAL (Scint + SiPM/Fe)

- ▶ DHCAL (RPC + DCAL III / Fe)

- ► TCMT (Scint+SiPM or RPC+DCAL / Fe )

- Readout of FLC\* analog pipeline

- External ADCs & Sequencing

#### **DHCAL DAQ**

Readout of DCAL digital pipeline.

▶ Dead time free triggered readout

DCAL III ASIC

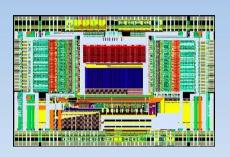

### ROC family 2nd Generation ASICs

()mega

FE electronics adapted for the ILC:

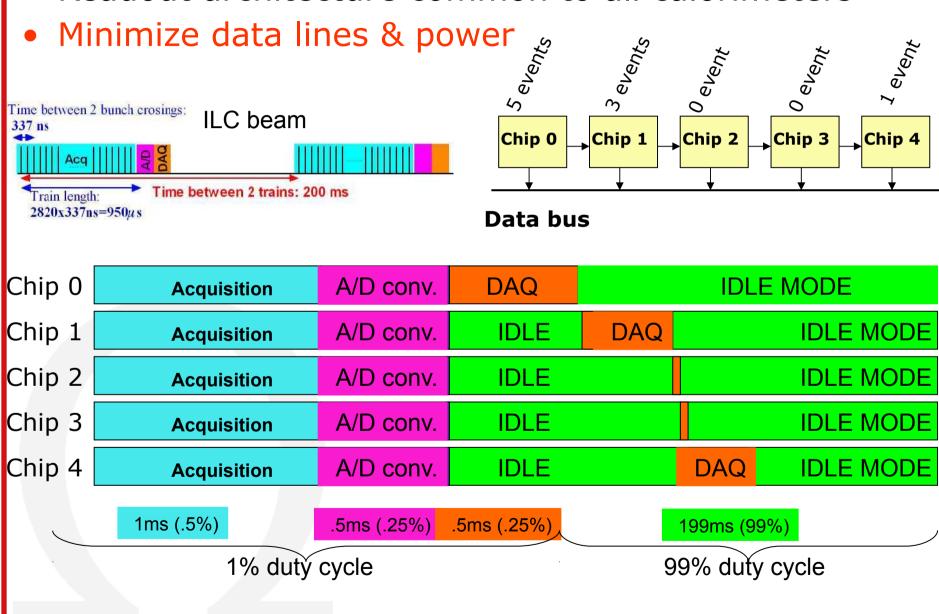

Add **auto-trigger**, analog storage, digitization and token-ring readout !!!

Include power pulsing : <1 % duty cycle

Address integration issues asap

Optimize commonalities within CALICE (readout, DAQ...)

#### **HARDROC2**

SDHCAL RPC 64 ch 16 mm<sup>2</sup>

FLC PHY3 (2003)

**MICROROC** SDHCAL μMegas

SKIROC2

**ECAL Si** 64 ch. 70 mm<sup>2</sup>

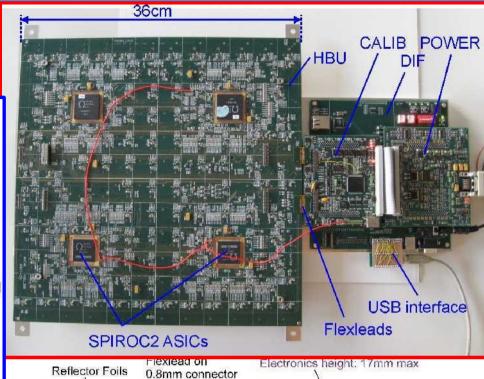

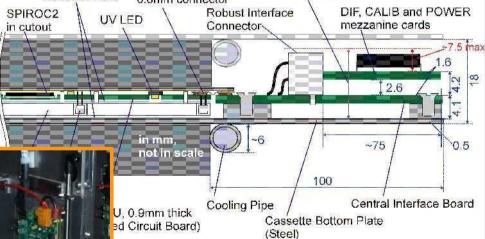

SPIROC2

**AHCAL SIPM** 36 ch 30 mm<sup>2</sup>

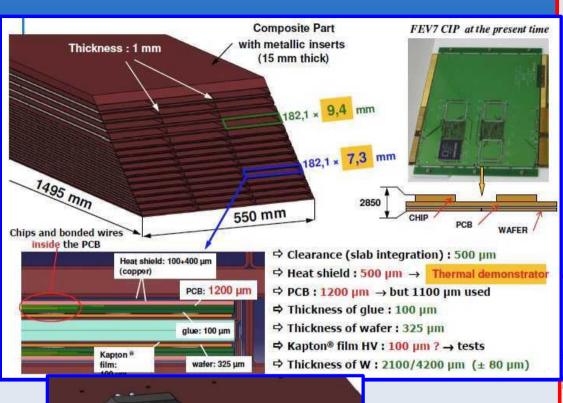

**Technological prototypes**

Adapted from Ch. de la Taille

### Read out: token ring

Readout architecture common to all calorimeters

Slide from Ch. de la Taille

# **DAQ Task goal**

Original ideas and R&D from CALICE-UK (UCL, Cambridge U., Manchester U., RHUL)

- "Generic" DAQ based AMAP on commercial boards

- ► **Extensible** for Large Detectors + redundancy

- ► **Flexible** → FPGA based : various acquisition modes (triggered, ILC-like)

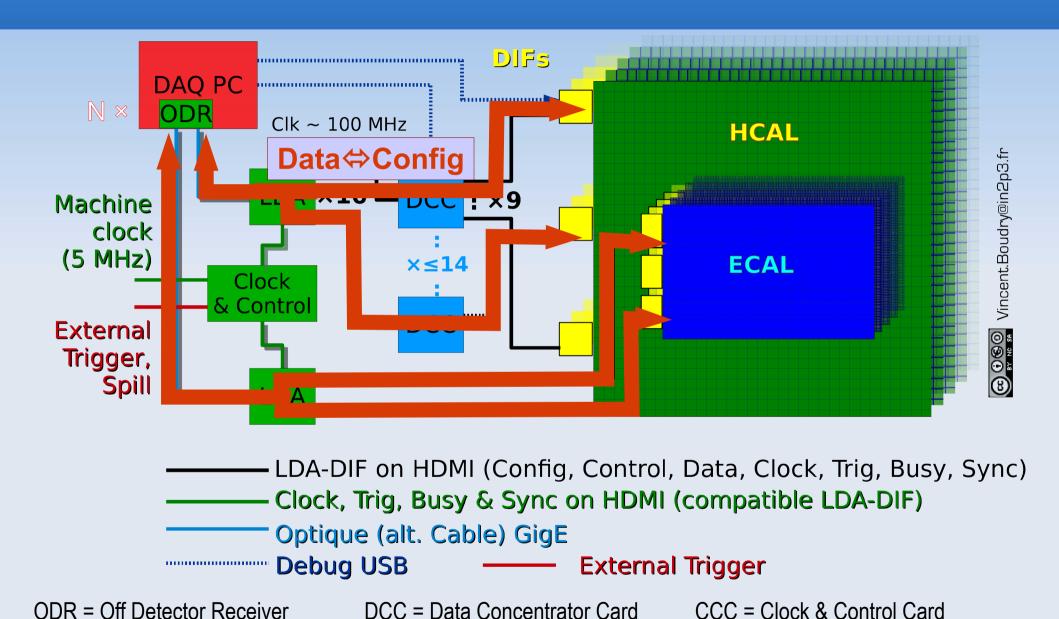

- Provide the digital readout of CALICE embedded front end (\*ROC chips) [1st gen was analogue]

- ► All calorimeters seen through CALICE **standard** Detector **InterFace** board (**DIF**)

- ◆ **Sends** configuration; fast commands; clocks; Triggers

- Receives Data; Busy

- ▶ 1 or 2 **Concentrator** cards level

- ▶ **Distribution & collection** of the fast signal & sequencing

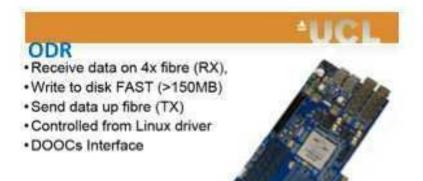

- Advanced Off-Detector Receiver (FPGA based event builder)

- ► All signals on 1 cables; add-hoc secure communication protocol

- "low speed" 8b/10b coding

- 3 CALICE prototypes en route:

- SDHCAL: ~400.000 ch; Digital (2b/ch → 2.5 with BC information & fmt)

- ECAL: ~ 22.000 ch; Energy (12b → 32.2)

- ► AHCAL:  $\sim$  52.000 ch: Energy & time (2×12 b  $\rightarrow$  32.3)

# **Test beam Acquisition modes**

### Single Event + Ext. Trig

- External trigger (from hodoscope or calibration system) = HOLD

- Stop Acq, Hold analog data + sampling, Start Acq

- Noise & Beam condition safe (only 1 evt per trigger)

#### Single Event + auto-Trig

#### NOW USED IN DHCAL TB

- **External trigger** (hodoscope) → DIF

- ◆ Stop Acq, ReadOut (last evt ~ triggered one), Start Acq

- Data sync (for Event building)

- On synchronized BC ID → need for a SYNC @ MClk (100- 400 ns)

- On trigger timestamp

- ◆ BUT: for the AHCAL/Spiroc: the TDC signal needs a SYNC of the clocks ±1ns

- ► Rems: RAMfull from 1 ASIC → Reset of all detector

#### **ILC like**

- StartAcq on Start-of-Spill signal (-δt)

- ► StopAcq & Readout on End-Of-Spill or RAMfull or a Given # Beam Trigger

# **Three TB Running modes:**

### Physics

- as fast as possible IN SPILL,

- ▶ poissonian stat → As low as possible PILE-UP (or not!)

- Data with "low occupancy" (particle type & E dependant)

#### Demonstrator

- as close as possible from final ILC conditions

- power pulsing, auto-trig

- beam conditions close to ILC ? (Duty cycle, occupancy)

#### Calibration / noise

- ► *a priori*: off spill, fixed rate

- all cells ("maximum occupancy")

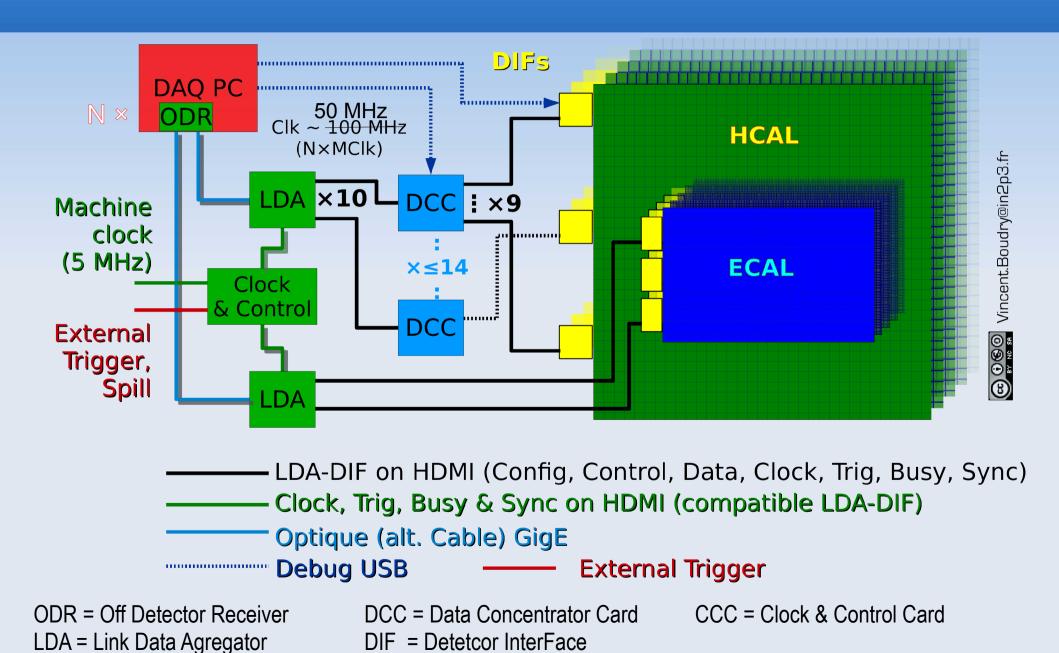

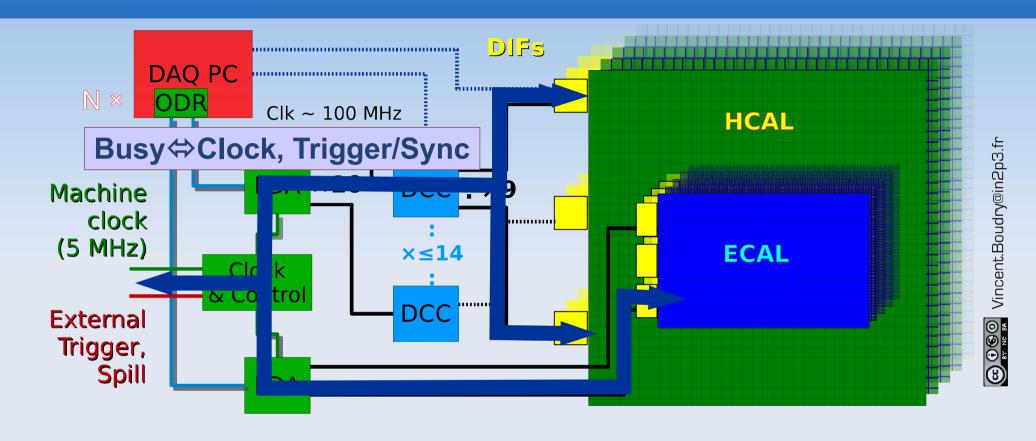

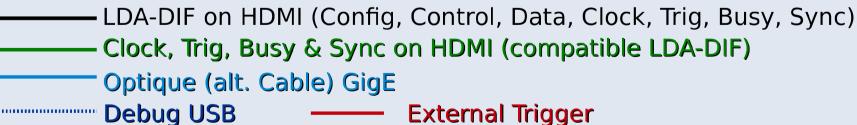

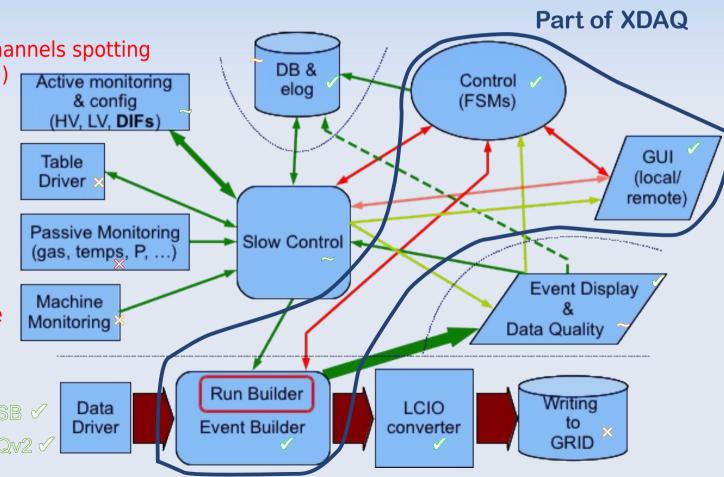

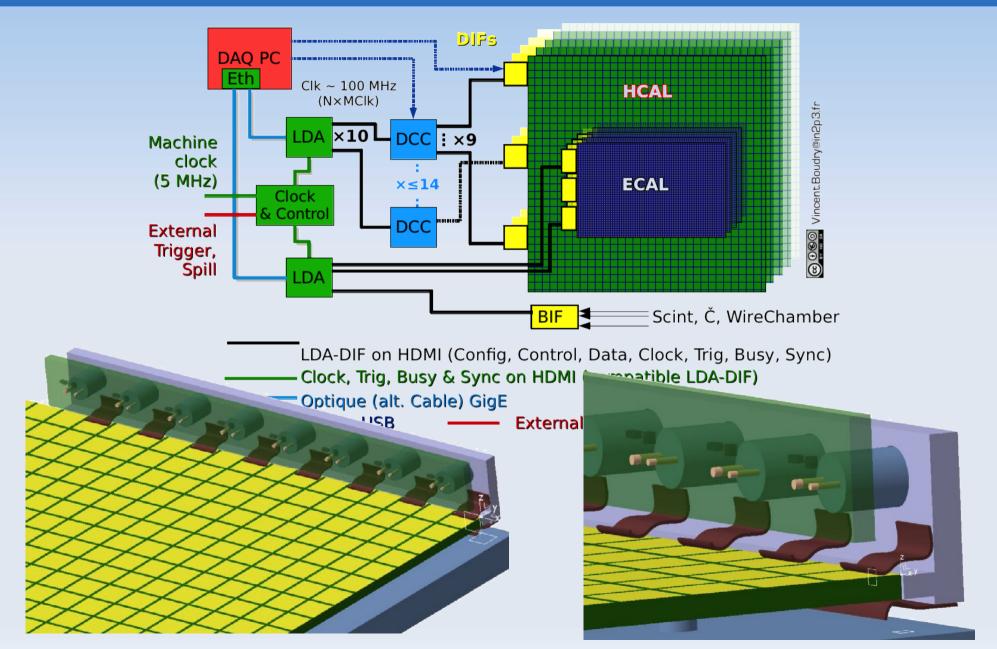

# **CALICE DAQ2 scheme**

# **CALICE DAQ2 scheme**

LDA = Link Data Agregator DIF = Detetcor InterFace

# **CALICE DAQ2 scheme**

ODR = Off Detector Receiver LDA = Link Data Agregator

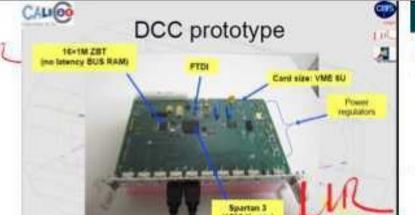

DCC = Data Concentrator Card

CCC = Clock & Control Card

DIF = Detetcor InterFace

# **Detector interfaces**

AHCAL (DESY)

DHCAL (LAPP)

| Grenade, 29/09/2011

12/31

MANCHESTER | Non-House

#### LDA

- . The LDA (from Enterpoint) consists of :

- Mulldonoch2 baseboard:

- add-on HDMI board to connect to 10 DIFs

- an add-on ethernet board to connect to an ODR.

- · Firmware development :

- DIF <=> LDA link running:

- new code soon to be posted to svn;

- same format as ODR in svn repository.

DCC and LDA are essentially similar to an ethernet switch but using a low level protocol

They both fan-out/in fast isochronous signals on a dedicated path and commands on the 8b/10b serial link

LDA has a fast link: Gb ethernet to the upper level = ODR, and can connect to 10 DIFs or DCC with the 8b/10b serial link

DCC can connect to 1 LDA and 9 DIFs using the 8b/10b serial link, data from DIF are buffered and sent to the LDA

- Overall status unchanged for a while.

- Fans out clocks, fast commands and control signals.

UNINERSITY OF CAMBRIDGE

- . Fans in busy.

- Full complement of 10 boards with power. supplies tested.

- . One in LLR and one in LAPP.

- CCC link to LDA still needs to be done:

- Board designed and firmware developed for

- Soon to produce enough boards for all LDAs.

### Documentation / repository

· All components should have extensive documentation on twiki : it is being updated and as components are basically done, can soon be finalised.

MANCHESER

- Twiki main :

- https://twiki.oern.ch/twiki/bin/view/CALICE/CALICEDAQ

- Also list of hardware availability /status started. https://twiki.cern.ch/twiki/bin/view/CALICE/HardwareList

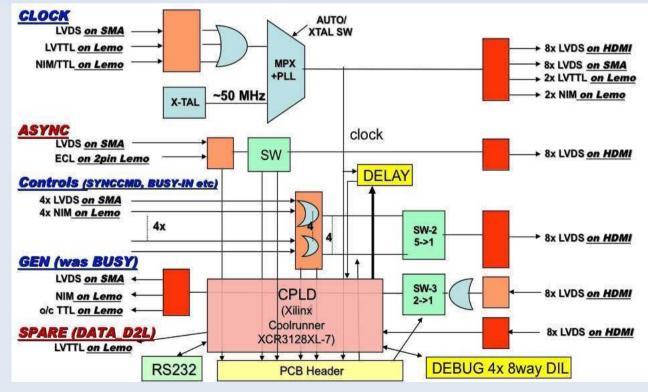

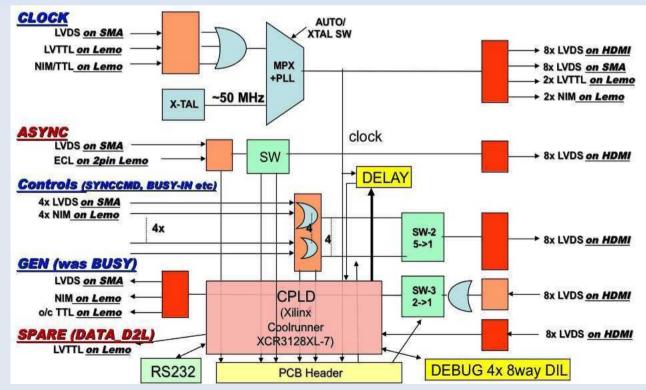

### **Clock and Control Card**

- Developed at UCL (M. Warren, M. Postranecky)

- Distributes on 8 channels (HDMI, SMAs, NIM, ...) via dedicated circuitry for low jitter

- ▶ Int | ext clock

- Fast Signal (Trigger | Sync )

- Sums-up BUSY

- Performs Trigger logics

- ► CPLD

- Performs sequencing

- Reset of detector on ramfull

- Readout order on Trigger

- At limit

- new HW required

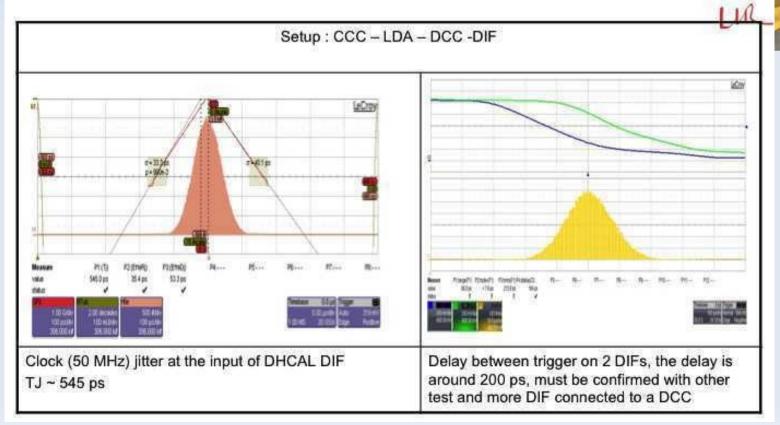

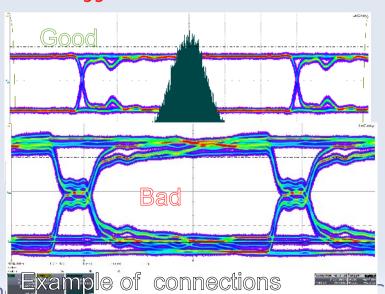

# Clock & Trigger jitter

- Trigger & busy handling (G. Vouters)

- ► Trig (NIM) → CCC → LDA → DCC → DIF BUSY ← CCC ← LDA ← DCC ←

- Trigger Jitter between DIFs (FG)

### Jitter measurement

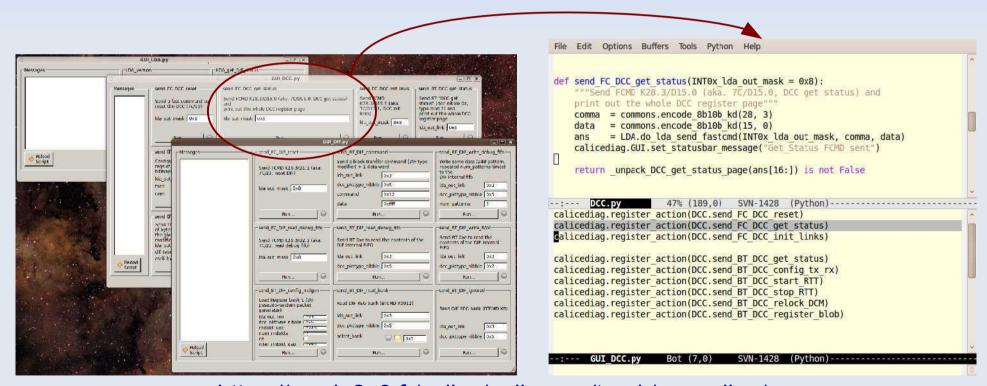

# **Python Test toolkit**

- Interactive hardware test software (GUI)

- Each HW test easily scriptable: simple user-friendly python API: each function defined ← 1 graphical pane with "Run" button

- Available to anyone working with USB/RS/Ethernet devices

- C libraries implementing the complete DIF Task force protocole → API

https://svn.in2p3.fr/calice/online-sw/trunk/pyserdiag/

# Reliability tests

#### **Stress tests using pseudo-random generator**

- $9 \times DIF \rightarrow 1 \times DCC \rightarrow 1 \times LDA \rightarrow PC$

- ▶ 9 DIFs (ECAL & SDHCAL) generate pseudo random data

- Results

- ▶ Direction DIF → LDA ✓

- Maximum DCC → LDA link occupancy (40Mbps) ✓

- Many TB of data transferred no error (on table)

### **End-to-end test: FIFO write/read**

- PC ↔ 1×LDA ↔ 1×DCC ↔ 1×DIF

- ► Tests both fast-commands and block transfer "read" requests

- PC ↔ LDA Ethernet OK

### **ROC** config loading & checking ✓

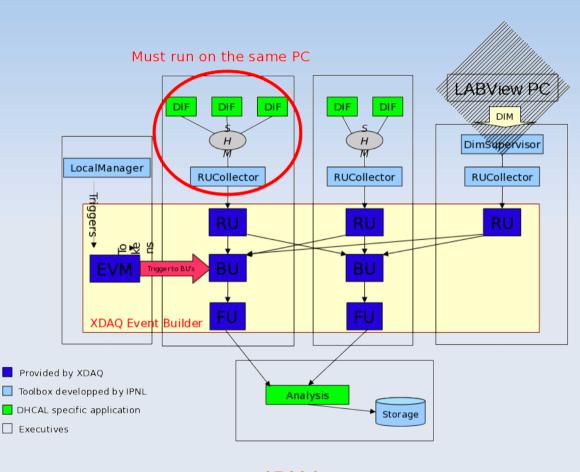

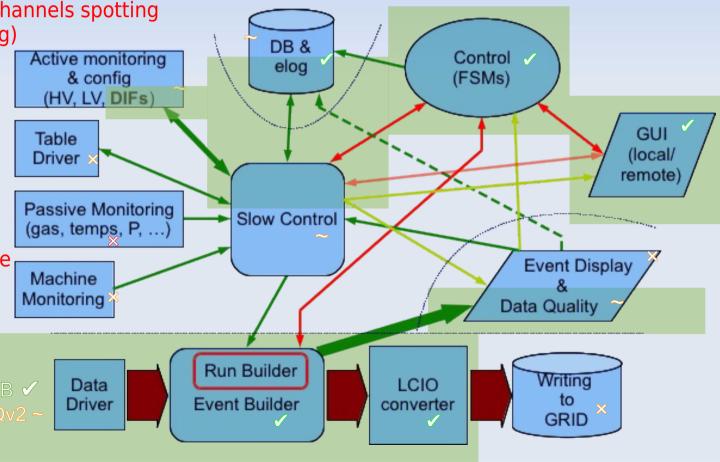

# Software: XDAQ framework

- dev<sup>ts</sup> started @IPNL for electronics test using XDAQ in 2008

- Ran for ≥ 1 year in TB, Cosmics & Electronics test

- USB readout

- Interface to old LabView program

- Recent development

- Integration of DAQ2 readout chain

- interface to a configuration DB

- Writing of LCIO data in RAW format

- versatile online analysis framework (root histos)

- → Marlin Based

- For current TB: deployment on 4 PC tested;

Performances to be improved

**IPN Lyon**

### **SW** status

- XDAQ + C library to DAQ2

- All critical elements are ready

- Configuration DB (being worked on)

- DAQ2 interface

Semi-automatic noisy channels spotting & correcting (monitoring)

- Clean Slow control

- interface to CondDB;

- event display

- Missing ancillaries

- interface to the GRID

- interface to the machine (⊃ in AIDA WP8.6.2)

# First large scale test

- Last 2 weeks at PS

- SDHCAL with 31 chambers ( $\sim$ 2/3 of full det).

- 90 DIFs, 2 LDAs, 13 DCC, 1 CCC, 4 PCs

- ~4400 ASIC / 285k channels individually configured

- Solved grounding problems, reset procedure, mis-functionnal elements, FW glitches, Data corruption

Readout ~100k triggers in test beam mode

(10 GB of data)

- ≥1 events per trigger

- trigger on scintillators

LICE Deam tests ("LCVV5 1")

| Entries<br>Nean x<br>Nean y<br>PMS x          |

|-----------------------------------------------|

|                                               |

|                                               |

|                                               |

|                                               |

|                                               |

|                                               |

| Hije<br>But les<br>Neon x                     |

| Ent les<br>Neon x<br>Neon y<br>PMS x<br>DMS y |

|                                               |

|                                               |

|                                               |

| lda | dec | cumulative data size | nb of shmwr | Failed | Corrupted |

|-----|-----|----------------------|-------------|--------|-----------|

| 1   | 1   | 330200               | 357         | 0      | 0         |

| 1   | 2   | 256638               | 357         | 0      | 0         |

| 1   | 3   | 1891131              | 355         | 0      | 1         |

| 1   | 4   | 720476               | 357         | 0      | 0         |

| 1   | 5   | 662954               | 357         | 0      | 0         |

| 1   | 6   | 944784               | 357         | 0      | 0         |

| 1   | 7   | 691332               | 357         | 0      | 0         |

| 1   | 8   | 719920               | 355         | 0      | 1         |

| 1   | 9   | 1289548              | 355         | 0      | 1         |

| 2   | 1   | 0                    | 0           | 0      | 0         |

| 2   | 2   | 0                    | 0           | 0      | 0         |

| 2   | 3   | 0                    | 0           | 0      | 0         |

| 2   | 4   | 1165448              | 357         | 0      | 0         |

| 2   | 5   | 802156               | 355         | 0      | 1         |

| 2   | 6   | 838746               | 357         | 0      | 0         |

| 2   | 7   | 1927652              | 357         | 0      | 0         |

| 2   | 8   | 2155632              | 357         | 0      | 0         |

| 2   | 9   | 1690838              | 355         | 0      | 1         |

| 3   | 1   | 1287528              | 355         | 0      | i .       |

Grenade, 29/09/2011

20/31

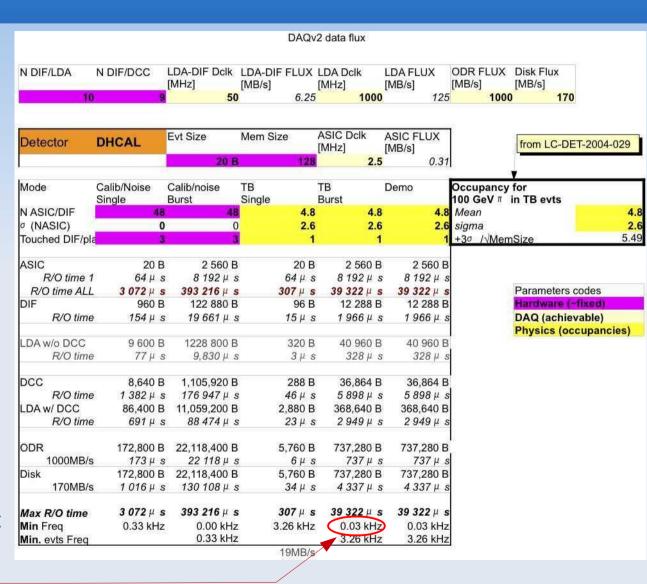

### **Performances**

Rather low demands in term of bandwidth (but >> @ ILC for same vol.)

► SDHCAL : ~ 20MB/s in Spill

► ECAL: ~100MB/s

► AHCAL: ~ 300 MB/s

- Data limited by ASICs readout

- Modes:

- test beam single event

- Test beam burst (≈ ILClike mode)

- Some code (System C) exists for simulation of full chain, being tested

- Successful full scale test done last week at PS with the SDHCAL

- ▶ 5 Hz of data taking

- Noisy detector (heat)

### **Beam InterFace card**

### Beam InterFace card

#### **Basis**:

- CALICE chips use auto-trigger

- Readout can be triggered by single event using external trigger (e.g. beam hodoscope)

- → "Single event" mode

History of Chip is usable (e.g. in case of selective ext. trigger)

- Readout triggered by environmental internal or extern trigger

- Chip full

- ILC-like mode (end-of-spill)

- Require some device to readout the beam line parameters

- Scintillators; Cherenkov PM (coding of CEDAR bits)

- ► Time of event (⊃ rec for wire chambers) within a 5 MHZ clock period

#### **Implementation**

- 2 solutions

- ► Add-hoc card for interfaces with a CALICE ROC (SPIROC ?) + 1 DIF

- Small adaption (buffers) card on a DIF + "simulation" of a digital ROC in the FPGA

- Part of the coding can be "tricky"

- Both offer full compatibility with CALICE DIF for the DAQv2.

- To be implemented for 2<sup>nd</sup> version of CALICE beam test

- One of the task of AIDA (WP8.6.2)

- ► For "standalone" CALICE tests

- ► Functionnalities ⊃ in JRA1 TLU

Use of sub-ns TDC for CERN wire chambers until then?

# **Summary & outlook**

- Last months dedicated on bench studies & FW improvement

- CALICE DAQ2 has reach the **deployment phase** → **ready for large TB**

- ► TB of SDHCAL with 400,000 channel next week with RPC (HardROC) & μMegas (MicroROC)

- ► ECAL & AHCAL new electronics test bench

- HW ~ stabilized

- ► Improvement of existing cards (LDA, CCC) foreseen

- Beam InterFace card too be designed

- FW & SW in early functionnal version

- Clean-up and part-rewriting needed

- Improvement of diagnosis tools needed

- Integration with environment (beam) to be done

- AIDA (co-running of CALICE & EUDAQ → common DAQ)

- Specifications to be decided in next months

Big effort for CALICE!!

~15++ individuals from:

- UK: CAM, MAN, UCL, RHUL

- FR: LLR, LAPP, IPNL

- DF: DFSY

# **Back-up**

### **Clock and Control Card**

- Developed at UCL (M. Warren, M. Postranecky)

- Distributes on 8 channels (HDMI, SMAs, NIM, ...) via dedicated circuitry for low jitter

- ▶ Int | ext clock

- Fast Signal (Trigger | Sync )

- Sums-up BUSY

- Performs Trigger logics

- ▶ CPLD

- Was used as DIF-Master (dev<sup>t</sup> of LAPP)

- Aka also sending hard-coded commands to DIF directly

- Standalone tests with USB readout

### SW status

- Missing critical elements

- Configuration DB (being worked on)

- ► DAQ2 interface ↔ XDAQ being worked on

- Missing ancillaries

- Semi-automatic noisy channels spotting & correcting (monitoring)

- Clean Slow control

- interface to CondDB;

- event display : DRUID on LCIO file

- interface to the GRID

- ▶ interface to the machine (⊃ in AIDA WP8.6.2) Code exists in DAQv1

**Implemented**

# CALICE DAQ

### Back up

# **HW** availability

| Card            | #Avail | #Tested | #OK | Remark  All basic HW avail.                                                          |

|-----------------|--------|---------|-----|--------------------------------------------------------------------------------------|

| PC              | 6      | 6       | 6   | OS needs upgrade                                                                     |

| ODR             | 10     | 4       | 4   | (commercial board: no expected default)                                              |

| LDA             | 25     | 22      | 17  |                                                                                      |

| HDMI Mezzanines | 30     | 24      | 13  | 4 have faulty connectors and are being repaired. Not all cards have 10 conn. working |

| GEth mezzanines | 25+5   | 25      | 20  | 2 can easily be recovered                                                            |

| CCC Adapter     | 25     | 17      | 16  | Limits # of installations                                                            |

| CCC             | 10     | 10      | 10  | term adaptation maybe be needed                                                      |

| DCC             | 2+20   | 22      | 21  | 1 faulty channel on 1 card;<br>1 burned to be repaired                               |

| ECAL DIF        | 29     | 29      | 29  | equipement for 11 additional ones avail.                                             |

| SDHCAL DIF      | 190    | 190     | 183 | 7 being refurbished; mods needed for HR2 (ok for HR2b)                               |

| AHCAL DIF       | 4*     |         |     | *Being produced                                                                      |

Complete list of HW pieces & location available on https://twiki.cern.ch/twiki/bin/view/CALICE/HardwareList Vincent.Boudry@in2p3.fr 2G DAQ for the CALICE beam tests | LCWS'11 | Grenade, 29/09/2011 30/31

### **Cables**

- CERN requires halogen free cables

- "IS23 does apply to above-ground installations and experiments."

- On shelf: only for HiFi freaks (or Pigeons):

- beautiful 100€ apiece 5m-long shielded HDMI cable

- 1 reasonable offer:

- On demand PolyEthylene coating

- $\triangleright$  ~ 25€/cable (5m long, Ø 8.5mm) for 200+ cables.

- pbm: 12 weeks delais

- ► ~ enough funds on ANR to buy for the m³ SDHCAL (150 needed)

- Urgent: 12 weeks delay due to boat shipping from China

- Other demands being surveyed:

- μMegas (~30 ?)

- AHCAL (50) and ECAL (30)

- + 10% spares (enough ?) → 260-275

Check F. Davin presentation