# **DEPFET Prototypes**

LCWS 2011 Granada

Fernando Martínez Vidal Marcel Vos Guillermo Eneas Timón

# **DEPFET** collaboration

#### University of Barcelona

- **Ramon Llull University**

- Bonn University

- Heidelberg University

- Goettingen University

- Karlsruhe University

- IFJ PAN, Krakow

- **MPI Munich** .

- Charles University, Prague

- IGFAE, Santiago de Compostela University

- IFIC, CSIC-UVEG, Valencia

- University of Giessen

Universitat Ramon Llull

Werner Heisenberg-Institut)

GEORG-AUGUST-UNIVERSITÄT GÖTTINGEN

#### UNIVERSITAT DE BARCELONA B

FRSIDADE SANTIAGO

www.depfet.org

27/9/2011 Guillermo Eneas Timón Grau

# Index

- Introduction

- Operation principles & feautres

- Matrix & Prototype

- Beam Test Results

- Trailing frames

- Modificated readout sequence

- Source data analysis

- Clear efficiency

- Results

Conclusions

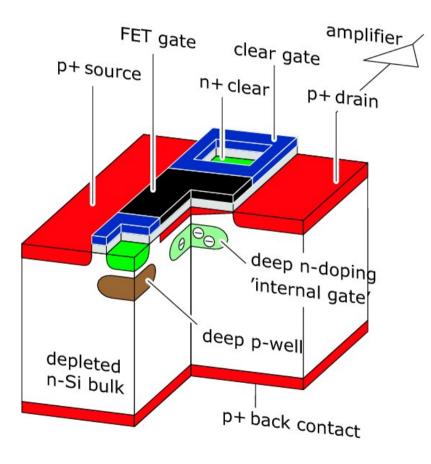

#### Introduction: Operation principles & features

- DEPFET is an active pixel detector:

- Each pixel is a p-channel FET on a completely depleted bulk.

- A deep n-implant creates a potential minimum for electrons under the gate (internal gate).

- Signal electrons accumulate in the internal gate and modulate the transistor current (~300-600pA/e<sup>-</sup>).

- Accumulated charge can be removed by a clear pulse.

- Features:

- Internal amplification.

- Large SNR.

- Thin detector ~ 50µm.

- Good spatial resolution.

- Low power consumption, only read out one row at time. Rolling shutter readout scheme.

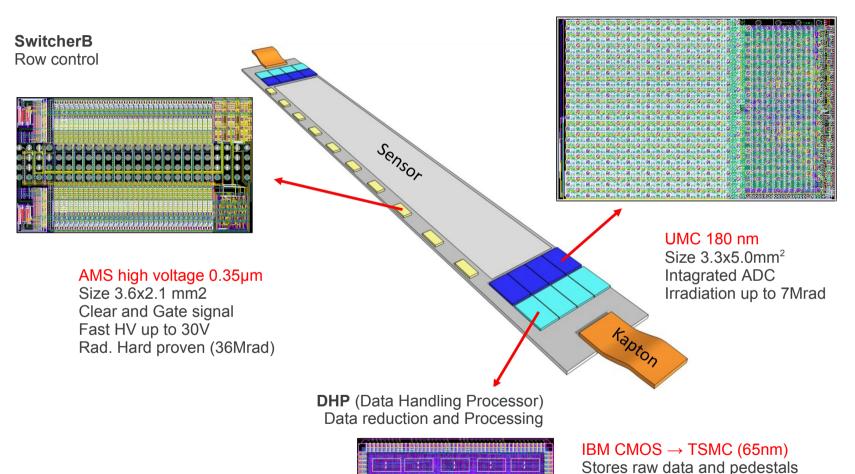

- Readout channels integrated over the detector. Chips laying on lateral balcony.

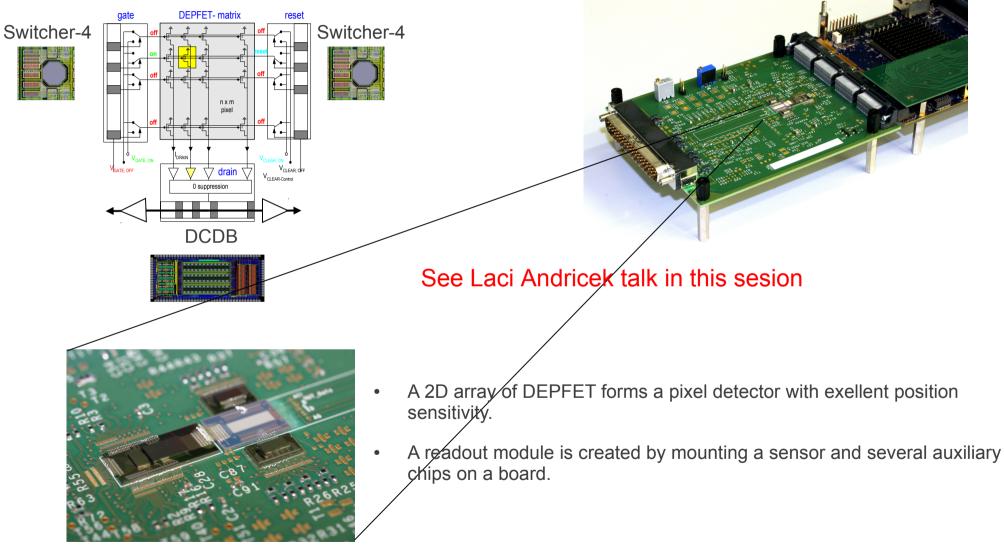

#### Introduction: Matrix & Prototype

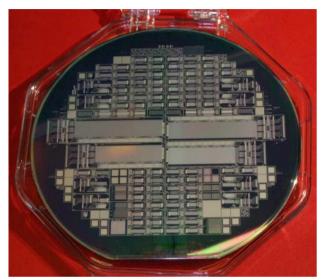

PXD5+DCDB prototype

27/9/2011 Guillermo Eneas Timón Grau

#### **Beam Test**

• Beam Tests with ILC geometry detector have confirmed the DEPFET characteristics.

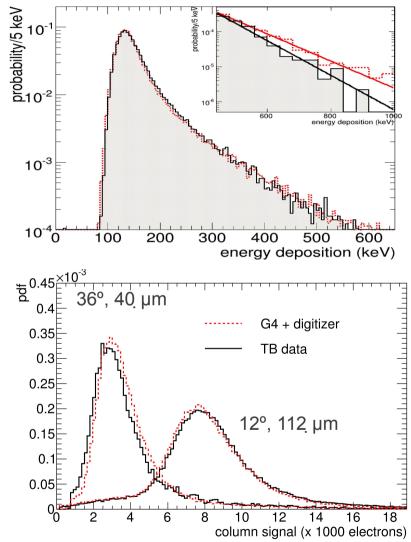

#### **Beam Test results**

- Tests of DEPFET prototypes devices

- Validation of fast DEPFET simulation

- Response to minimum ionizing particle, performed at CERN SPS:

- Use most probable signal to extract  $g_q = \Delta I_D / Q$

- 6 µm gate length→~300pA/e<sup>--</sup>

- 5  $\mu$ m gate length $\rightarrow$ ~650pA/e<sup>--</sup>

- Resolution ~1µm for 20x20 µm<sup>2</sup> pitch and 450 µm thick.

- Using information of one column we can predict the charge distribution for thin sensor.

- New prototypes thinned down to 50µm thickness tested (Beam Test next week in CERN SPS).

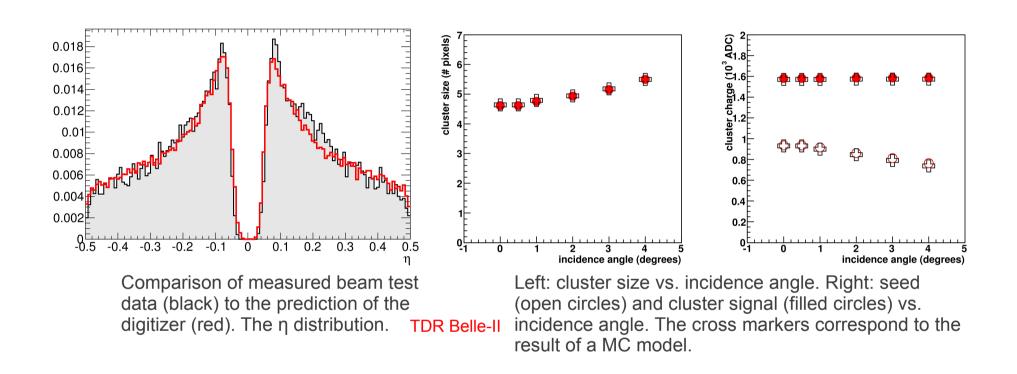

The column signal distribution from TB data (black continuous line) and MC (red dashed line) for incidence angles of 12° and 36° with respect to the perpendicular correspond to a sensor thickness of 112  $\mu$ m and 40  $\mu$ m,

respectively

**TDR Belle-II**

#### **Beam Test Results**

Charge sharing between DEPFET pixels is understood.

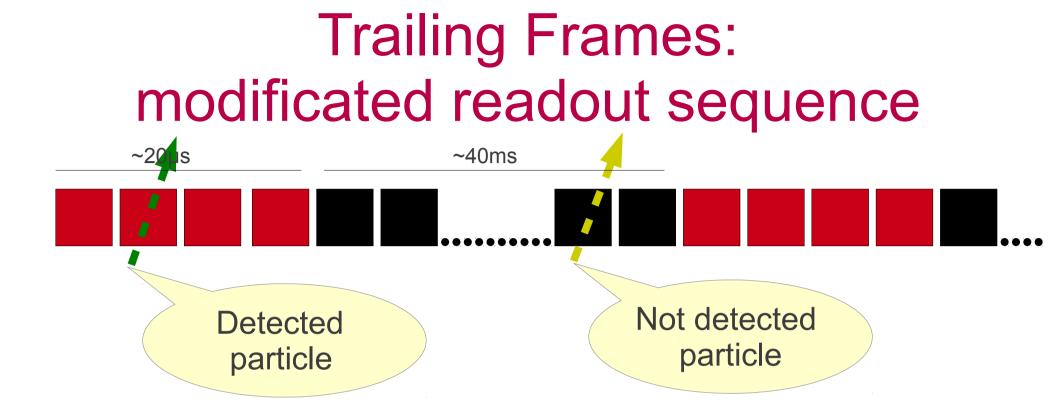

- Trailing Frames are a modificated readout sequence in which the information from four consecutive readout frames of the matrix can be saved (implemented in the DAQ by Sergey Furletov and his team in the test beam of 2010).

- This readout mode allows to measure the efficiency with which signal is removed under different circumstances.

- The matrix is doing its reading sequence continuously.

- Red squares represent the four consecutive frames where we see the matrix information.

- Black squares represent the frames that we don't see.

#### Trailing Frames: Source data analysis

- Measures taken with <sup>109</sup>Cd source at MPI by Christian Koffmane.

- We define  $V_{CL}^{eff} = V_{CL}^{Hi} V_{CL}^{Lo}$ , such quantity is a crucial voltage for the clear performance.

- Clear voltage scan: all voltages are referred to source.

| Date      | Run  | CCG(V) | ClearHi(V) | ClearLo(V) | GateLo(V) |

|-----------|------|--------|------------|------------|-----------|

| 15/2/2011 | 2072 | -1.5   | 18         | 2.5        | -3.65     |

| 28/4/2011 | 3007 | -1.5   | 17         | 2.5        | -3.65     |

| 28/4/2011 | 3008 | -1.5   | 15         | 2.5        | -3.65     |

| 28/4/2011 | 3009 | -1.5   | 13         | 2.5        | -3.65     |

| 28/4/2011 | 3011 | -1.5   | 22.5       | 2.5        | -3.65     |

| 28/4/2011 | 3012 | -1.5   | 20.5       | 2.5        | -3.65     |

| 28/4/2011 | 3013 | -1.5   | 24.5       | 2.5        | -3.65     |

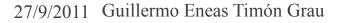

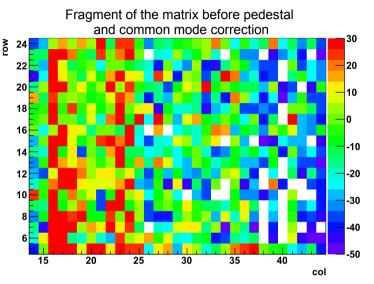

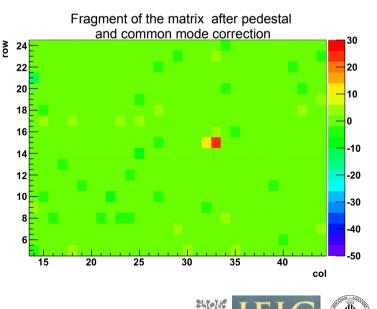

#### Trailing Frames: examples

ADC counts after common mode and pedestal correction for four consecutive frames.

A faint "shadow" of the signal is visible after clear pulse.

- For low clear voltage, the signal remains large in multiple frames.

- # Clusters increases strongly when  $V_{CL}^{eff}$  diminishes. As the clear is inefficient we see the same cluster more than once.

- Raising the clear voltage, a complete clear is achieved.

# Run 3013 $V_{CL}^{eff} = 22V$

#### Clear Performance: Clear Efficiency

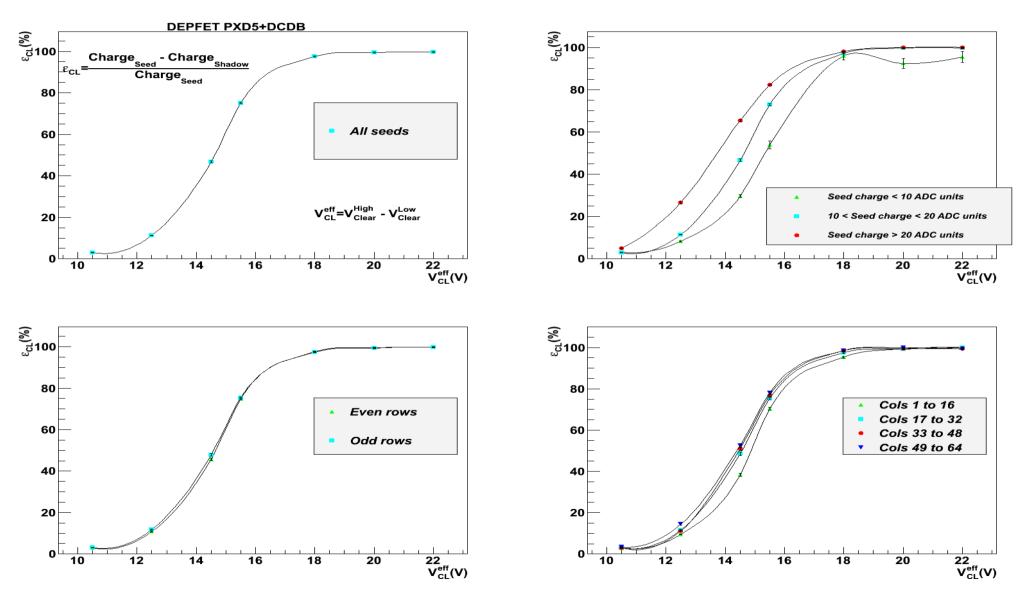

- We measure the clear efficiency by comparing the charge on the seed pixel of the cluster,  $Q_0^{seed}$ , and the charge in the same pixel after applying the clear pulse,  $Q_f^{seed}$ .

- To quantify the clear performance in a single figure of merit the clear efficiency,  $\varepsilon_{Ch}$  has been defined as:

• Measurements of this quantity under different circumstances and their corresponding analysis are presented below.

#### Clear Performance: results

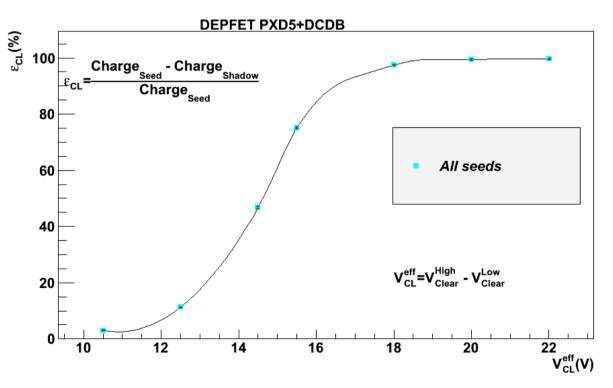

• The average clear efficiency as function of effective clear voltage increases strongly between 12 and 18 Volts. A *plateau* of 100% is reached at approximately 20V.

Clear efficiency as function of the effective clear voltage

#### Clear Performance: results

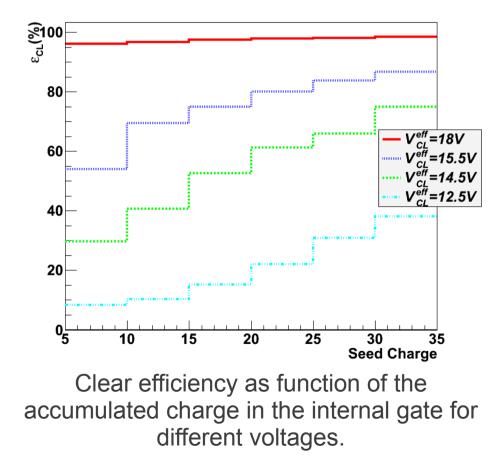

• Clear efficiency depends on the amount of charge accumulated in the internal gate. For intermediate voltages this dependence is more pronunciated. Qualitatively this can be understood as due to the repulsion of charge carriers.

#### Clear Performance: results

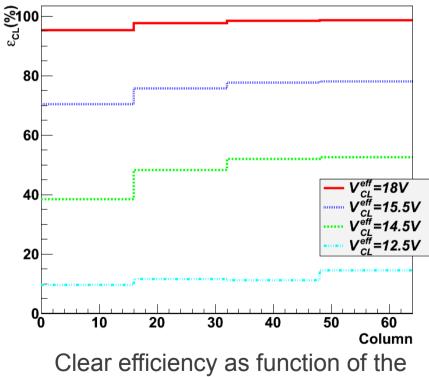

• There is a small, but significant dependence of the clear efficiency with the column number. The clear pulse is most effective for columns close to the switcher generating the clear pulse. As the clear pulse propagates over the line which carries from one side of the matrix to the other the pulse height is degraded (that explanation has to be confirmed by detailed simulations).

distance to the switcher generating the clear pulse for different voltages.

#### Conclusions

- DEPFET technology allows to build very thin detectors with high spatial resolution.

- DEPFET (ILC design) performance has been measured in Beam Tests. Program to continue in October 2011 with thin sensor devices.

- We have developed a new method to study the clear efficiency of DEPFET readout prototypes.

- We have measured a dependence on the effective clear voltage, the amount of charge accumulated in the internal gate and the distance to the clear switcher for the clear performance.

# Thank you!

# **Back Up Slides**

27/9/2011 Guillermo Eneas Timón Grau

#### **Clear Efficiency**

27/9/2011 Guillermo Eneas Timón Grau

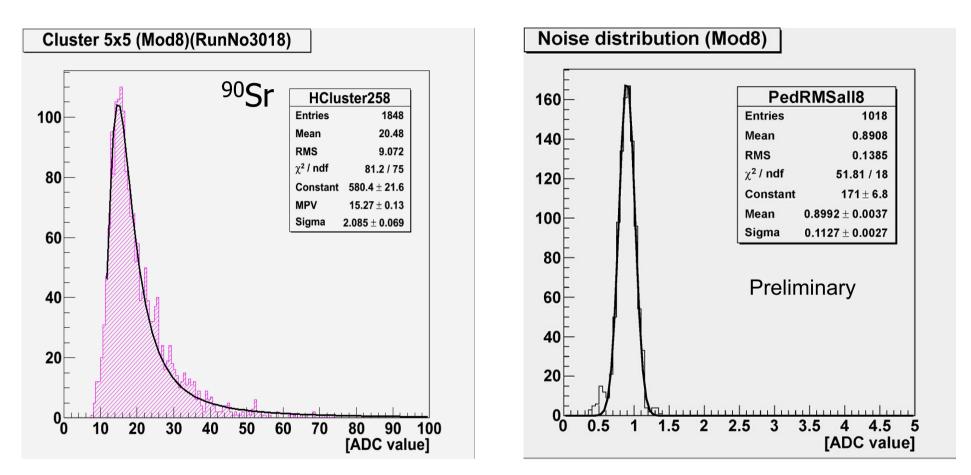

## DEPFET: Extracting data from DEPFET

- Drain current when no charge is accumulated in the internal gate: pedestal,  $i_{red}$ .

- Standard deviation of  $i_{red}$ : noise,  $\sigma$ .

- A correction is applied that subtracts noise common for each row,  $i_{com}$ .

- The signal,  $i_{sig}$ , measured is then:  $i_{sig} = i_{drain} i_{ped} i_{com}$

- If  $i_{sig} > 10 \cdot \sigma$  we have a physical sign (only required for cluster seed).

- A neighbouring pixel is added to the cluster if  $i_{sig} > 2.6 \cdot \sigma$

- The SNR of the total cluster has to be > 12.

ADC counts ploted in a 2D Histogram

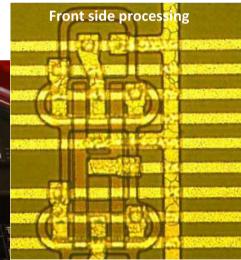

#### VXD ladder & Auxiliary Chips

**DCDB** (Drain Current Digitizer for Bellell) Analog frontend and ADC

Common mode and pedestal correction

**TOVALENCIA**

Data reduction (zero suppresion)

Timing signal generation

Switcher, DCD: Heidelberg U. DHP: Bonn U., Barcelona U.

27/9/2011 Guillermo Eneas Timón Grau

## PXD6 prototypes: Thin wafers

- 8 wafers with thin sensors (50µm):

- Small matrices to test different pixel size (50 to 200µm)

- Design variations: short gate lengths, clear structures

- Half ladders for prototyping (final size)

- Technology variations on the wafer level

- 90 steps fabrication process

- 9 Implantations

- 19 Lithographies

- 2 Poly-layers

- 2 Alu-layers

- Back side processing

19 months processing time (16 after SOI preprocessing)

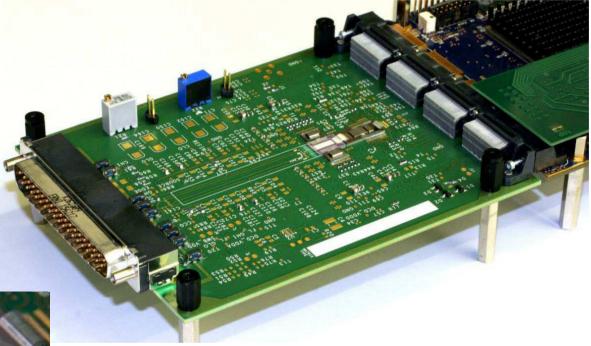

## PXD6 prototypes: Test platform

#### **Belle-II design**

- Sensor 32x64 pixels

- 50x75x50 μm<sup>3</sup>

- SwitcherB and DCDB at full speed

# Prototypes with thin DEPFET sensors produced!

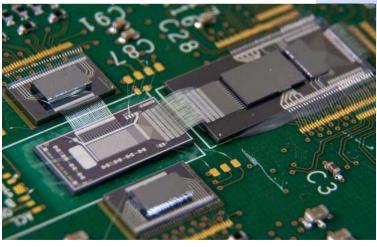

#### PXD6 prototypes: Fast readout

320MHz DCDB frequency→100ns read-out time, S/N=17 (not optimal voltages)

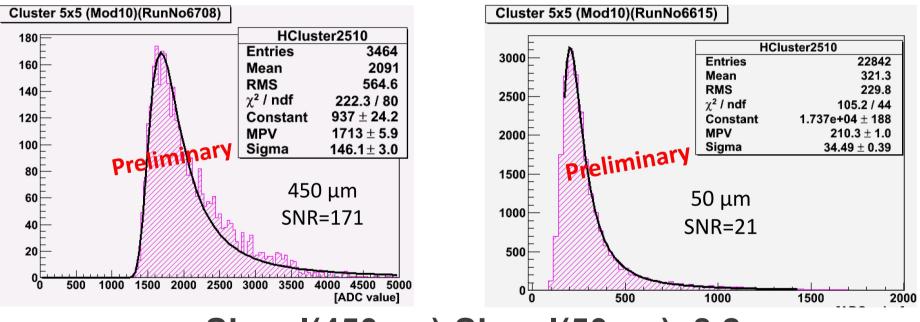

#### PXD6 prototypes: Thin sensors

#### Thick and Thin sensors:

Belle-II design

Gate length = 6 µm

CURO readout

#### Signal(450µm):Signal(50µm)=8.2

#### As expected!