SUNGKYUNKWAN UNIVERSITY Information & Communication Engineering

## Status and plans for a highly granular SiW Ecal EUDET Module extension

Roman Pöschl LAL Orsay

### French Korean Electronics workshop at SKKU May 2011

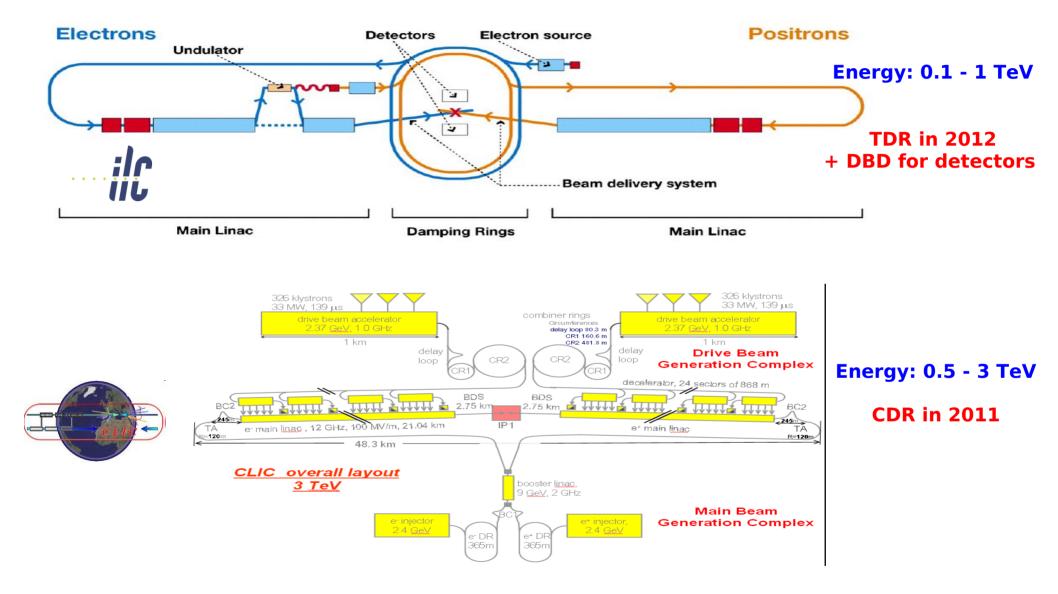

#### (Future) Linear electron-positron accelerators

#### Linear collider is integral part of European Strategy beyond 2012

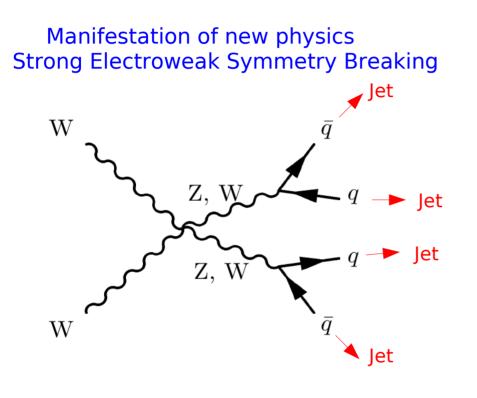

#### Boson Boson Scattering

What if no Higgs?

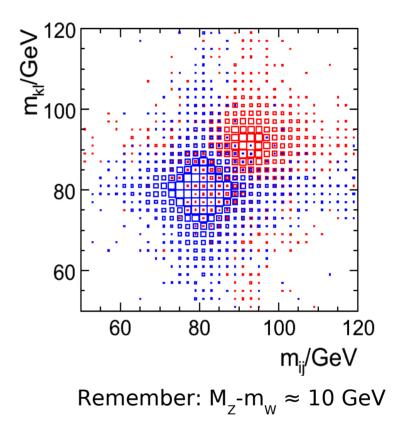

W, Z separation in the ILD Concept

- Need excellent jet energy resolution to separate W and Z bosons in their hadronic decays  $3\%/E_{iet}$ -4%/ $E_{iet}$

- Basic mean: Highly granular Calorimeters

#### SiW Ecal - Basics

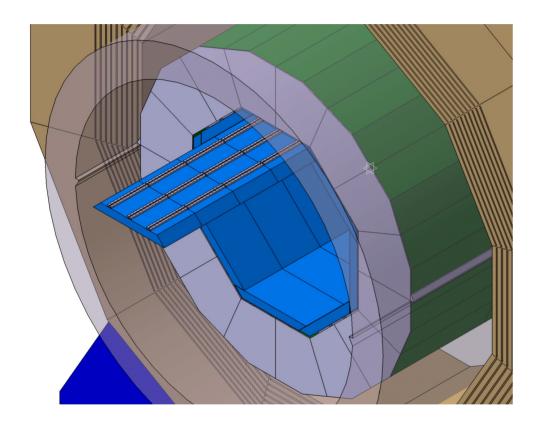

#### The SiW Ecal in the ILD Detector

#### **Basic Requirements**

- Extreme high granularity

- Compact and hermetic

#### **Basic Choices**

- Tungsten as absorber material

- $X_0 = 3.5$  mm,  $R_M = 9$  mm,  $\lambda_1 = 96$  mm

- Narrow showers

- Assures compact design

- Silicon as active material

- Support compact design

- Allows for pixelisation

- Large signal/noise ratio

#### SiW Ecal designed as Particle Flow Calorimeter

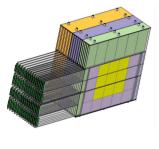

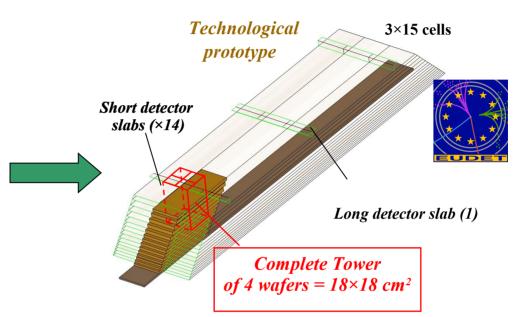

### **Technological Prototype**

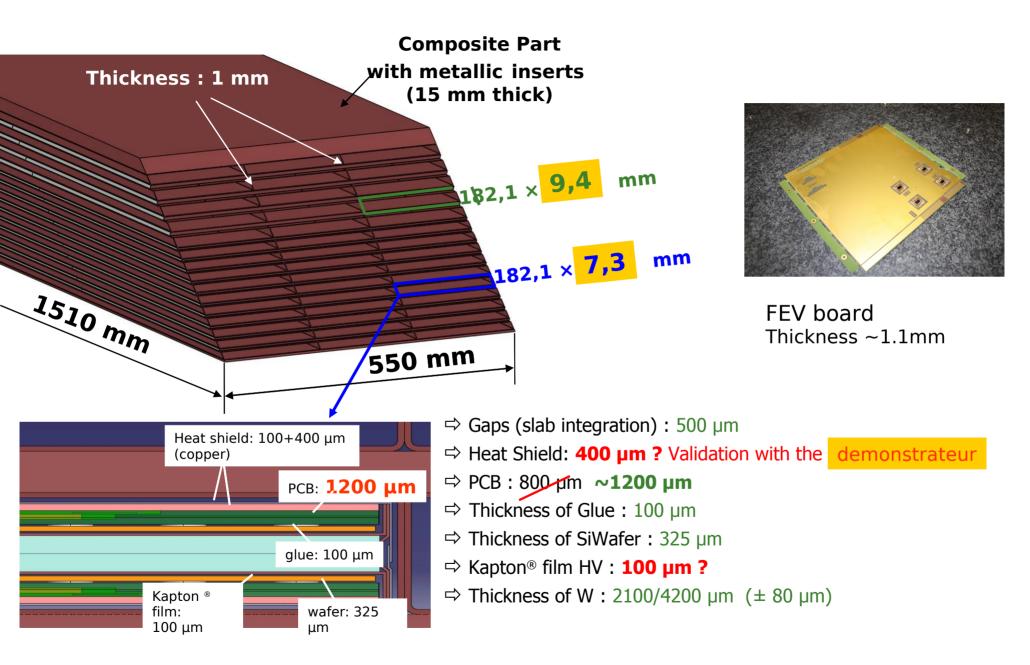

#### Technical solutions for the/a final detector

- Realistic dimensions

- Integrated Front End Electronics

- Small power consumption Power pulsed electronics

- Construction 2010 2012, Test beams ~2012

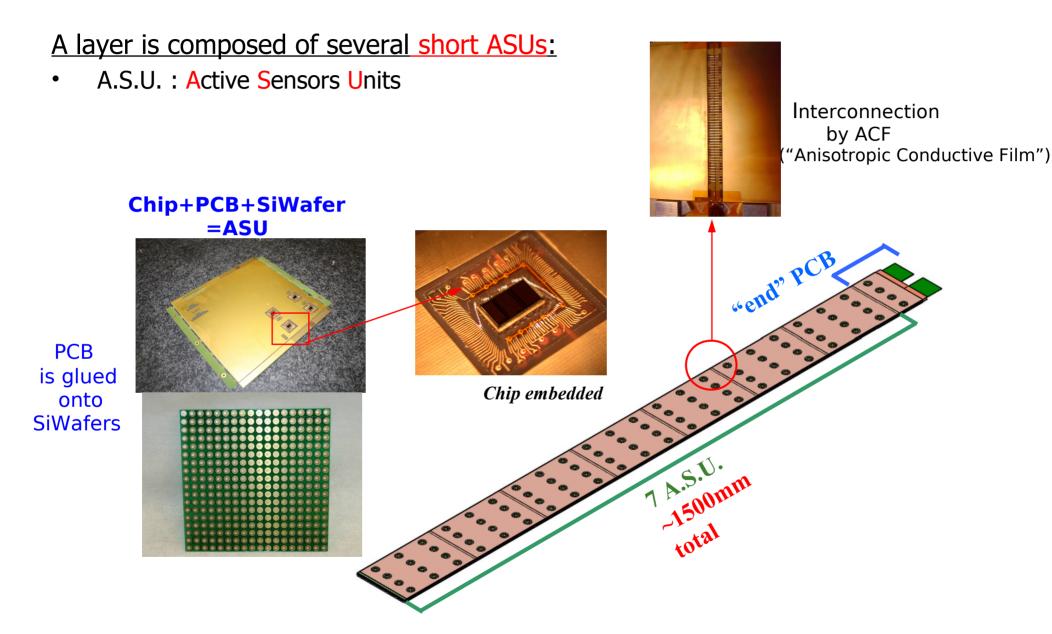

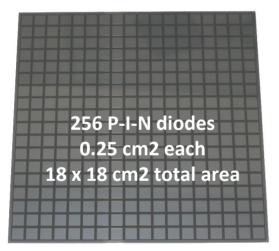

### Ecal detector layer - principle

#### EUDET "legacy"

Alveolar strucuture to house layers (self supporting)

| 9cm                                     |

|-----------------------------------------|

| 256 P-I-N diodes                        |

| 0.25 cm2 each<br>18 x 18 cm2 total area |

|                                         |

Front end electronics

Silicon sensors

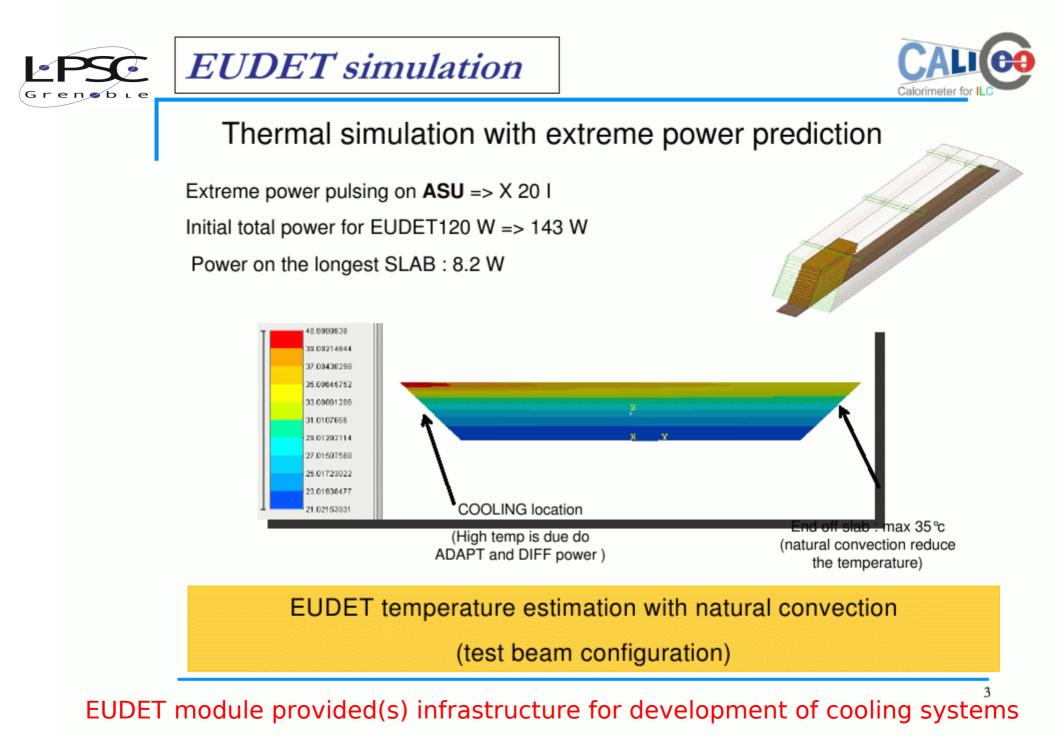

Status of the portable cooling station for EUDET life:

- Chiller and flow meter => ORDERED

- Important step : machining of heat pipe cooling system and water cooling system will begin after the final assembling of the alveolar structure (we need final dimension of the alveolar structure) => November 2010.

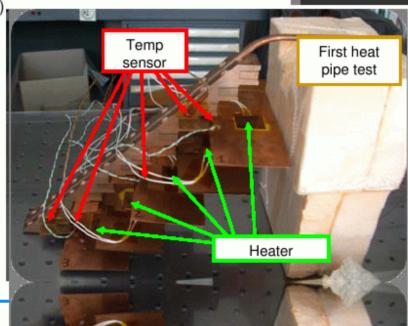

- Spring 2010 First test of heat pipe test (15 W design)

- November 2010 construction of both systems:

Heat pipe

Water cooling system for EUDET (143 W)

### COOLING system for EUDET : march 2011

1<sup>st</sup> version

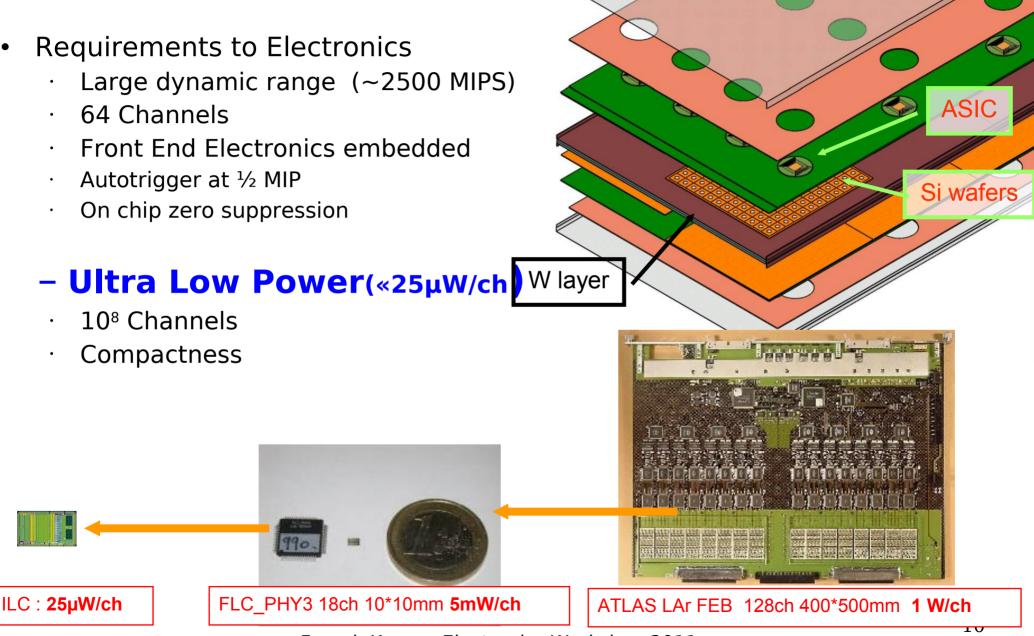

## Front End Electronics

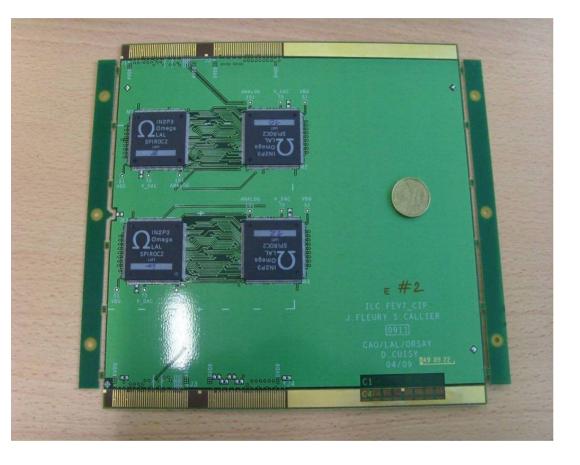

### SPIROC2 and FEV7

- FEE established designed and prototyped within EUDET

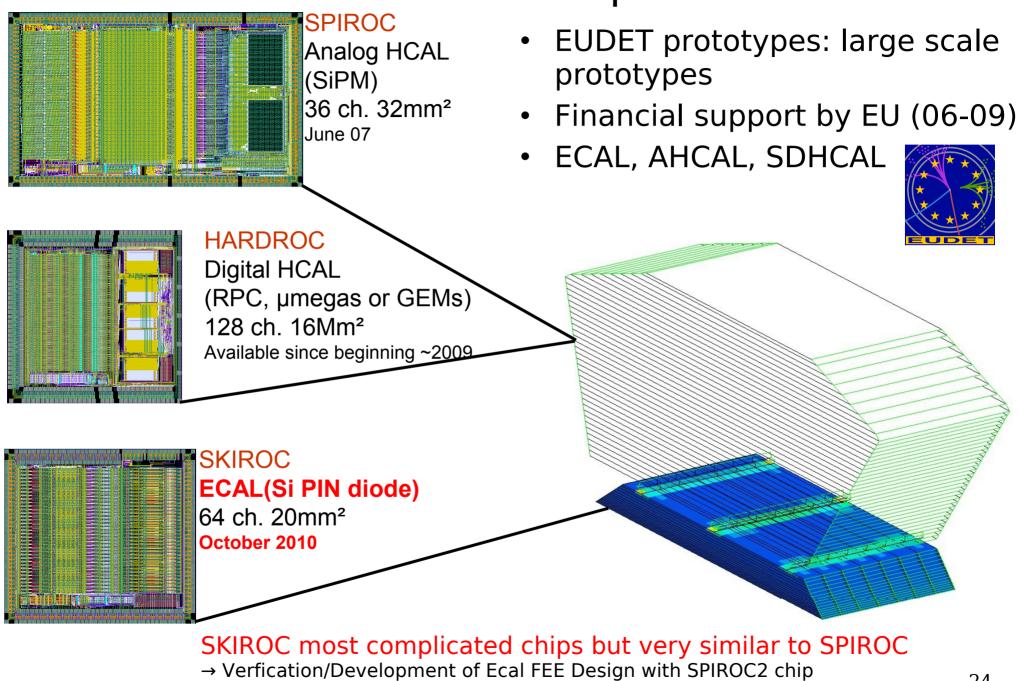

Used SPIROC chip (AHCAL) for first version of Ecal ASU SPIROC: 30 channels 500 MIPS dynamic range Chip for Ecal is SKROC

SKIROC: 64 Channels 2500 MIPS dynamic range At hand since autumn 2010

- Chip in package to validate principle of FEE design

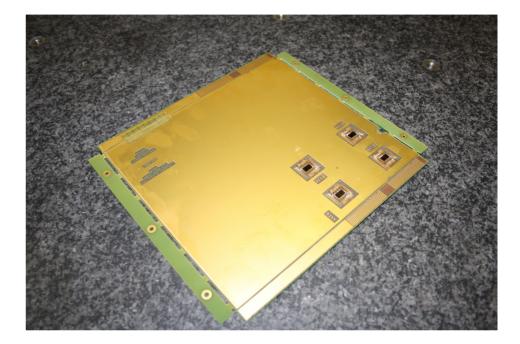

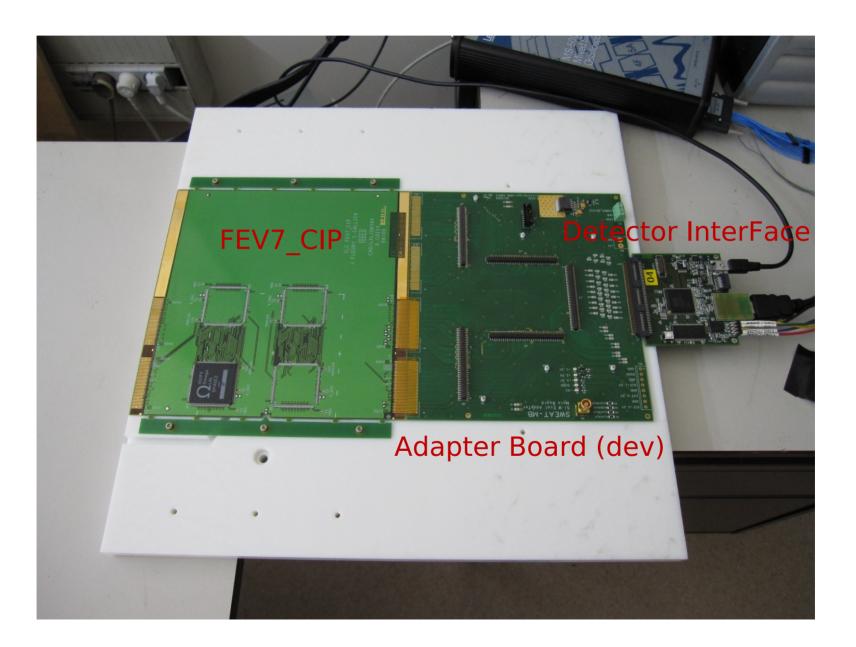

## FEV7-COB: with SPIROC2 COB

- Front End Board using Chip-On-Board (spiroc2=208 pads)

- Nearly Identical to Chip-In-Package FEV7

- Schematics identical

- Same number of channels

- Same pinout on Adapter Board/Slab Connector

- Except :

- Pads connections to chip pins

- Position of Wafer on the bottom side

- Thickness: thinner to comply with H alveolar structure

Next step towards FEE for Ecal established

#### **Goal: Ecal board FEV8 with SKIROC chip**

### **FEV N Issues**

- FEV7 feature untolerable bending ~3mm

- Industrial standard is 1% of diagonal (30cm for FEV7)

- Would lead to mechanical stress during assembly

- Alternative assembly may reduce bending by 50% (still intolerable)

- Dedicated effort to reduce initial bending by  ${\sim}50\%$

Remedies?: Contact with industry **Korean French collaboration within FKPPL** Contacts within AIDA?

#### Issue needs to be solved before before moving towards FEV8 FEV8 is actual board for SiW Ecal

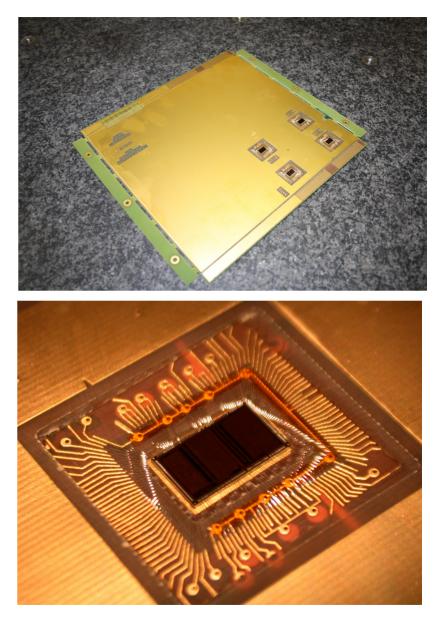

## PIN Diodes Silicon Sensors

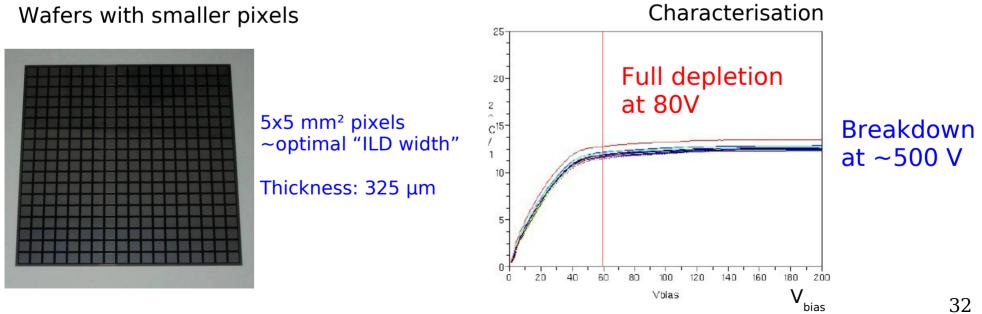

Designed for ILC : Low cost, 3000 m2 Minimized number of manufacturing steps Target is 3 Euro/cm2 Now : 10 Euro/cm2 Somewhat reduced for mass order

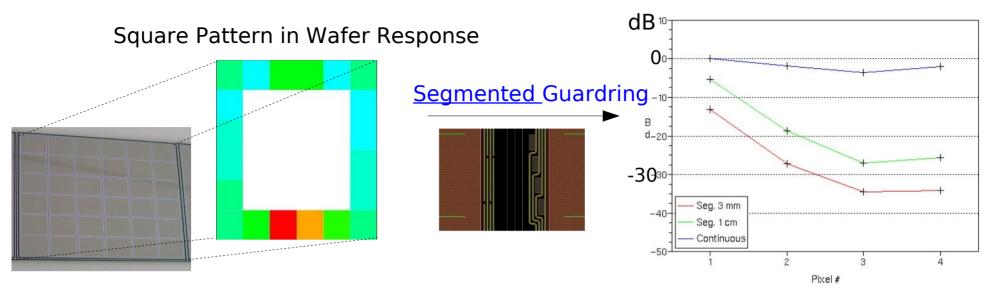

Guard-rings do not collect charges Dead space to be reduced

Hit map from physics prototype

#### French Korean Electronics Workshop 2011

#### Use of floating guard-rings

**EUDET layout** *Prototype from Hamamatsu*

FZŰ

- Discussions with CEA/LETI (november 09)

- 8 inches wafers, 4 matrices, 700 um thick (yield)

- ST microelectronics

- Visit to HPK confirm and complement what learned from LETI

- Will use 6 then 8 inches wafers

- 4 matrices processed at the same time (yield improvement)

- R&D on laser sawing

- Optimized thickness (yield vs width of dead space)

- Optimized call of offer

- ILD = 400% of production capability of a year (solid state devices division)

- Firsts contacts with VTT, SINTEF, MICRON semicond.

- In touch with PERKIN ELMER US & EU : both integration and manufacturing

- Not forgetting our historical collaborators : FZU (ONSemi), MSU, BARC, ...

- More discussions needed but a strategy is being build on "real" inputs from manufaturers

- R. Cornat: LLR

$\rightarrow$  Support by AIDA to purchase (several variants) of wafers

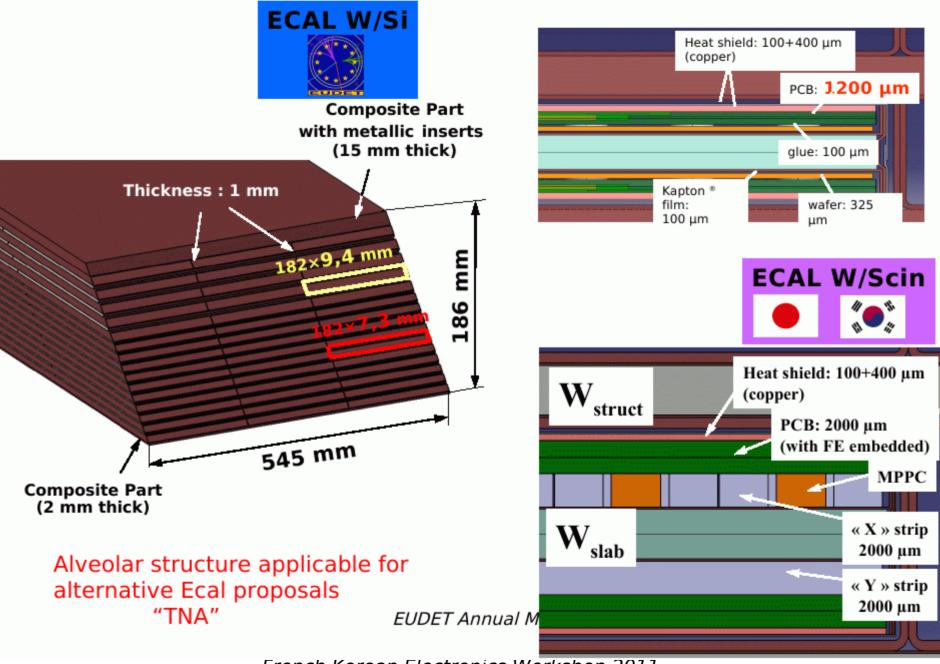

#### Study of alternative Ecal technologies

- 2011: Completion of absorber structure and  $1^{\mbox{\scriptsize st}}$  version of cooling system

- 2011 2012: Test beams ("electrical", cosmics, beams at DESY ) with small units

- 2011-2012: Continuous R&D on FEE FEV7/SPIROC  $\rightarrow$  FEV8/SKIROC Risks: Hidden design bugs, mechnical issues of FEV

- 2011-2012: Continuous R&D for low cost R&D Si wafers Progressive purchase of wafers

- 2013: Test beam with ASUs in absorber structure (CERN preferred) Risks: Shutdown of test beam site(s)

### Backup

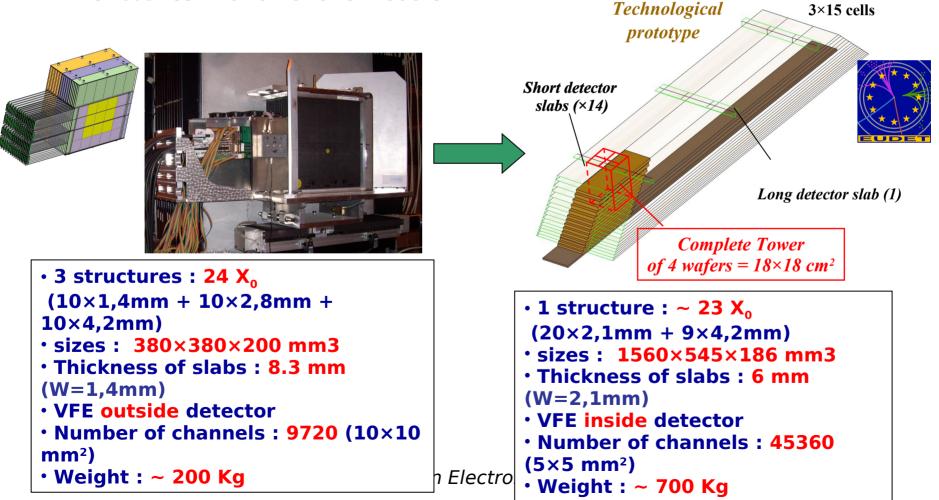

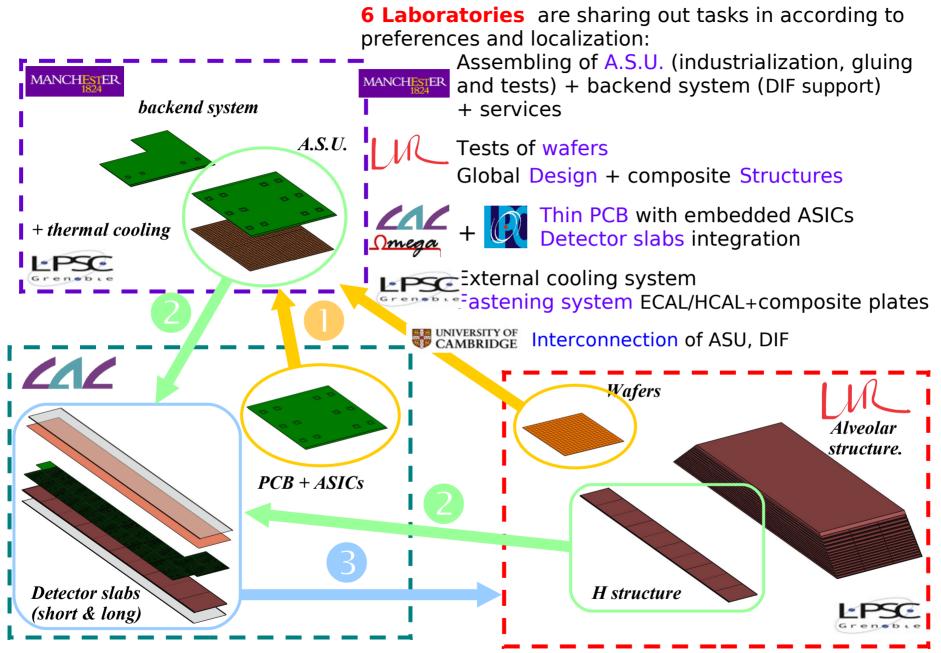

#### Evolution of Task – JRA3 Ecal EUDET Module

#### 2006

Conceptual Phase – Definition of Project Targets Detection of problems with Si-Wafer Guardrings and start of investigations for remedies

#### 2007

Decision to go for 0.5x0.5 cm<sup>2</sup> Si-Wafers instead of 1x1 cm<sup>2</sup> Wafers Contacting and negociations with manufacturers ⇒ Wafers with dimensions of 9x9cm<sup>2</sup> Continuation of studies for building large alveolar Structures Dimensions depend on wafer dimensions and constraints of challenging Very Front End Electronics

#### 2008

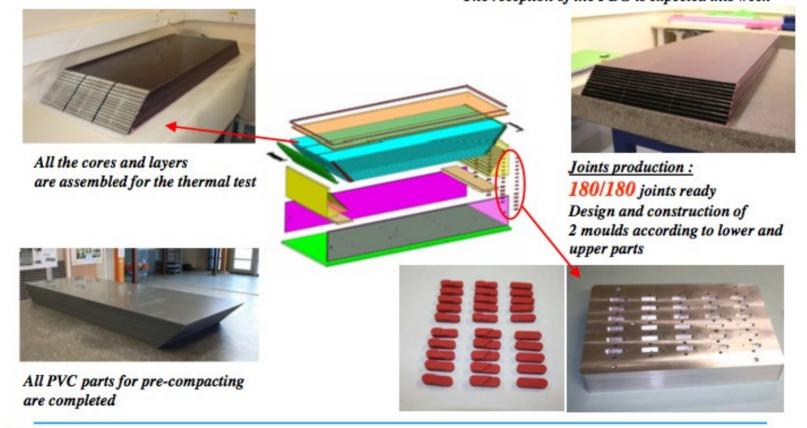

Decision to go for a demonstrator to allow for validation of mechanical concept Milestone: Design of Moulds and Alveolar Structures finished (EUDET-Memo-2008-07) Milestone: TDR of SiW Ecal EUDET Module – Details of design fixed (EUDET-Memo-2008-11)

Delivery and Examination of 30 Si-Wafers (Hamamatsu)

#### 2009

Demonstrator built and start of thermal studies Demonstrator is to be taken as EUDET Deliverable!!!! Ordering of pieces for 'real' EUDET module in autumn 2009 Next steps depend on progress of VFE Advancing the VFE has top priority 2010-2011 Towards the EUDET Module ?

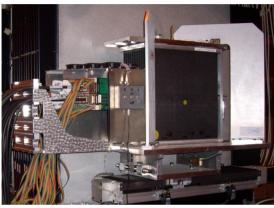

### **EUDET Prototype**

- Logical continuation to the physical prototype study which validated the main concepts : alveolar structure , slabs, gluing of wafers, integration

- Techno. Proto : study and validation of most of technological solutions wich could be used for the final detector (moulding process, cooling system, wide size structures,...)

- Taking into account industrialization aspect of process

- First cost estimation of one module

20

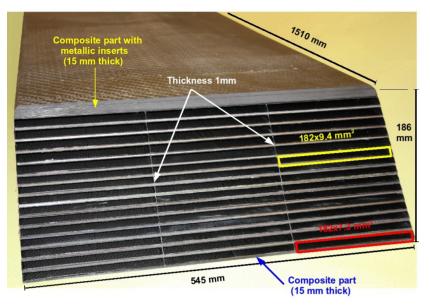

### **EUDET Module – Design**

### ECAL module - parts of Mould

⇒ Validation & Thermal tests : *Feb 2011* ⇒ Alveolar structure : *March 2011*

<u>Alveolar layer production :</u> **15/15** structures are been moulded The production of one layer is now stopped because we waiting <u>the FBG</u>. The reception of the FBG is expected this week

Frotin

3

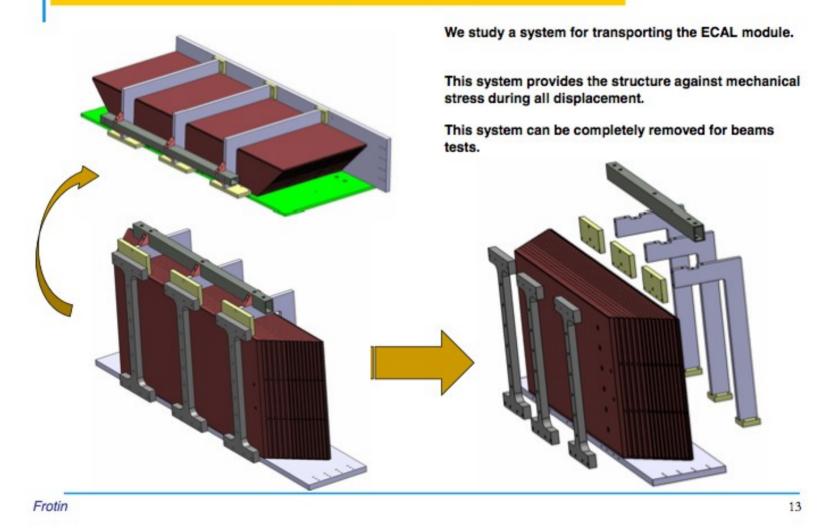

### ECAL module – Studies

⇒ what remains to be done: Design of transport system Jun 2011

Preparing EUDET Module for testbeams

## The ROC Chips

### **Parties Involved**

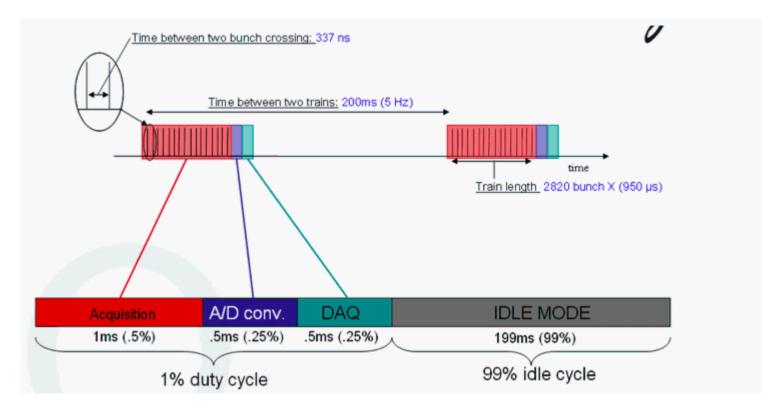

### **Power Pulsing**

#### Main tool to control power budget of LC calorimeters

- Electronics switched on during 1ms of ILC bunch train and data acquisition

Time constraints even more severe for CLIC

- Bias currents shutdown between bunch trains

### **FEV N Issues**

- FEV7 feature untolerable bending ~3mm

- Industrial standard is 1% of diagonal (30cm for FEV7)

- Would lead to mechanical stres to wafers during assembly

- Alternative assembly may reduce bending by 50% (still untolerable)

- Dedicated effort to reduce initial bending by  ${\sim}50\%$

Remedies?: Contact with industry Collaboration with corean groups Contacts within AIDA?

#### Issue needs to be solved before before moving towards FEV8 FEV8 is actual board for SiW Ecal

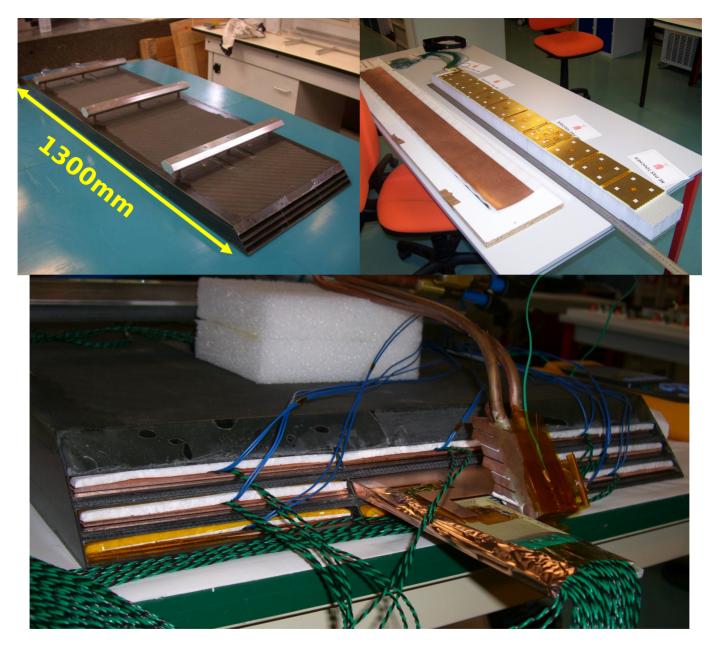

#### Assembly of Demonstrator

Detector module realised (from mechanical point of view)

Demonstrator subject to a thermal test French Korean Electronics Workshop 2011

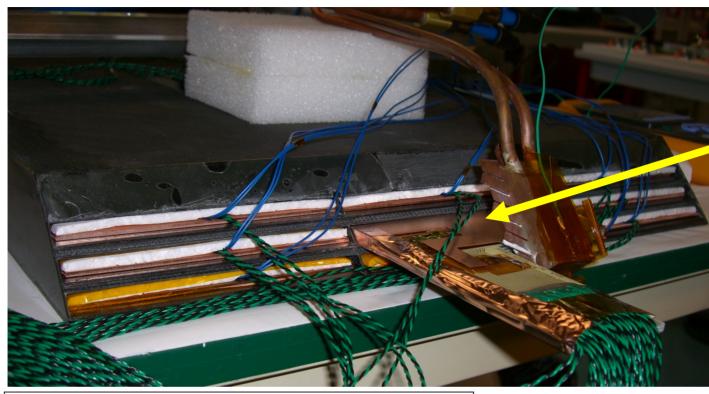

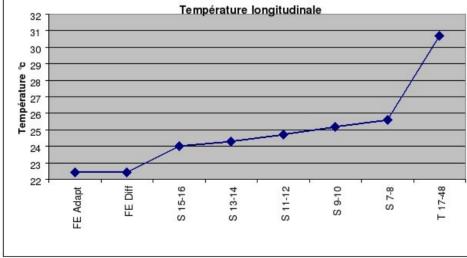

#### **Thermal Test**

#### To study thermal behaviour of detector module

#### Inserted Thermal Layer

| Ambient Temperature | 22   |        |       |

|---------------------|------|--------|-------|

| Alveolar Slot       | Left | Middle | Right |

| External            |      | 23.5   |       |

| Upper               | 24.8 | 24.8   | 24.6  |

| Lower               | 25   | 30.7   | 25.2  |

| Bottom              | 25.1 | 25.2   | 25.1  |

Detector Module realised from mechanical point of view Thermal test important for DBD

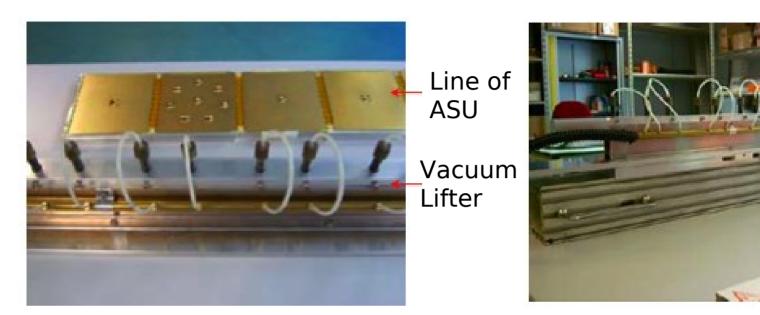

Assembly Tools – Handling of fragile layers

Handling by vacuum lifter

Positioning of Vacuum Lifter on ASU Line

Vacuum Lifter Line of ASU

### (Careful) handling of ASU Line established

- Detector Assembly needs more tools and an assembly hall

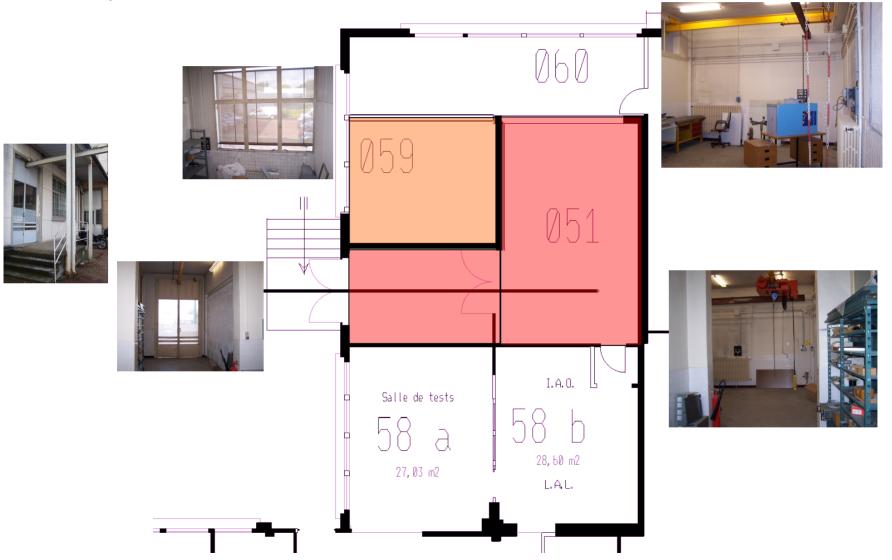

#### LAL allocated facilities for Ecal

*Hall present state*\_(hall 051:47m2 and hall 051+ hall 059:64m2)

23 September 2010 Casablanca, Morocco French Korean Electronics Workshop 2011

**R&D** for Silicon Wafers

Xtalk <u>Continous</u> Guardring <-> Pixel

Attenuation of Xtalk

#### Beyond the Physics Prototype

# First SLAB prototype (01/07/09)

Conclusion and outlook- Towards the EUDET Module

- Construction of alveolar structure for 'real' EUDET Module proceeds well

- Infrastructure for detector assembly about to be established Assembly hall with cosmics test bench at LAL

- Focus of getting the VFE accomplished

- "Shipping" signals out Interface to the DAQ is addressed

- Results with first ASU expected in the coming months Depends on development of DAQ interface

- (Crucial) Step from ensemble FEV7/SPIROC  $\rightarrow$  FEV8/SKRIOC to be realised

- Cost for Silicon wafers is an issue (well beyond EUDET matters)

- Beam tests with EUDET Module (foreseen within AIDA)