## Progress on FEV7/8 at SKKU

S.H. LEE, H.J. CHOI

## Contents

- 1. Introduce

- 2. Research in the Omega

- 3. Measurement of SPIROC 1 test board

- 4. Design of FEV7 PCB

- 5. Design of FEV8 layout

- 6. Progress at SKKU

- 7. Some problems of FEV board

- 8. Q&A

## Introduce

#### **CALICE Project**

In particle physics, French scientists from Laboratoire de l'Accélérateur Linéaire (CNRS-IN2P3/Université Paris Sud) and Laboratoire Leprince-Ringuet (CNRS-IN2P3/Ecole Polytechnique) collaborate actively with Korean institutes to develop new detectors for the future International Linear Collider which is scheduled to start operation in 2020.

## Research in the Omega

During 5 months in 2010, I stayed in Omega to research about read-out chips and FEV boards.

Ms. Choi stayed during 2 months, also.

Co-work is really helpful both Korea and France to go on the research about CALICE project.

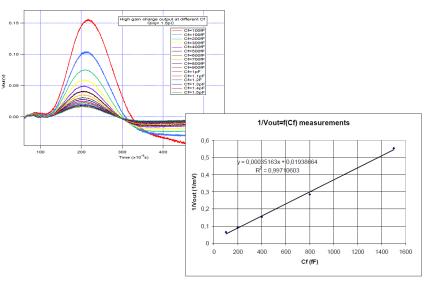

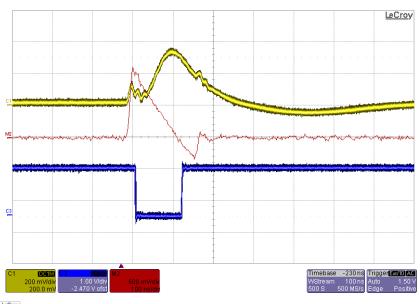

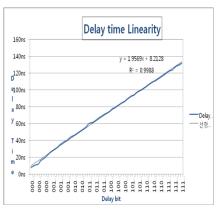

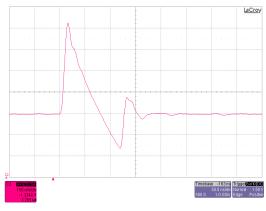

## Measurement of SPIROC 1 test board

Measurement of SPIROC 1 test board of analog signal.

Energy measurement

Time measurement

Trigger delay

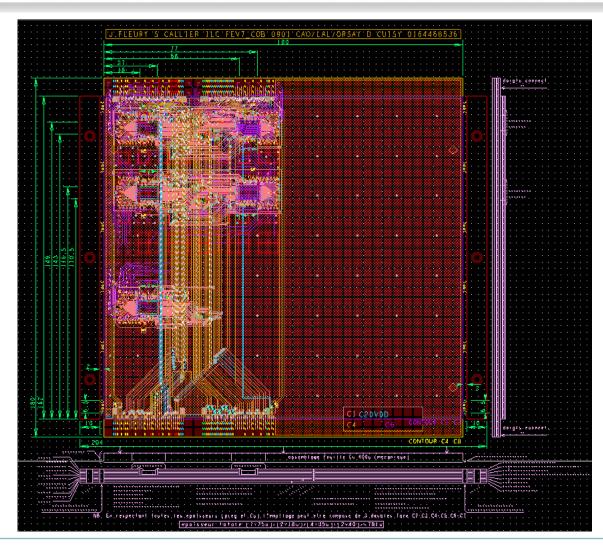

## Design of FEV7 PCB

FEV7 CIP FEV7 COB1 FEV7 COB2

FEV7 COB1 with 5chips

#### Purpose

- 1. Understand how to operate the board.

- 2. Become familiar with tools.

- 3. Design FEV7 boards.

- 4. Design new versions for manufacturing in Korea.

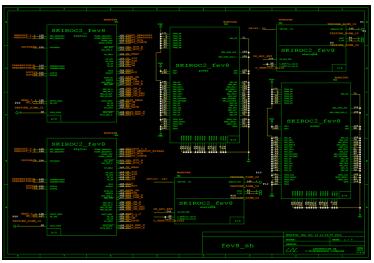

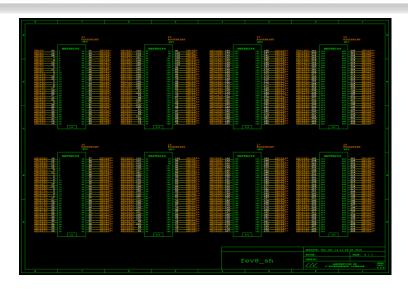

## Design of FEV8 Schematic

#### The next version of FEV board.

It will used for ECAL.

16 SKIROC2 chips

The final version of FEV board.

Laurens: 8 chips in only a left side. Ms. Choi: 16 chips in both sides.

## **Progress at SKKU**

Tools

Allegro Design Entry 16.3 HDL L

Allegro SI/PI

NI LabView 10.1

Tools for designing chips

2. Find some companies to make boards

Unfortunately, Some problems have occurred!

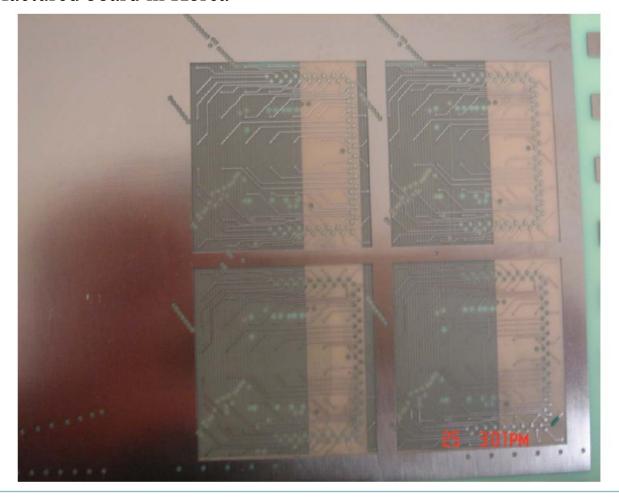

#### Technical problems

- very small diameter of vias and complicated structure to make

- digging some space to insert each chip(COB, COB2)

#### Economical problems

- extremely difficult to success

- commercial production

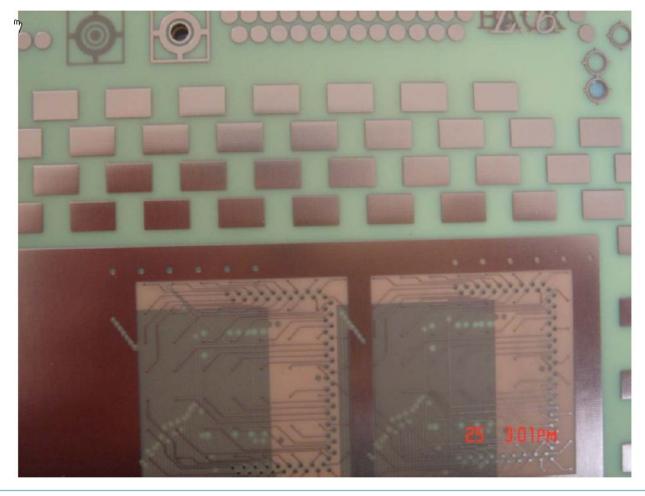

#### Manufactured board in Korea

#### Manufactured board in Korea

#### **Problems**

- 1. Spark at signal circuit

- 2. Leakage the current between conductors at the boards

- 3. Cut the circuit lines

#### Improvement

- 1 Bilaminar PP

- 2. Adjustment of conductor thickness

- 3. Strengthen insulation

# Q & A

AnME Lab. of Accelerator & Medical Engineering