# TRACKING AND VERTEXING SUMMARY

Suyong Choi Korea University

## **Outline**

- Vertex/tracking detector for ILC

- Vertex detector for CLIC

- LCTPC

# DEPFET

## DEPFET

#### Applications

- Belle-II  $50x75 \mu m^2$  ,  $75 \mu m$  thick

- ILC 25x25  $\mu m^2$ , 50  $\mu m$  thick

#### PXD6 Sensor Production

• 50 micron thick sensors (50x75 and 50x50  $\mu m^2$  ) produced

#### PXD9 Sensor

- Final design for Belle, 75 micron thick

- Plan: Prototype run followed by production run

#### ASICs

- Close to final designs ready, produced and working

- DHP02 needs to be moved to TSMC 65nm process

#### DCD (drain current digitizer)

fully functional at full readout speed (600MHz)

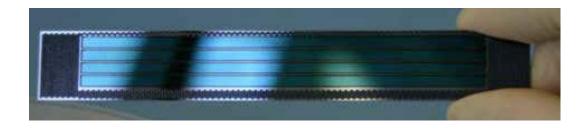

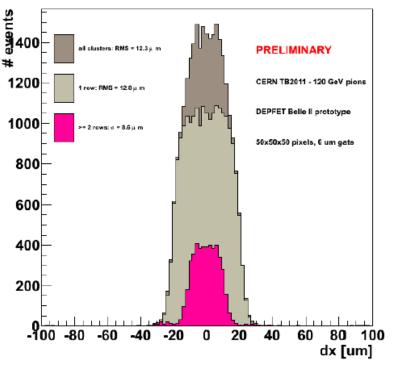

## **DEPFET Test Beam**

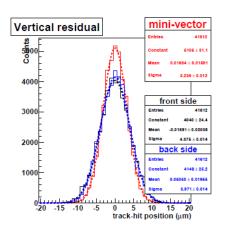

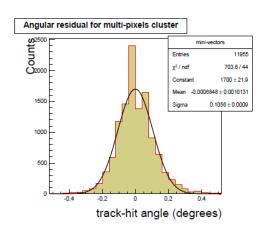

- PXD6 and ILC designs readout at 100MHz or 320 MHz

- Results

- ILC design: S/N: 20 ~ 40

- $25x25 \mu m^2$ ,  $450 \mu m$  thick sensor

- Belle2 design:S/N  $\sim$  40 for 50  $\mu m$  thick sensor

- translates to S/N ~ 60 for 75  $\mu m$  thick

- Position resolution for Belle2 design 12  $\mu m$  slightly better than binary RMS (14.4 micron)

- Thin sensor performance demonstrated!

# DEPFET – Cooling

### Cooling

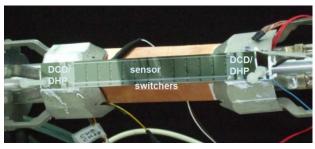

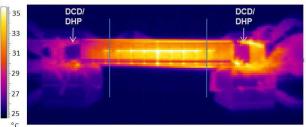

- Mockup and simulation tools used

- Belle-II (air + liquid cooling), ILC (air cooling)

- 1 m/s air flow needed for sufficient cooling

- 2 μm deformation for 2 m/s, 0.7 μm amplitude vibration

## ILC cooling

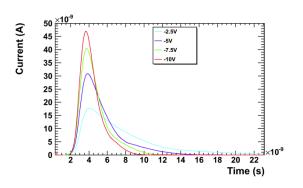

- Power pulsing exercised

- FEM analysis set up

- Port belle-2 mock up to ILC

- By DBD, full measurements

+ simulations

#### Mockup for Belle II

# CPS – CMOS PIXEL SENSOR

## **CPS for ILD-VXD**

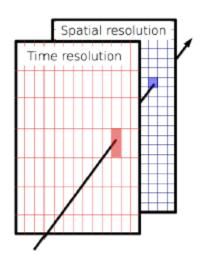

- Two types of CPS

- Inner layer 300 cm<sup>2</sup>, resolution

- Outer layer 3000 cm<sup>2</sup>, power consumption

- 16x16  $\mu$ m<sup>2</sup> for spatial resolution  $t_{ro}$  ~ 50 $\mu$ s

- 16x80  $\mu$ m<sup>2</sup> for time resolution  $t_{ro}$ ~10 $\mu$ s

- For time stamping

- Sensor prototypes produced in Q4/2011

- Mimosa 30 inner layer prototype

- Mimosa 31 outer layer prototype

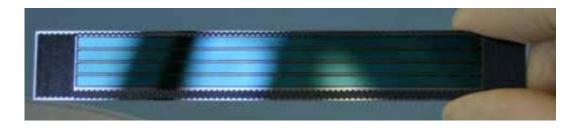

## **CPS**

- Double sided detector:

- 6 mimosa-26 on each side of ladder, 8M pixels

- Test beam in Q4 2011 @ CERN SPS  $\pi^- > 100$  GeV beam

- New 0.35% X<sub>0</sub> prototype under construction

- Beam test in Q4 2012

## **CPS**

- Mimosa 30

- 8x256 with 16x16 μm² pixels, 8x64 with 16x64 μm² pixels

- 15e ENC with 10 μs readout

- Beam test in Jun/Jul

- Mimosa 31

- 48x64 with 35x35 μm² pixels

- Beam test in 2013

- Meets VXD specs for  $\sqrt{s} = 500$  GeV

- For  $\sqrt{s} = 1$  TeV

- $0.35 \rightarrow 0.18 \,\mu m$  process

- Faster readout 2(inner)/10(outer)

μs with accelerated read out techniques

- >20% Less power consumption, good sensor throughput

- Mimosa 32 exploratory chip under test

- Prototypes for validating architecture to be submitted Q3/Q4 2012

- Full scale block in 2013

- Full scale prototype in 2014/15

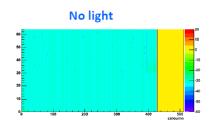

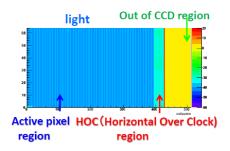

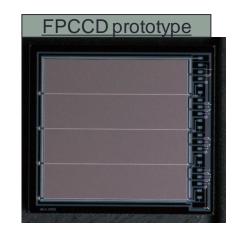

# FPCCD - FINE PIXEL CCD

## **FPCCD**

- 2<sup>nd</sup> FPCCD readout ASIC

- Total noise 16e < 30e</li>

- prototype power consumption:

30.9 mW/ch > 6 mW/ch

- 3<sup>rd</sup> FPCCD readout ASIC

- Changes to analog and digital readout

- Process: 0.35 μm to 0.25 μm

- 5.4 mW/ch

- DNL and INL improved to within ±1LSB and 0.38%

#### Plan

- 2<sup>nd</sup> Prototype test using radiation sources

- 3<sup>rd</sup> prototype chip arrival in Oct

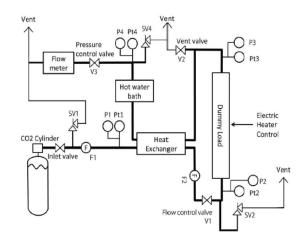

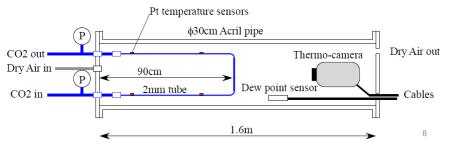

# Cooling of FPCCD Vertex Detector

- To minimize charge transfer inefficiency due to radiation damage cooling to -40 C is optimal

- Use two-phase CO<sub>2</sub>

- Large latent heat of C02

- Smaller flow rate

- Cooling system test mock up

- No condensation

- Heat penetration 20W/m measured

- Plans

- Cooling test of dummy ladder/endplate

- Circulating system

CO<sub>2</sub> cooling blow system between -40C and 15 C

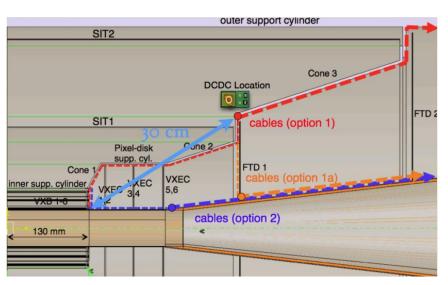

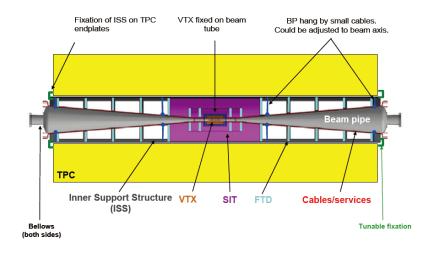

# FORWARD TRACKING

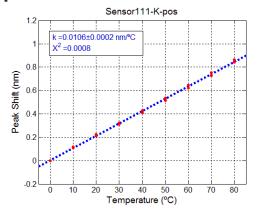

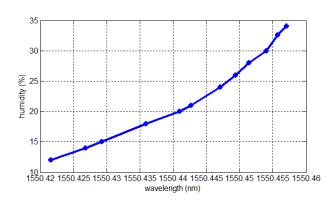

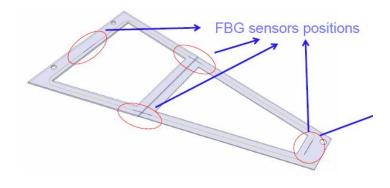

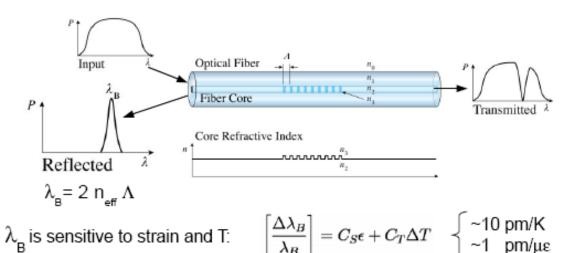

# Fiber Bragg Grating sensor for FTD

Temperature and humidity measurement with FBG

Sensitive to strain and deformations

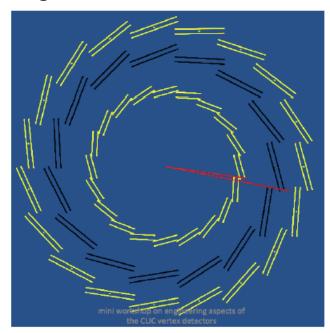

# CLIC VERTEX DETECTOR

## VTX requirements for CLIC

- Vertex requirements

- Efficient tagging of heavy states: 3  $\mu m$  spatial resolution

- <0.2% X<sub>0</sub> per layer

- Coverage to 7°

- Occupancy ~ A few %

- Time stamping with 10ns accuracy to suppress bkgs.

- No technology that fulfills all requirements

- Simulation impact of layout

- Integration/assy., power pulsing, cooling

- R&D on sensor and readout

- Post CDR design

- Minimize cabling, vertical integration

- inactive regions, Lorentz angle

## Vertex Detector R&D for CLIC

- Pixel technology

- $25x25 \mu m^2$

- 10ns time stamping

- 0.2% X<sub>0</sub>: 200 micron thick Si –incl. support and cables

#### Hybrid

- Thinned detector (50 micron thickness) + readout chip (50 micron thickness)

- Need low mass Interconnect

- Hard to reduce material, difficult/expensive interconnect

- CLICpix: 65nm process, 25x25  $\mu m^2$ , ~2015

- Test structures on 65nm tested OK

- Demonstrator prototype to be submitted 2012: 64x64 pixel array

#### Integrated tech

- 3D integration of sensor and readout chip

- Charge collection in epitaxial layer  $<1\mu m$

- More Difficult to achieve good time resolution with sufficient S/N

- TSV (medipix 3), edgeless sensors

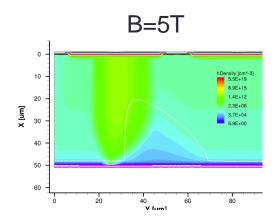

## **Simulations**

#### Sensor

- Charge collection

- Charge sharing

- Signal rise time

## Backgrounds

- 5~10 hits per cluster for innermost vertex barrel layer from incoherent pair backgrounds

- 0.5%~1% occupancies

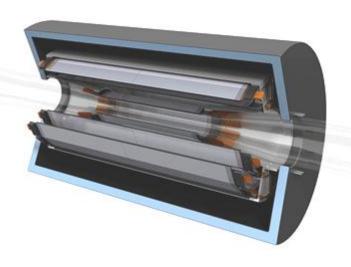

## Power and Cooling

#### Power

- Kapton flex cable

- Deal with large and short current peaks

- Large currents along ladders

- stitching across modules

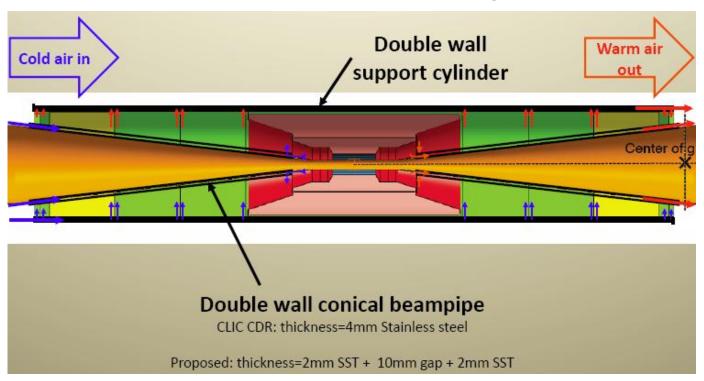

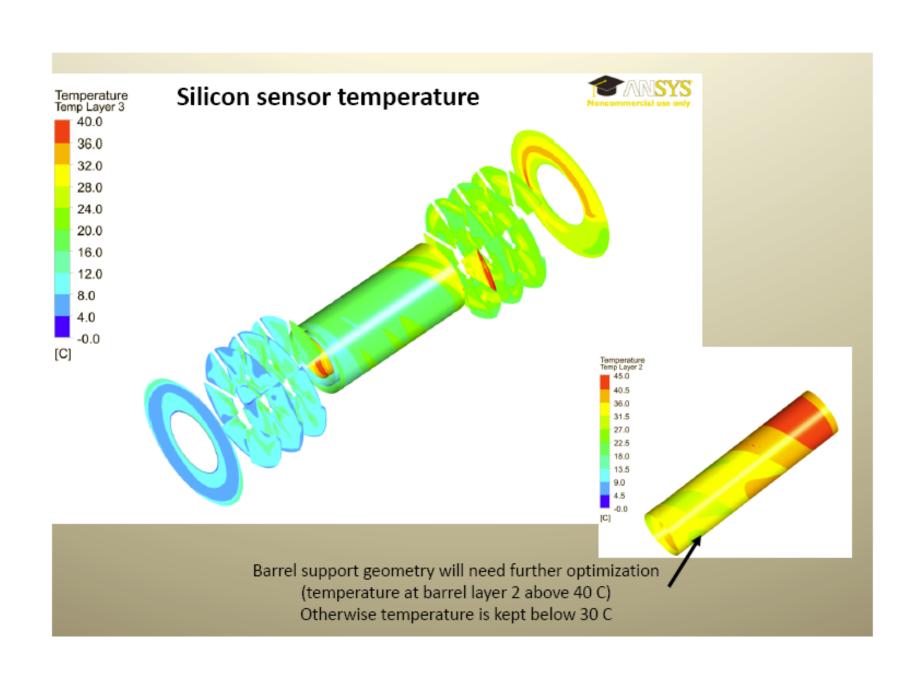

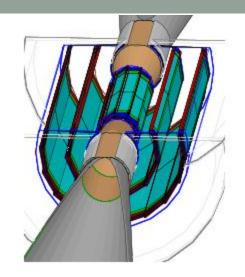

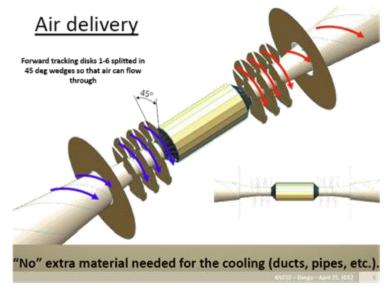

### Cooling

- Helical motion of air through double walled beam pipe and support

- Air speed: 11m/s at inlet

- Sensor deformation: ~ 2μm

- Due to special barrel support

- Looks promising

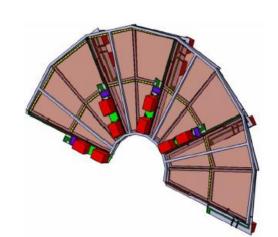

# LCTPC

## LCTPC Status

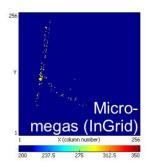

### MPGD Technologies

- DESY GEM (50  $\mu m$ ), triple GEM, new module tested end of summer

- Asian GEM  $(100 \ \mu m)$  modules, double GEM, new processing, new readout electronics in 2013

- Micromegas new modules with integrated electronics should be tested in large prototype in DESY in July

#### Timepix

- Readout with both GEM and Micromegas

- Full module work started 120 timepix chips, 8M pixels

#### SALTRO16

- power pulsing reduces power by 1/60.

- Work started on final version (GdSP) for LCTPC

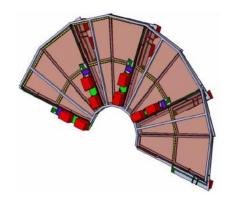

## LCTPC

- Prototypes

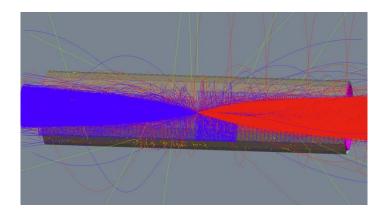

- LP1 test beam at DESY (1-6 GeV electron beam)

- LP2 upgrade from LP1

- Magnet using cryocoolers

- new end plate(realistic material budget)

- new cage field (end of 2012)

- Simulation suggests ion back-drift in amplification cause

60 micron distortion. Gating system may be needed.

- Plans

- Upgraded test beam facility to test momentum resolution

- Hadron beam to test multitrack environment

# **BACKUP**

## DEPFET

- In-pixel amplification, thin active sensor, low power consumption

- All silicon module one material, self-supporting sensor

- Application: Belle-II and ILC

- Belle-II requirements: 0.15% X<sub>0</sub> /layer, higher occupancy (x4) and radiation (x10) than ILC

- Belle-II  $50x75 \mu m^2$  ,  $75 \mu m$  thick

- ILC 25x25  $\mu m^2$ , 50  $\mu m$  thick

## FPCCD vertex detector

- Fine Pixel CCD

- Pixel size ~ 5μm

- Fully depleted epitaxial layer

- Read out between trains (No power pulsing)

- FPCCD vertex detector

- Double-sided ladder

- 1.6x10<sup>10</sup> pixels

- Sensors and front-end ASICs inside a cryostat

- Power consumption > 50W inside the cryostat

- Readout ASIC

- Total power < 100W</li>

- 10 Mpix/sec

- Noise + ADC accuracy < 30e (signal size 500 e)</li>

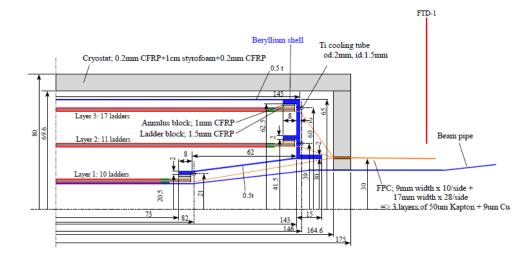

# CO<sub>2</sub> cooling for FPCCD VTX

- Cooling tube is attached to VTX end-plate and heat removed by conduction through CFRP ladder

- Return line of CO2 will be used to cool the electronics outside the cryostat (~200W/side)

- Inner support tube should be air-tight and filled with dry air/nitrogen in order to prevent condensation on the CO2 tube

# Fiber Bragg Grating Monitoring

Fiber Bragg Grating sensor principle

- Environmental and structural monitor

- Low material budget

- Immune against high EM fields

- Can be used in high and low temp.

- Suitable in radiation environment

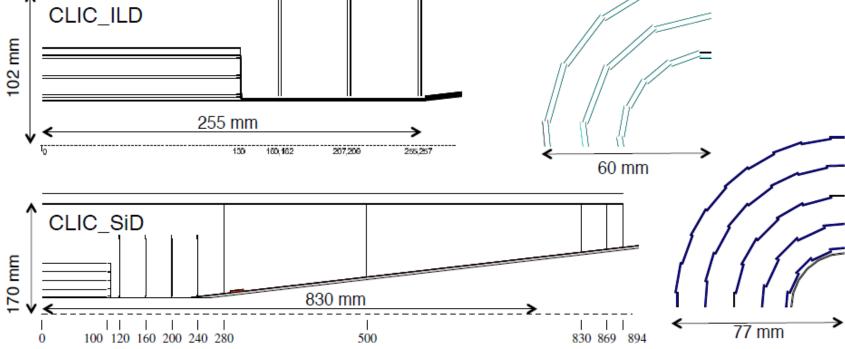

CLIC vertex detectors simulation layouts

|                     | CLIC_ILD                | CLIC_SiD                | CMS                       |

|---------------------|-------------------------|-------------------------|---------------------------|

| Material X/X0 (90°) | ~0.9% (3x2 layer)       | ~1.1% (5 layer)         | ~10% (3 layer)            |

| Pixel size          | 20 x 20 μm <sup>2</sup> | 20 x 20 μm <sup>2</sup> | 100 x 150 μm <sup>2</sup> |

| # pixels            | 1.84 G                  | 2.76 G                  | 66 M                      |

| Time resolution     | ~10 ns                  | ~10 ns                  | <~25 ns                   |

| Avg. power/pixel    | <~0.2 μW                | <~0.2 μW                | 28 μW                     |

April 24<sup>th</sup> 2012

Vertex-Detector R&D for CLIC

# Cooling

Power: 500W (50mW/cm²)

Forced dry air – baseline for barrel region