# **ROC chip status**

#### S. Callier, S. Conforti, L. Raux, F. Dulucq, C. de La Taille, G. Martin-Chassard, N. Seguin-Moreau

Orsay Micro Electronics Group Associated

#### HARDROC3

- First of the "3<sup>rd</sup> generation ROC chip" to be submitted O AIDA

- independent channels, one register/channel, I2C link for SC parameters(@IPNL), triple voting, circular memory, temperature sensor

- Digital part finished in July 2012

- Analog part: No major modifications in the analog part. Extension of the dynamic range to set Vth0=100fC Vth1=5pC and Vth2 > 15 pC

- HR3 won't be pin to pin compatible with HR2 and packaged in TQFP208 instead of TQFP 160 (same size and thickness)

- $\Rightarrow$  New 1 m2 RPC chamber to be built to test HR3 at the system level

- Die size ~30 mm2

- Chip design in its final stage. <u>Submission in November 2013</u> => reception in March 2013. Aida report to be delivered in August 2013

#### • SPIROC3/SKIROC3:

- More complex chips (internal SCA, ADC, TDC): many parts still to be tested on test bench and at the system level

- Hardroc3 test feedback necessary before submitting Spiroc3/skiroc3

<u>)mega</u>

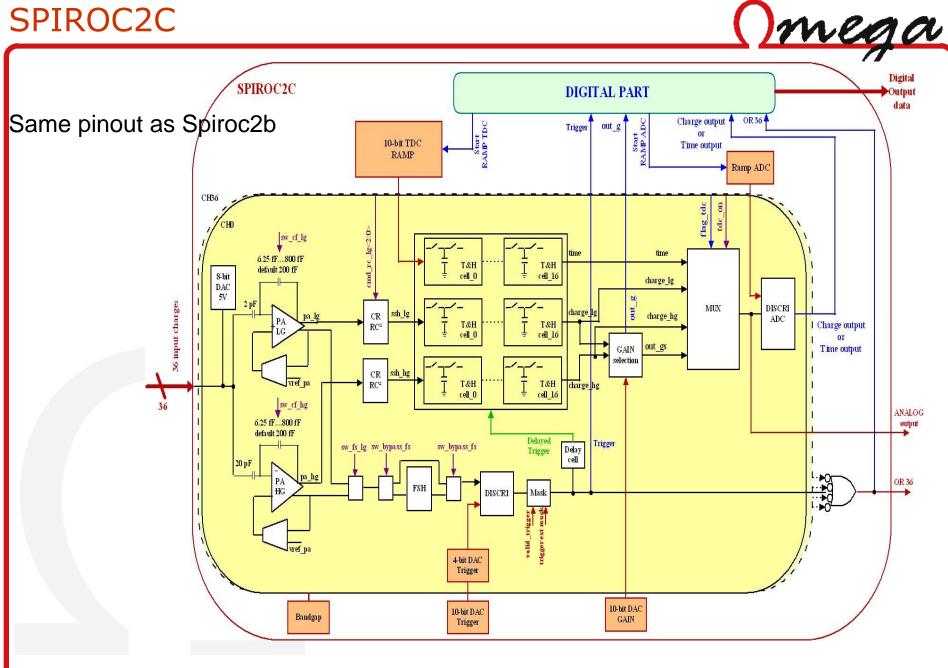

Spiroc2c: before submitting SPIROC3. Pin to pin compatible with spiroc2b so measurements can be performed at the system level using the existing HBUs

- Spiroc2c received in June 2012 and under test

- **New input preamp** (NMOS transistor instead of PMOS):

- pedestal shift problem in spiroc2b : CORRECTED in spiroc2c

- Rate dependency in 2b: CORRECTED in 2c

- Coupling HG/LG: CORRECTED in spiroc2c

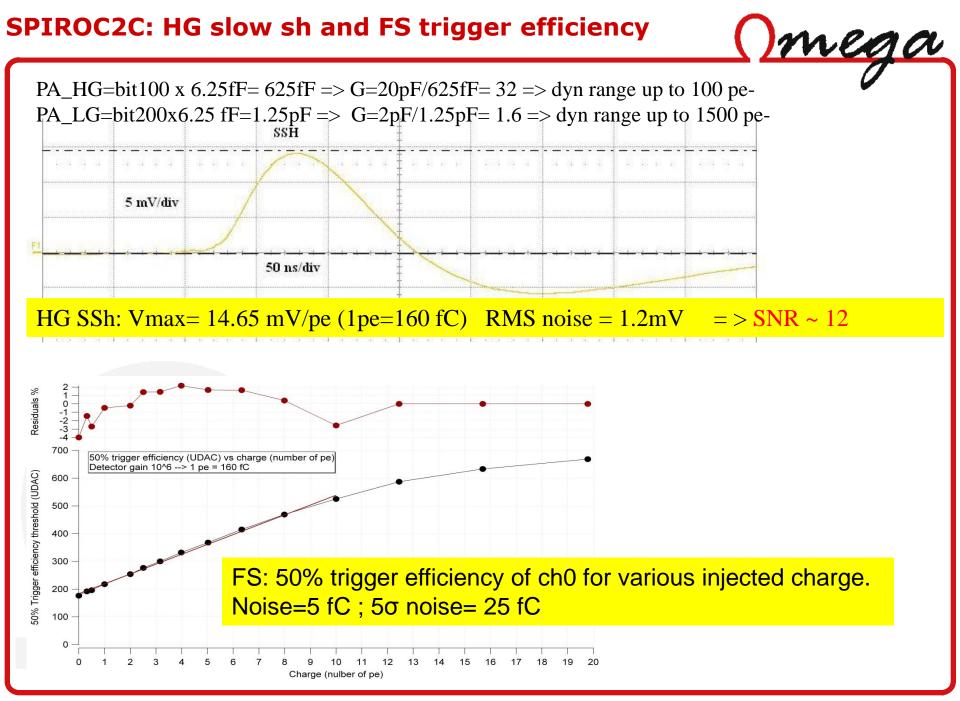

- LG and HG preamp gain can be changed independently in 2c

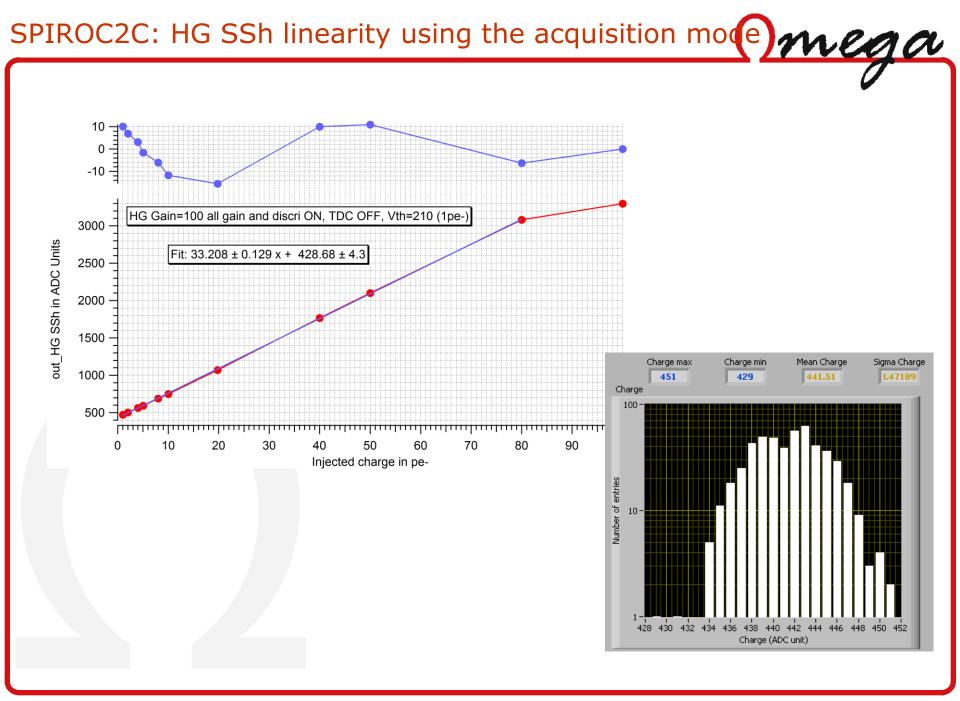

- HG: Cin=20pF, Cf = 6.25 fF x (1 to 255)

- LG: Cin=2pF, Cf= 6.25 fF x (1 to 255)

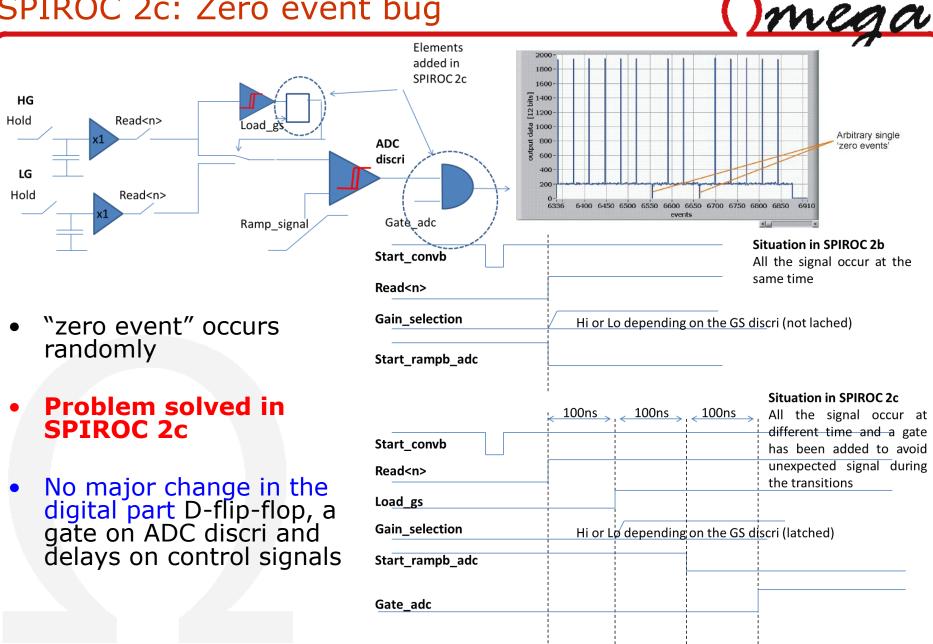

- "zero" events pb in 2b: CORRECTED in 2c

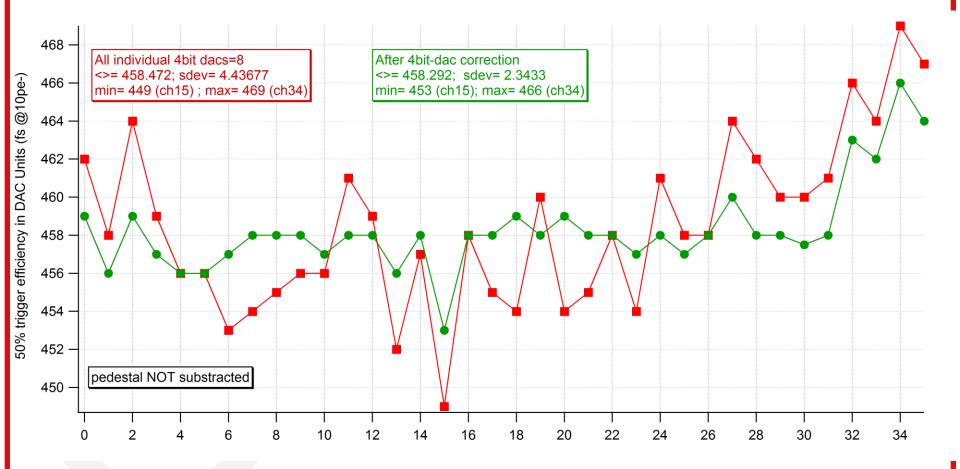

- 4-bit Channel wise threshold tuning: difficult in 2b as the tuning of one channel depends on the others. CORRECTED in 2c

- New TDC to decrease deadtime: done

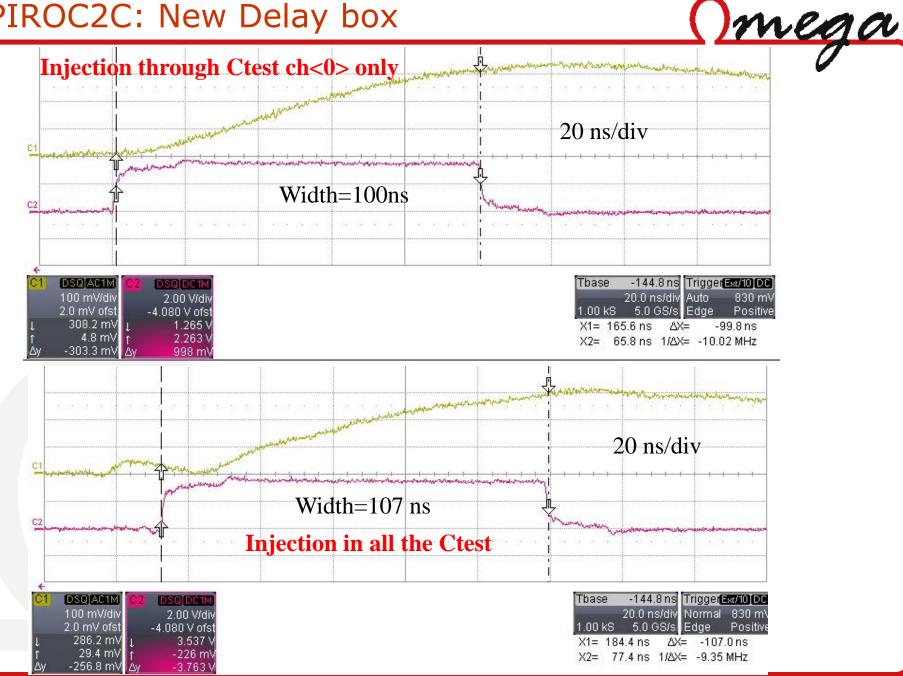

- New Delay box

- Input 8-bit DAC: layout redone to improve the slope uniformity: no difference...

meaa

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

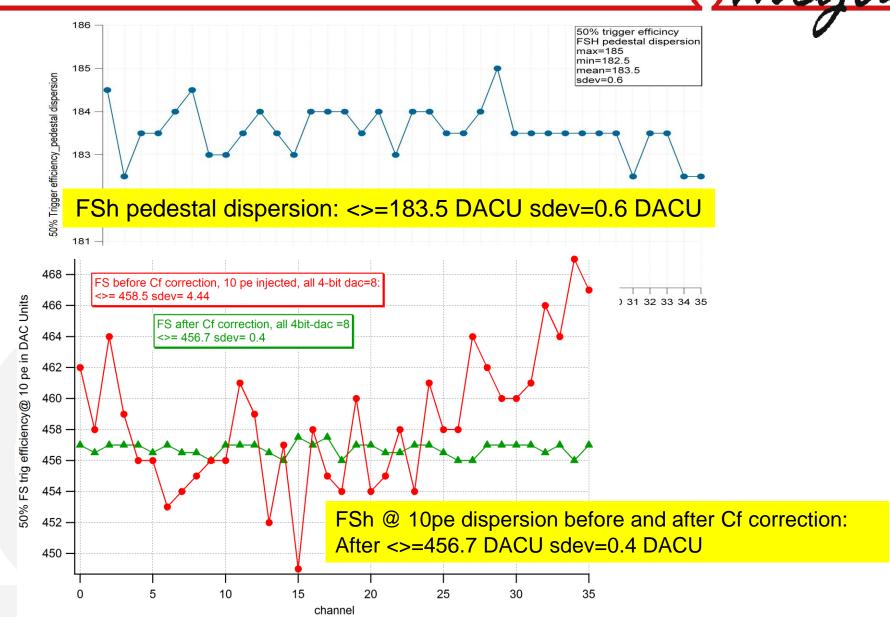

SPIROC2C: 4 bit DAC channel wise tuning

#### FS@ 10 pe injected

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

<u>(mega</u>

# SPIROC2C: FS Uniformity and Cf correction Omega

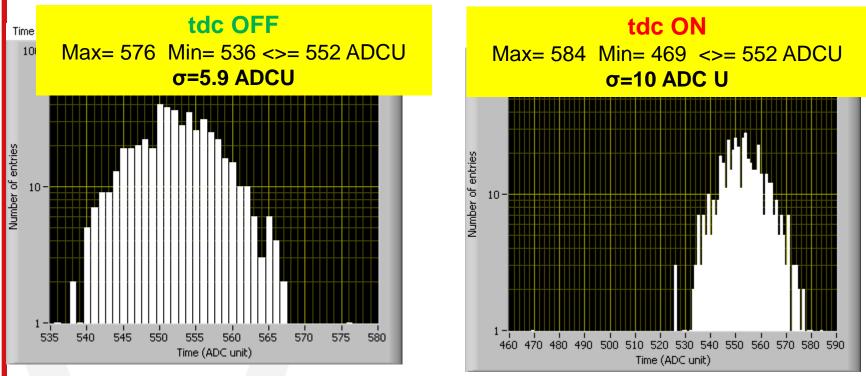

## Spiroc2c: Digital coupling

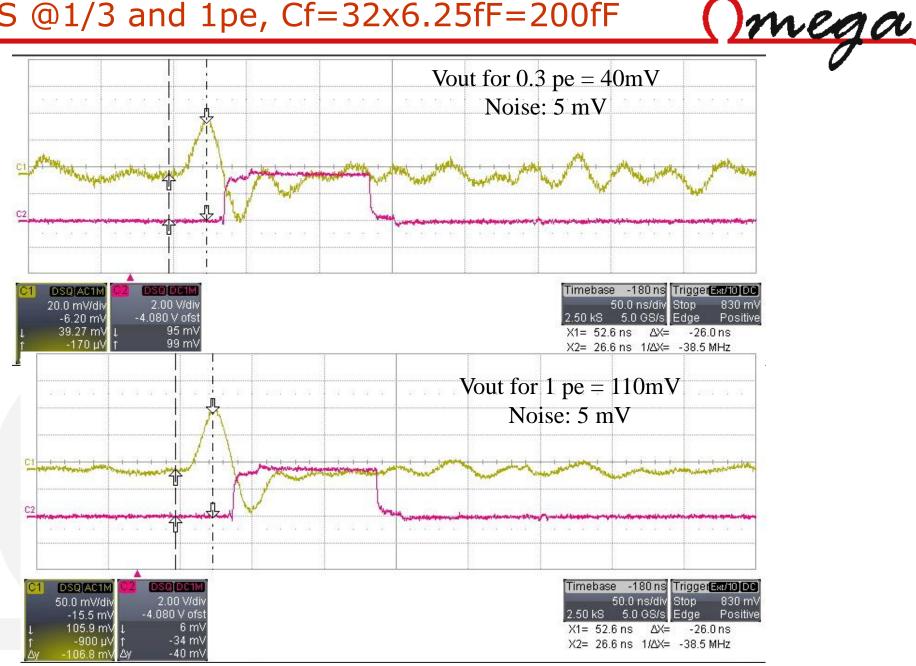

Acquisition using the autotrigger mode Injection through 100pF, 1 pe- (1.6V@60dB), HG Ssh @ 50ns Cf=200fF ( $32x \ 6.25fF \Rightarrow G=100$ ) for all the channels, Vth=230 (=0.5 pe-)

Pedestal~ 450 ADC Units

TDC => digital coupling in spiroc2c through the substrate (NMOS preamp connected to gnd) There is no digital coupling in spiroc2b (PMOS transistor connected to vdd)

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

()mega

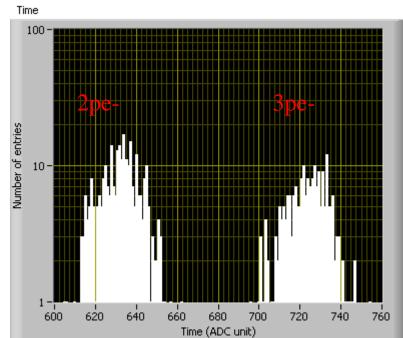

## Digital coupling in Spiroc2c

Injection through 100pF, 2 and 3 pe-, Cf=200fF (G=32) for all the channels, ssh@50ns Vth=260 (~1pe-)

HG ssh, tdc OFF Time Time 100 100 Number of entries Number of entries 10-10 -600 620 640 610 620 630 640 650 660 670 680 690 700 710 720 730 740 750 Time (ADC unit)

#### TDC coupling in Spiroc2c doesn't prevent to distinguish 2 and 3 pe-

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

## HG ssh, tdc ON

## CONCLUSION

- HARDROC3: submission in November 2012

- Spiroc2c:

- Spiroc2b "bugs" corrected

- Very good performance of Spiroc2c when the TDC is OFF

- BUT DIGITAL COUPLING through the substrate which prevents to set the threshold < to 1pe.</li>

- Anyway it would be interesting to equip HBUs with spiroc2c and check the performance in TB conditions

- Many measurements to be done on testbench

mega

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

mega

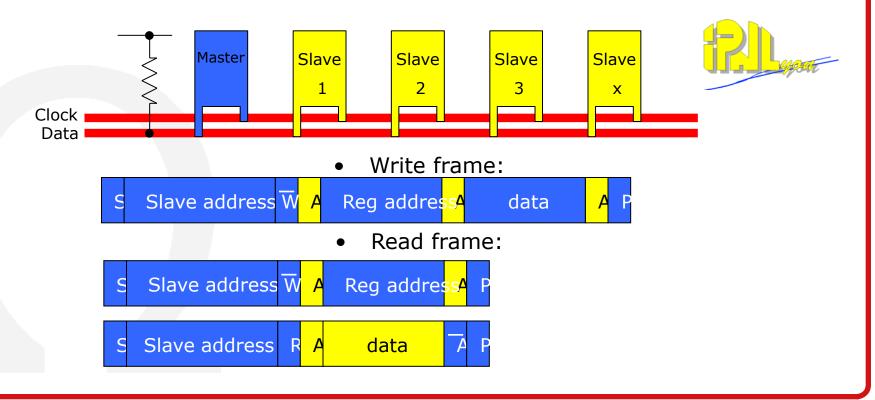

## 3Gen ROC chips: common features

- Slow control parameters:

- Backward compatibility with 2Gen ROC chips slow control

- Use of classical shift register slow control

- Embedded I2C

- 7-bit address + 1 general call address (127 chips can be addressed)

- Access port doubled

- Bidirectional data line with open collector (Driver will be the same as Dout)

- Read back capability of SC bits (non destructive)

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

(<u>)mega</u>

#### 3Gen ROC chips: common features

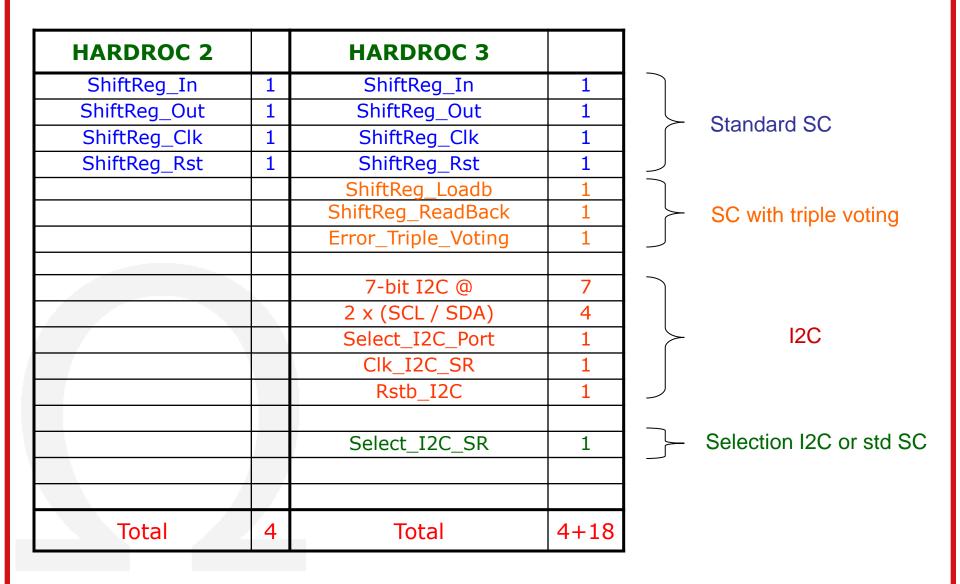

• Extra pin needed for I2C / SC:

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

<u>()mega</u>

#### SPIROC2C

#### FS @1/3 and 1pe, Cf=32x6.25fF=200fF

« Pedestal shift » due to coupling on Vdda\_pa on spiroc2b

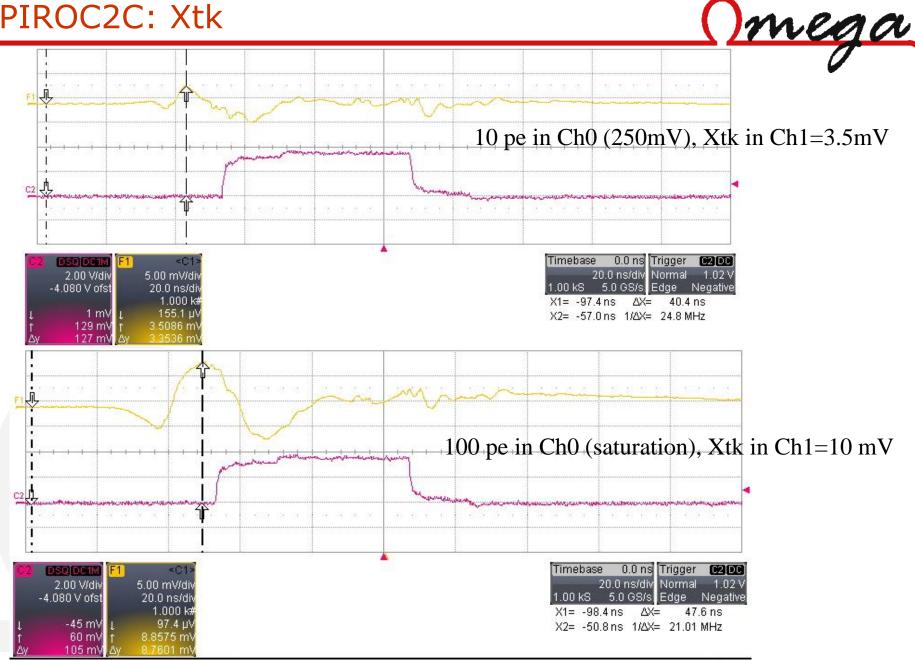

Spiroc2c: Injection of 10, 100, 300 and 1000pe- in ch0 and measurement of the charge (HG) seen on the neighbours (all preamp on but all discris masked except of ch<0>:

|        | 10pe-    | 100pe- | 300pe- | 1000pe- |

|--------|----------|--------|--------|---------|

| Ch<0>  | 950 UADC | 3500   | 3500   | 3500    |

| Ch<1>  | 470      | 470    | 450    | 450     |

| Ch<2>  | 470      | 460    | 440    | 440     |

| Ch<3>  | 460      | 463    | 446    | 446     |

| Ch<20> | 460      | 457    | 450    | 450     |

| Ch<35> | 455      | 457    | 455    | 455     |

When discris of the other channels are ON = > we measure Xtk in the neighbours

CALICE meeting Cambridge 16-19 Sept, 2012 N.Seguin-Moreau

mega

#### SPIROC2C: Xtk

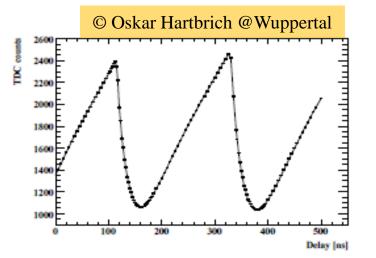

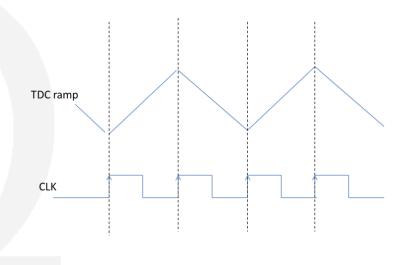

#### SPIROC 2c: TDC

- Modifications of the TDC

- To decrease dead time during transition => alternation of a rising and a falling ramp implemented

- Conservative modification

- a new TDC has to be re-designed in SPIROC 3

<u> Mega</u>

#### SPIROC 2c: TDC

<u> Mnega</u> Deadtime reduce with the tdc 260SPIROC2b TDC 00m integrated in spiroc2c 2400 2200 2000 1800 1600 1400 1200 1000 100200300400 500 Delay [ns] SPIROC2c -6.592 µs Trigger Tbase CIDE DSQ AC1M 200 ns/div Normal 1.560 V 200 mV/div 5.0 GS/s Edge 10.0 kS Positive -1.5780 \ 2.326 \ 852 mV 1.474 V

### SPIROC 2c: Zero event bug

#### SPIROC2C: New Delay box