# Outer Silicon Mechanical Status

#### Bill Cooper Fermilab

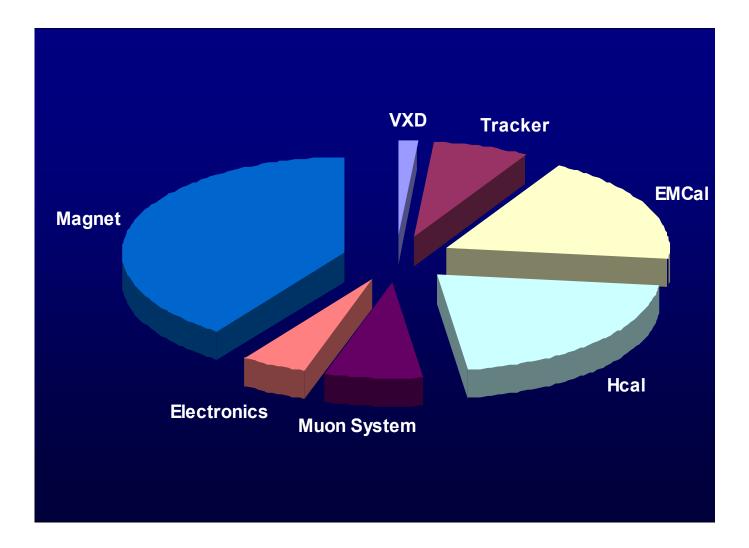

#### Cost by Subsystem

### Outline

- Review of design, with emphasis on areas needing attention

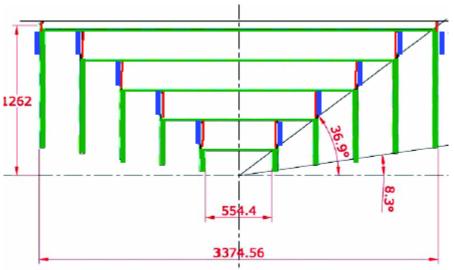

- Overall layout of outer and inner silicon

- Outer silicon layout

- Provisions for servicing inner silicon

- Module design (from Tim Nelson)

- Remaining, near-term work

- Summary

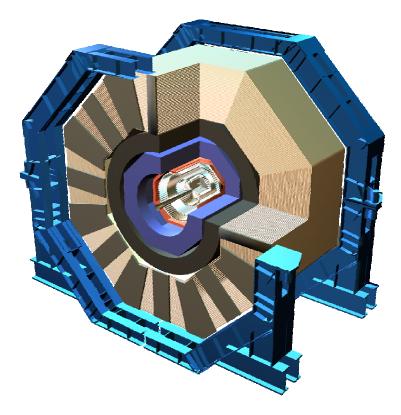

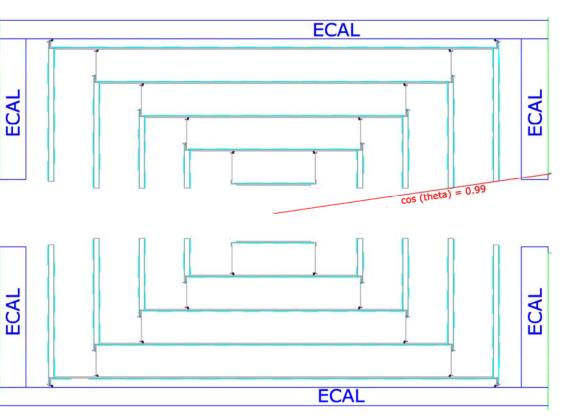

### Vertexing and Tracking

- Conceived and optimized as an integrated detector

- Inner tracking (Vertex detector)

- Central tracking

- Forward tracking

- EM calorimeter

- 5 T solenoidal field

- Outer silicon

- 5 axial barrel layers

- 5 double-layer disks per end

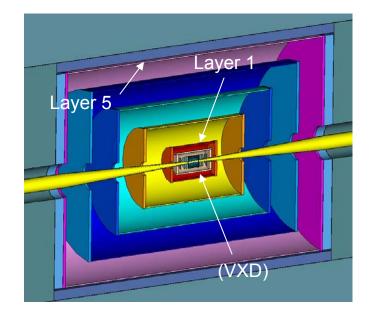

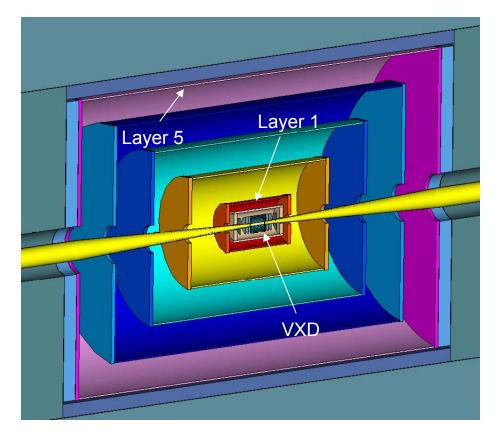

### Silicon Detector Layout

- Outer tracker (microstrips)

- OR = 1.25 m

- IR = 0.2 m

- May need to adjust inner radius to match beam-line elements

- In barrels, knowledge of Z comes from the inner detector and the location of the sensor in which a hit occurred.

- Supported from ECAL

- Inner detector (pixels)

- VXD

- 5 barrel layers (may increase to 6)

- 4 disks per end

- Additional "forward" disks

- Supported from conical portions of beam pipe

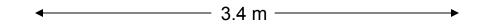

### **Outer Silicon Layout**

- Drawing features awaiting update:

- Detailed geometry of modules, including module mounts

- Details of disk and barrel overlaps

- Inner radii of disks

- Barrel foam thickness

- Disk foam thickness

- Paths and handling mechanisms for readout cables and fibers

- Provisions for distributing dry gas flow

- Details of ECAL inner surface

- Reproducible, rolling support from ECAL

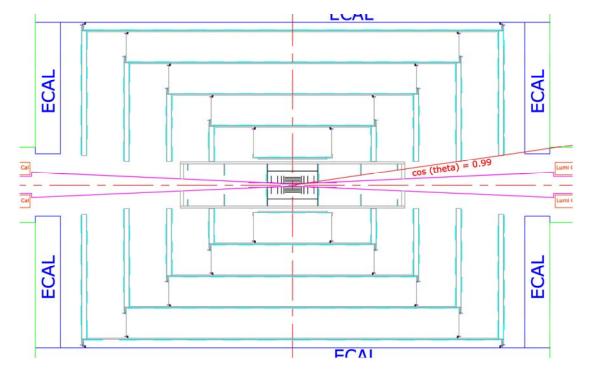

#### Detector Open with Full Access to Inner Detector

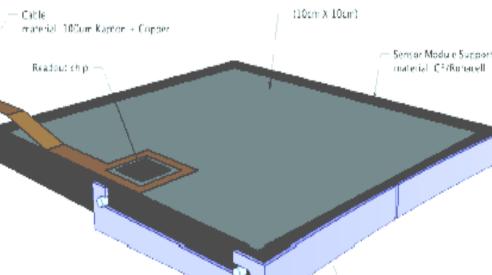

## Outer Tracker as Modeled in SiD<sub>00</sub>

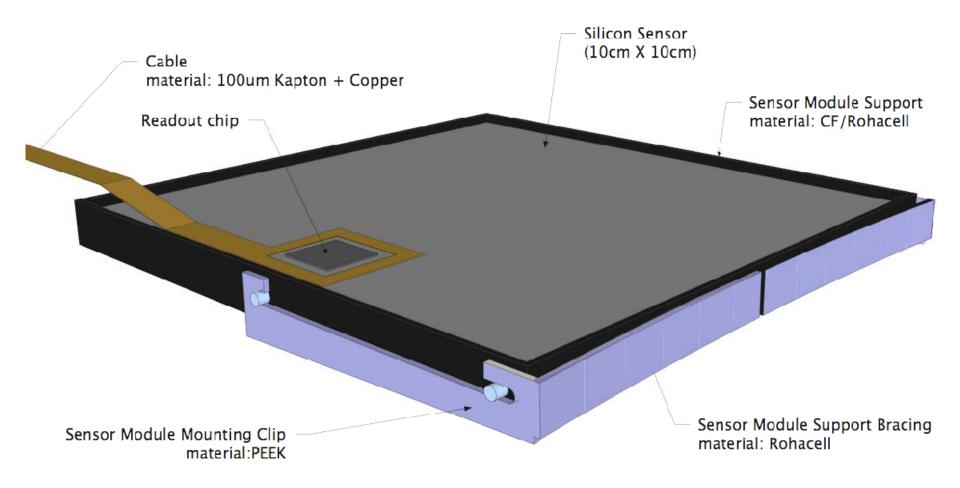

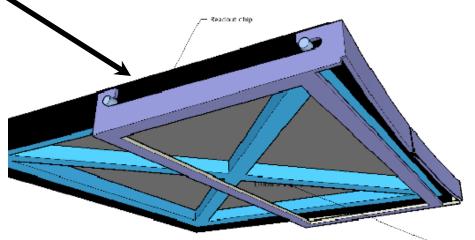

- Closed CF/Rohacell cylinders

- •Nested support via annular rings

- Power/readout motherboard mounted on support rings

- Bus cables connect single-sensor modules to motherboards

- •Cylinders tiled with 10x10cm sensors with readout chip

- ·Single sided ( $\phi$ ) in barrel

- $\cdot R$ ,  $\phi$  in disks

- Modules mainly silicon with minimal support (0.8% X<sub>0</sub>)

- ·Overlap in  $\phi$  and  $\boldsymbol{Z}$

- T. K. Nelson, SLAC

Sensor Module Mounting Clip

Bill Cooper

Sensor Module Support Bracing

SiD Meeting – 16 December 2005

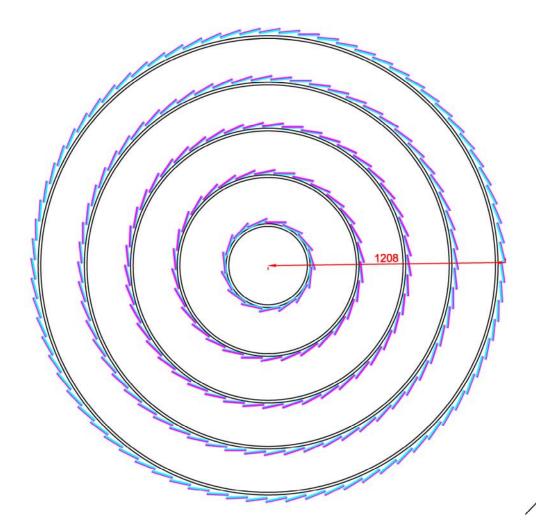

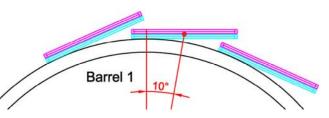

### • Duter Barrels with a Single Type of Module

Sensors: Cut dim's: 104.44 W x 84 L Active dim's: 102.4 W x 81.96 L Boxes: Outer dim's: 107.44 W x 87 L x 4 H Support cylinders: OR: 213.5, 462.5, 700, 935, 1170 Number of phi: 15, 30, 45, 60, 75 Central tilt angle: 10 degrees Sensor phi overlap (mm): Barrel 1: 5.3 Barrel 2: 0.57 Barrel 3: 0.40 Barrel 4: 0.55 Barrel 5: 0.63 Cyan and magenta sensors and boxes are assumed to be at different Z's and to overlap in Z. Within a given barrel, cyan sensors overlap in phi as do magneta sensors.

Overlap of modules

0.025 mm strip pitch, 0.050 mm readout pitch

Bill Cooper

SiD Meeting – 16 December 2005

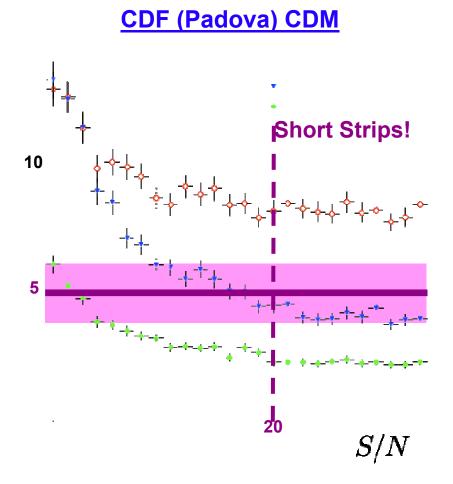

- A primary advantage of support cylinders: they enable very short modules

- Short modules are nice because they...

- have high S/N

- provide *z* information for pattern recognition

- can be universal and are easy to assemble, install and replace

- Downside? Lots of readout... is mass a problem?

- Sensor material and support material are similar and relatively insensitive to module length.

- The most massive components in large silicon trackers are those that support the readout:

- hybrid electronic boards

- cooling

- cables

The readout chip is the key: take advantage of ILC machine timing to design a chip that eliminates/minimizes these.

#### **Barrel Module Design**

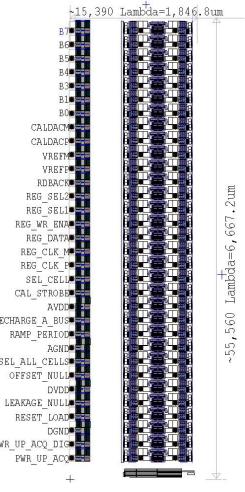

- Tracker variant of chip developed at SLAC for SiW ECAL

- no hybrid: the chip bump bonds directly to silicon

- digital section quiet during entire train: only activity is synchronous clock

- pulsed power eliminates need for active cooling

- 4 buffers/channel with beam-crossing stamp preserves event identity for reconstruction

### **KPiX-T Readout Chip**

- First submission (2X32 array) should arrive at SLAC any day

- Will test with silicon by wirebonding to spare CDF Layer 00 sensors

- If successful, hope to submit full-scale version as the next step.

### Module Implications for Sensors

- Must develop bump-bondable silicon microstrip sensors

- Double-metal:

- used to route signals to bonding array

- used as via between cable and chip for power and control

- Conceptual design and development of specs underway... time to initiate discussion with HPK for production of prototypes

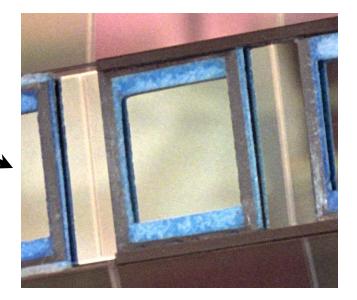

#### Sensor Support

- CF-composite frame with Rohacell cross-bracing based upon similar frames used for CDF ISL

- Frames clip into mounts on support cylinders

- Investigating CF-filled injection-molded PEEK for mounts and possibly also support frames: there is a major advantage to making these components massproducible

#### **Barrel Cables**

- Many cables in short-module tracker, important to minimize material:

- Pulsed-power scheme can accept 1 ohm for power+return

- Only six other lines needed for control

- Using 1/4 oz. copper on 100 micron Kapton, cables are ~5mm wide: copper covers less than 1/2 of area

- Each module has a short (~10cm) "pigtail" that bonds directly to the sensor: rather complicated but small

- Pigtail connects to longer cable that extends to power/data concentrator boards: rather long but simple

- No showstoppers expected, but must produce detailed design for fabrication of prototypes

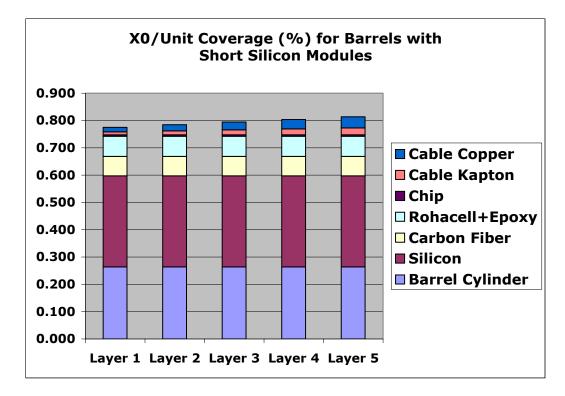

#### **Barrel Tracker Material**

- Total is ~0.8% X<sub>0</sub>, roughly equal parts silicon and support

- Readout material is negligible by comparison, <0.1% X<sub>0</sub> in all layers

#### **Expected Performance**

- Capacitance should be ≈15pf

- S/N ≈ 20

- Profit enormously from floating intermediate strips (50/25 µm)

- $\Rightarrow \sigma_{hit} \approx 5 \mu m$

- Could consider thinner silicon if deemed advantageous

Outer Silicon Disks (1)

- All elements of the concept carry over to modules for the forward disk, be they wedges, squares or hexagons.

- Modules can trivially be made double-sided using single-sided silicon on both sides of support: doubles silicon and readout material

- If there is real interest in using double-sided silicon in the forward disks, some changes will be necessary.

- Not much additional thought going into forward modules until simulation points to a particular tiling scheme.

### Outer Silicon Disks (2)

Overall layouts which take into account module design, tiling, mounts, overlaps, and paths for services will be updated once a tiling arrangement has been selected.

- Potential overall layouts may help with tiling selection.

# Remaining Work (1)

- Barrel sensors

- Number of varieties

- Signal to noise (has been estimated for single-sensor modules)

- Sensor dimensions

- Phi and longitudinal overlaps

- Effective thickness, including mounting and readout

- Overall geometric arrangement

- Barrel power (per unit area and per barrel)

#### Disk sensors

- Number of varieties

- Signal to noise

- Sensor dimensions

- Phi and radial overlaps

- Effective thickness, including mounting and readout

- Overall geometric arrangement

- Disk power (per unit area and per disk)

Remaining Work (2)

- Support cylinders and disks

- Optimum foam thickness

- Optimum wall thickness

- Portions of foam and wall that can be removed

- Mechanical connection details

- Modules to barrels and disks

- Barrel to barrel annular rings

- Readout motherboards to annular rings

- Outer barrel to ECAL

- Cooling

- Flow paths

- Calculations of heat transfer rates versus flow

- Analysis of the potential for vibrations

### Summary

- The overall design has been updated to more realistically address servicing.

- The overall design allows a clean separation between outer detector and inner detector elements.

- Single-sensor module designs have been developed by SLAC (T. K. Nelson).

- Portions of design work await guidance from simulations.

- We do have enough information to proceed with design efforts in many areas.