# VXD and intermediate tracking Integration Status

A. Ishikawa, M. Vos, A. Besson

- News from R&D groups

- Beam background updates

- Costing

- Power consumption

- Cabling

- SIT

- Conclusion

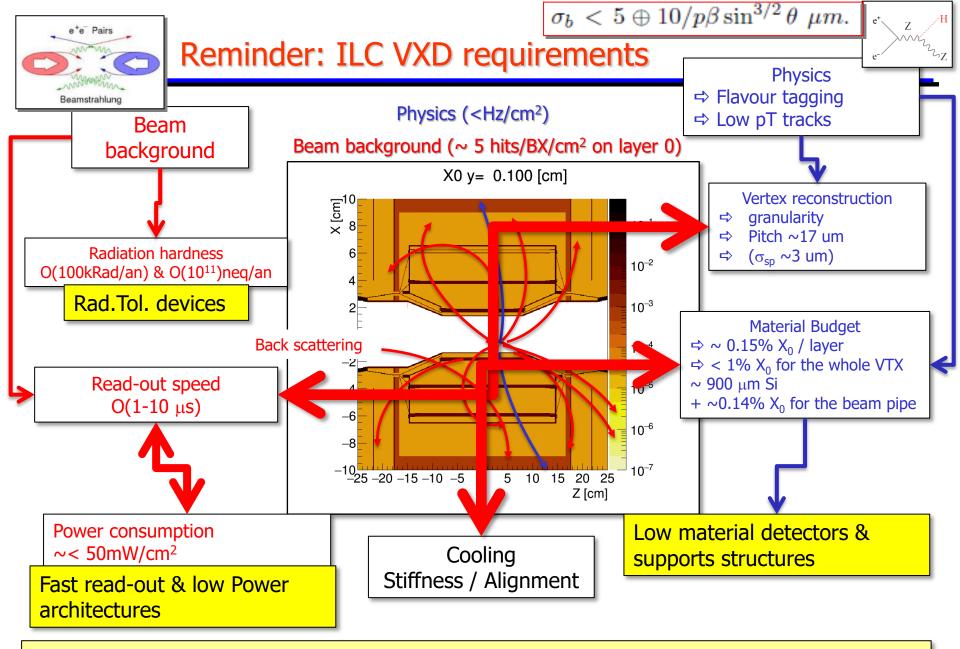

#### Challenge : meet the requirements all together

ILD Integration, Feb. 2019

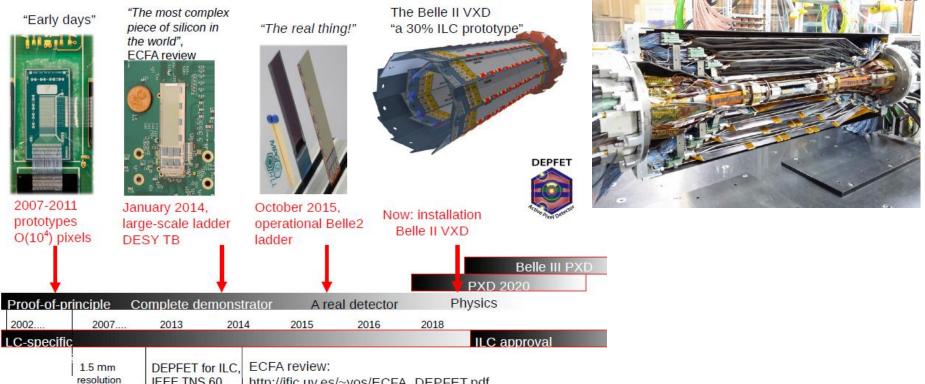

# News from DEPFET

#### **One-slide DEPFET history**

- IEEE TNS 60 http://ific.uv.es/~vos/ECFA\_DEPFET.pdf

- Real experience gained for Belle II

- Installation of vertex detector and preparation of PXD2020

- ILC-specific activity has been 2nd priority

- Approval required to for signficant renewed interest

- · Thinking about Belle III has started

- Advanced DEPFET and CMOS options pursued by the collaboration

ILD Integration, Feb. 2019

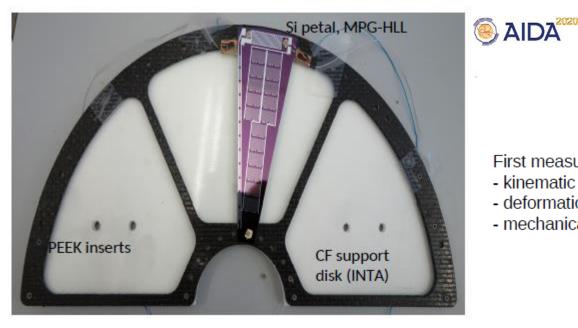

# News from Forward disks

- A new mock up is being built (FTD1 & 2)

- Thermo-mechanical properties

- Planarity

Mock-up for FTD1 and 2 is being assembled at IFIC

New production at silicon lab of the Max Planck society in Munich

Petals arrived at IFIC in September 2018 and are currently being mounted on mock-up structure

First measurements look promising:

- kinematic mount absorb thermal expansion as expected

- deformations under power load and air-flow are O(5  $\mu m)$

- mechanical stability in stable conditions is much better

ILD Integration, Feb. 2019

# **News from CMOS Pixel Sensors**

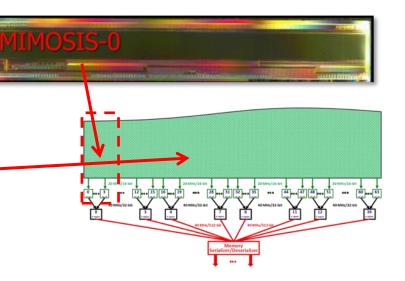

- MIMOSIS-0 prototype (2018)

- 1<sup>st</sup> prototype for CBM experiment @ FAIR

- Design adaptable to ILD

- Ongoing tests

- > Pixel dispersion, architecture

- > Radiation hardness tests ongoing ( $10^{14} n_{eq}/cm^2 \& 20 Mrad$ )

- MIMOSIS-1 (2019) -

- Full scale

- Ongoing design

- CREMLINplus program (EU + Russia)

- with DESY, CERN, JINR, FAIR, BINP, KINR, Frankfurt & IPHC

- Telescope with MIMOSIS 1 or 2

- > Double sided ladders & faster read-out time 100  $\mu$ s -> 5  $\mu$ s. w.r.t to Mimosa 26 (EUDET)

- > Slightly degraded resolution compensated by double sided

- Long term R&D (with CERN)

- Stitching -> reduce ladder overlap / reduce space between sensors

- $\succ~~\sim150~\mu m$  to  $\sim\!<\!50~\mu m$

- Synergy with ALICE plans

- 65 nm technology exploration

- Mixed CMOS processes

# Extension of MIMOSIS to ILC vertexing and tracking

⇒ PSIRA

#### Conservative approach

Minimize changes w.r.t. MIMOSIS

$\succ$  Keep TJ 0.18  $\mu$ m technology & a similar architecture

- 2 sub-systems targeted

- Vertex detector & Silicon inner trackers (SIT @ ILD)

#### ⇒ Finalize CPS ~2025

#### • Expected Performances

- −  $\sigma_{sp}$  ~4 µm ⇒Use double sided ⇒  $\sigma_{sp}$  ~2.8 µm

- > 22x22  $\mu$ m<sup>2</sup>  $\sim$  20% better spatial resolution % ALPIDE (vertexing)

- Faster = higher Power consumption

- Read-out time: 2-4  $\mu$ s (ILD-VXD) and 1  $\mu$ s (ILD-SIT)

- Single pixel address read-out = 50 ns

- ➤ (with 20 MHz clock)

- Sustainable occupancy (~5 pixels/hits)

- $> \sim 4$  hits/region/µs  $\sim 100$  hits/cm<sup>2</sup>/µs

| PSIBA                                                 | Matrix (512 x 1024)     | Pixel: 22 x 22 µm <sup>3</sup><br>ion 1<br>512 phels<br>Pixel<br>Pixel<br>Pixel | n2 Region 3 Region 64                                       |

|-------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|

| Bias DACs<br>Pixel Config.<br>Management<br>Registers | PE Driving & Cluster Fi | nding & Region RO 1 R RO                                                        | 2 RRO3 RRO64                                                |

| CMU<br>Costrol Man agement Unit<br>12C                | Sequencer               | Data Formatting                                                                 | Two options;<br>1. Continuous readout<br>2. Delayed readout |

|                                                       | 40 MHz                  | Serialiser (8b/10b7)                                                            | Pad Ring                                                    |

- Can one reach : Pitch ~ 18 x 18  $\mu$ m ( $\sigma_{sp}$  ~ 3  $\mu$ m) & r.o.time ~ 2-4  $\mu$ s ? – Doable with smaller feature sizes

- ⇒ PSIRA architecture already reaching 4-8 BX read-out time

- ⇒ Power vs read-out speed compromise

- ⇒ Avoiding power pulsing possible ?

#### Beam background

#### Beam background updates effects

Total VXD hits/BX

01m250\_DBD\_fieldX02

02m500 DBD fieldX02

NEW SIMULATIONS

LARGE, anti-DID 72\_BEAMLIMITS\_15v05\_250A

LARGE, no anti-DID 71\_BEAMLIMITS\_15v03\_250A

73 BEAMLIMITS3 15v05 250A

74\_BEAMLIMITS2\_s5v03\_250A

75\_BEAMLIMITS\_s5v05\_250A

76\_BEAMLIMITS2\_s5v05\_250A

$\sqrt{s} = 500 \text{ GeV}$ :

43\_akiya\_15\_500TDR

LARGE, anti-DID, lower momentum threshold

SMALL, no anti-DID, smaller maximum step length

LARGE, anti-DID, intermediate result, for illustration,

SMALL, anti-DID, smaller maximum step length

SMALL, anti-DID, new 250 GeV params

DBD

L12 EARLY

662.80

1276.50

1040.11

1050.50

970.11

827.67

738.40

713.89

1344.70

with new 250 GeV beam params

L12 LATE

34.00

126.50

1233.44

339.70

308.44

1386.00

401.20

420.00

579.50

• D. Jeans and Akiya beam background studies:

| Large, 250 new params, anti-DID<br>[I believe: (mean #hits/BX +/- bunch-by-bunch variation)                                                                                                         |                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Subsystem : VXD<br>Layer 1: 7292 hits. hitsperBX = (810.2 +- 339.) hits/BX. (5.89 +- 2.471) hits/cm^2/BX.<br>Layer 2: 4215 hits. hitsperBX = (468.3 +- 204.) hits/BX. (3.40 +- 1.488) hits/cm^2/BX. |                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Layer 3: 906 hits.<br>Layer 4: 746 hits.<br>Layer 5: 279 hits.<br>Layer 6: 266 hits.                                                                                                                | hitsperBX = (100.6 +- 57.4) hits/BX. (0.16 +- 0.094) hits/cm^2/BX.<br>hitsperBX = (82.88 +- 47.2) hits/BX. (0.13 +- 0.078) hits/cm^2/BX.<br>hitsperBX = (31 +- 17.1) hits/BX. (0.03 +- 0.018) hits/cm^2/BX.<br>hitsperBX = (29.56 +- 16.6) hits/BX. (0.03 +- 0.017) hits/cm^2/BX. |  |  |  |  |  |  |  |  |  |

- Now backscattered particles ~ 50-55% of total background (without antiDID)

- Anti-DID effect

- Reduces only backscattered particles rate

- ~ -35% reduction on total background

- Small geometry: small B field effect

- The safety margin for data flow/band width/power estimates: ~ 3-5

- Percent level occupancy can be reached

- E.g.: safety factor of 5, BX ~500 ns, pitch ~22um, read-out time ~ 4 us, cluster multiplicity ~5

⇒ Background (DBD@500GeV) ~ Background(@250GeV with new L\*, new lumi, with A-DID, bug corrected)

⇒ Anti-DID effect significant now but moderate.

⇒Large uncertainties remains (+bunch-by-bunch variations)

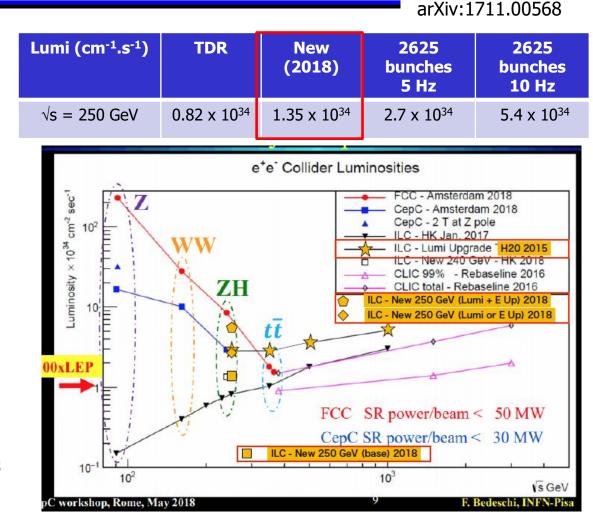

# Luminosity options and beam background

- Luminosity  $\propto (\delta_{bs})^{1/2}$ - affordable @ 250 GeV

- ⇒ significant effect on #hits/BX

- 2 other options

- # bunches: 1312 ⇒ 2625

- − Repetition rate: 5 ⇒ 10 trains

⇒ no effect on #hits/BX

$\Rightarrow$  no effect on #hits/read-out if bunch time spacing remains the same (~ 500 ns)

$\Rightarrow$  significant effect (x4) on data flow per second.

ILD Integration, Feb. 2019

#### Data flux (New Background estimates @ $\sqrt{s}$ = 250 GeV)

| Layer | DBD<br>occupancy<br>(hits/cm²/BX) | Detector<br>surface<br>(mm²)                        | #hits/BX | #hits/read<br>out             | #hits/train                           | # hits/s                 | Data rate<br>(Mbits/train)                                                        | Data rate<br>(Mbits/s)                                                            | Data rate<br>(Mbits/train)<br>With safety<br>factor of 3                          | Data rate<br>(Mbits/s)<br>With safety<br>factor of 3                              |

|-------|-----------------------------------|-----------------------------------------------------|----------|-------------------------------|---------------------------------------|--------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|       | @ √s<br>= 250 GeV                 | Length<br>x width<br>x # ladders                    |          | assuming<br>4 μs<br>i.e. 8 BX | Assuming<br>1312 bunches<br>per train | Assuming<br>5 trains / s | Assuming<br>16 bits/pixel<br>& 5 pixels/hit<br>& 10 bits header<br>= 100 bits/hit | Assuming<br>16 bits/pixel<br>& 5 pixels/hit<br>& 10 bits header<br>= 100 bits/hit | Assuming<br>16 bits/pixel<br>& 5 pixels/hit<br>& 10 bits header<br>= 100 bits/hit | Assuming<br>16 bits/pixel<br>& 5 pixels/hit<br>& 10 bits header<br>= 100 bits/hit |

| 0     | 5.89±2.47                         | 125 x 11 x 10<br>= 13 750                           | 810      | 6480                          | 1062 K                                | 5 314 K                  | 106                                                                               | 530                                                                               | 318                                                                               | 1590                                                                              |

| 1     | 3.40± 1.49                        | 125 x 11 x 10<br>= 13 750                           | 470      | 3760                          | 616 K                                 | 3 083 K                  | 62                                                                                | 310                                                                               | 186                                                                               | 930                                                                               |

| 2     | 0.16±0.09                         | 125 x 2 x 2.2<br>x 11<br>=60 500                    | 97       | 776                           | 127 К                                 | 636 K                    | 13                                                                                | 65                                                                                | 39                                                                                | 195                                                                               |

| 3     | 0.13±0.08                         | 125 x 2 x 2.2<br>x 11<br>=60 500                    | 79       | 632                           | 104 К                                 | 518 K                    | 10                                                                                | 50                                                                                | 30                                                                                | 150                                                                               |

| 4     | $0.03\pm0.02$                     | 125 x 2 x 2.2<br>x 17<br>=99 000                    | 30       | 240                           | 39 K                                  | 197 K                    | 4                                                                                 | 20                                                                                | 12                                                                                | 60                                                                                |

| 5     | $0.03\pm0.02$                     | 125 x 2 x 2.2<br>x 17<br>=99 000                    | 30       | 240                           | 39 K                                  | 197 K                    | 4                                                                                 | 20                                                                                | 12                                                                                | 60                                                                                |

| TOTAL |                                   | 346 100<br>mm <sup>2</sup><br>~ 0.35 m <sup>2</sup> | 1516     | 12128                         | 1 989 K                               | 9 945 K                  | 200                                                                               | 1 000                                                                             | 600                                                                               | 3 000                                                                             |

- average raw data size per BX, event or train. (with or without safety factor on beam background included) Average size per BX : ~0.15 Mbits / BX ⇒ 0.45 Mbits / BX (with safety factor of 3) Average size per event (~8 BX) : ~1.2 Mbits/ readout ⇒ 3.6 Mbits / readout (with safety factor of 3) Average size per train : ~200 Mbits / train ⇒ 600 Mbits / train (with safety factor of 3) Average size per second: ~1000 Mbits / train ⇒ 3000 Mbits / second (with safety factor of 3)

# Costing

#### Cost estimates and integration

- Added value:

- Opportunity to identify issues and to revisit the design

- Sources:

- STAR HFT, ALICE ITS upgrade and discussions with experts

- Assumptions

- No contingency added

- No R & D costs included

- Preproduction runs included

- Beam background and data flux staying below the estimated value x 5

- Assumed:

- ➤ 1 chip design for SIT

- > 2 chip designs for the VXD (might be 1 or 3)

- Chip Production yield (50%), Spares (20%)

- Some topics needs more detailed studies

- > (Faraday cage, installation, etc.)

- Uncertainties ~ 15 % (1 $\sigma$ )

- Evolution of the technology

- Beam background background

ILD VXD and SIT Costing Estimates

Auguste Besson<sup>1</sup>, Marc Winter<sup>1</sup> <sup>1</sup>IPHC-CNRS, Straalsourg University, France

January 28, 2019

Abstrast This note commanism the root estimation performs if the ILD Varies Desarter (VXD) and a filters inner Thadar (SIT) with an averand CMOS technology. This last estimate was framed for the IDI (1). Thus estimation are based in our timised laweldegs at the time ing and in our indust maningary case. Owned, The final miniber should be considered that assuming it for other of a DIV.

#### Acronymes

- CPS = CMOS Pixel Sensors

- MIMOSIS = Family of chips being developped for CBM-MVD detector

- ULTIMATE 2 = Chip which equipped the STAIL HFT detector.

ALPIDE = chip developed to equip ALICE-ITS spende detector.

- ALPIDE = thip developped to equip ALICE-ITS apgrade detection.

PSIRA = Family of chip proposed to equip the VXD.

- VXD = H.D Vertex Detector.

- SIT = Silicon Inner Tracker

ILD = International Larger Determined

#### 1 Introduction

1.1 General remarks

• In the whole document, the unit used is the KalkGaron (KRUR). Most randown spin or extra tabilismi from order experiment and project aships which was the first end-norm physics experiments with (RCH). The first using which was the first end-norm physics experiments with (RCF) at the random physics and the 2004. The second one is the ALICE TTS approximation (RCF) at the random physics and which will be experipsed with ALICE there is a first end-normalized matching the approximation of the ALICE TTS approximation (RCF) end-normalized matching the experipsed with ALICE there is a first end-normalized matching the approximation of the approximation of

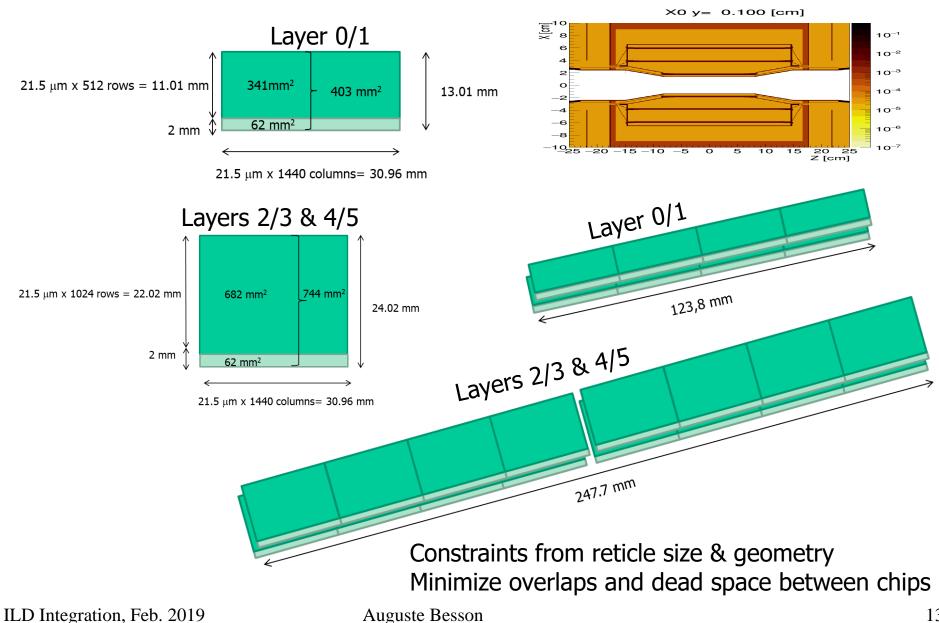

# Chip dimensions & ladders

### VXD dimensions

| Figures per layers                           |           |       |               |       |               |        |  |  |  |

|----------------------------------------------|-----------|-------|---------------|-------|---------------|--------|--|--|--|

| Layer                                        | 0         | 1     | 2             | 3     | 4             | 5      |  |  |  |

| Layer Radius $(mm)$                          | 16        | 18    | 37            | 39    | 58            | 60     |  |  |  |

| Layer $ z max \ (mm)$                        | 61.9      | 61.9  | 123.8         | 123.8 | 123.8         | 123.8  |  |  |  |

| Chip Pixel Number in X                       | 1440      | 1440  | 1440          | 1440  | 1440          | 1440   |  |  |  |

| Chip Pixel Number in Y                       | 512       | 512   | 1024          | 1024  | 1024          | 1024   |  |  |  |

| Chip Pixel PitchX $(\mu m)$                  | 21.5      | 21.5  | 21.5          | 21.5  | 21.5          | 21.5   |  |  |  |

| Chip Pixel PitchY $(\mu m)$                  | 21.5      | 21.5  | 21.5          | 21.5  | 21.5          | 21.5   |  |  |  |

| Chip Dimension X $(mm)$ (sensitive area)     | 30.96     | 30.96 | 30.96         | 30.96 | 30.96         | 30.96  |  |  |  |

| Chip Dimension Y $(mm)$ (sensitive area)     | 11.01     | 11.01 | 22.02         | 22.02 | 22.02         | 22.02  |  |  |  |

| Chip Dimension Y $(mm)$ (non sensitive area) | 2.0       | 2.0   | 2.0           | 2.0   | 2.0           | 2.0    |  |  |  |

| Chip Surface $(mm^2)$ (sensitive area)       | 341       | 341   | 682           | 682   | 682           | 682    |  |  |  |

| Chip Surface $(mm^2)$ (non sensitive area)   | 62        | 62    | 62            | 62    | 62            | 62     |  |  |  |

| Chip Surface $(mm^2)$ (total)                | 403       | 403   | 744           | 744   | 744           | 744    |  |  |  |

| Ladder Length $(mm)$ (sensitive area)        | 123.8     | 123.8 | 123.8         | 123.8 | 123.8         | 123.8  |  |  |  |

| Ladder Width $(mm)$ (sensitive area)         | 11.01     | 11.01 | 22.02         | 22.02 | 22.02         | 22.02  |  |  |  |

| N chip per ladder on each side               | 4         | 4     | 4             | 4     | 4             | 4      |  |  |  |

| Layer Surface $(cm^2)$ (sensitive area)      | 136.3     | 136.3 | 599.7         | 599.7 | 926.9         | 926.9  |  |  |  |

| N Chips Per Layer                            | 40        | 40    | 88            | 88    | 136           | 136    |  |  |  |

| Total surface $(cm^2)$ (sensitive area)      |           |       | 34            | 84    |               |        |  |  |  |

| Figures per e                                | double la | ayers |               |       |               |        |  |  |  |

|                                              | Laye      | r 0/1 | Laye          | r 2/3 |               | r 4/5  |  |  |  |

| N Chips in $z$                               | 4         | 1     | 4 + 4         | 4 = 8 |               | 4 = 8  |  |  |  |

| N Ladders                                    | 1         | 0     | $2 \times 11$ | = 22  | $2 \times 17$ | 7 = 34 |  |  |  |

| N Chips Per double Layer                     | 8         | 0     | 17            | 76    | 27            | 72     |  |  |  |

| N Chips (per architecture)                   | 8         | 0     |               | 44    | 48            |        |  |  |  |

| N Total Chips                                |           |       | 52            | 28    |               |        |  |  |  |

ILD Integration, Feb. 2019

#### Costs Estimate

| More details            |  |

|-------------------------|--|

| in the costing document |  |

Detector surface  $(m^2)$

Chip surface  $(mm^2)$

# Chips mounted # Chips to produce

# Chips per wafer

# Wafers produced

# Chips produced

# Pixels

# Ladders

# Layers

# Chips per ladder

| to Estimatos (VVD)                                                |               |            |     |               |       | Domain |                                                      | Item           |                      | Materi:<br>Unit Cost |           | Manpower<br>Costs | Total<br>Costs | Notes    |      |

|-------------------------------------------------------------------|---------------|------------|-----|---------------|-------|--------|------------------------------------------------------|----------------|----------------------|----------------------|-----------|-------------------|----------------|----------|------|

| ts Estimates (VXD)                                                |               |            |     |               |       |        | Sensors                                              | _              | - · · · ·            |                      | omit Cost | 1152              | 100            | 1252     |      |

|                                                                   |               |            |     |               |       |        | Sensors                                              |                | Masks                |                      | 300       | 600               | 0              | 600      | ۵    |

|                                                                   |               |            |     |               |       |        |                                                      | b              | ank wafer            | s                    | 0.1       | 30                | 0              | 30       |      |

|                                                                   |               |            |     |               |       |        |                                                      | Qua            | ity Assura           | ance                 | 2.4       | 30                | 0              | 30       |      |

|                                                                   |               |            |     |               |       |        |                                                      | Waf            | er product           | tion                 | 3.2       | 192               | 0              | 192      | ь    |

|                                                                   |               |            |     |               |       |        |                                                      |                | Thining              |                      | 0.5       | 30                | 0              | 30       | c    |

| ••                                                                |               |            |     |               |       |        |                                                      |                | Dicing               |                      | 0.5       | 30                | 0              | 30       | e    |

| tails                                                             |               |            |     |               |       |        | Tests                                                | Pi             | obe statio           | n                    | 200       | 200               | 0              | 200      | d    |

|                                                                   |               |            |     |               |       |        |                                                      |                | Others               |                      |           | 40                | 100            | 140      | e    |

| sting do                                                          | ncume         | nt         |     |               |       |        | Mechanics<br>Ladders                                 | Mark           |                      |                      | 0.5       | 452               | 500            | 952      |      |

| Sung ut                                                           | Junic         | -110       |     |               | 1     |        | Ladders                                              | Mech           | anical sup<br>Gluing | oport                | 0.5       | 34<br>68          | 0              | 34<br>68 | t    |

|                                                                   |               |            |     | ND Y          |       |        |                                                      |                | Others               |                      | 1         | 0                 | 100            | 100      |      |

|                                                                   |               |            | 1   |               | •     |        | Mechanics                                            | Be sur         | port and o           | others               |           | 200               | 100            | 300      | g    |

|                                                                   | -             | <b>۸</b> ۸ | 11  |               |       |        |                                                      |                | ssembling            |                      |           | 50                | 200            | 250      | h    |

|                                                                   | -17           | 141        | 1   |               |       |        | Faraday cage                                         |                |                      |                      |           | 100               | 100            | 200      | g    |

| -                                                                 | トレ            |            |     |               |       |        | Electronics                                          |                |                      |                      |           | 486               | 400            | 886      |      |

| DH                                                                | vert terme    |            |     |               |       |        | Flex cable                                           | С              | onstruction          | n                    | 0.7       | 140               | 100            | 240      | j    |

| <b>~ ~ </b>                                                       | -             |            |     |               |       |        |                                                      |                | Gluing               |                      |           | 100               | 50             | 150      | ď    |

| -                                                                 |               |            |     |               |       |        |                                                      |                | Bonding              |                      |           | 80                | 20             | 100      | ď    |

|                                                                   |               |            |     |               |       |        | Read-out                                             | 0              | Tests                |                      | 0.3       | 0<br>24           | 30<br>0        | 30<br>24 | 1    |

|                                                                   |               |            |     |               |       |        |                                                      |                | otical cable         |                      |           | 24                | 0              | 24 20    | -    |

|                                                                   | ]             | LD V       | /XD |               | ILD   | ALICE  | STAR                                                 | ITS/VY         | XD Ľ                 | TS/SIT               | note      |                   | 0              | 20       |      |

|                                                                   | L0-L1         | L2-1       | L5  | total         | SIT   | ITS    | HFT                                                  | ratio          |                      | ratio                |           | -                 | 100            | 100      |      |

| urface $(m^2)$                                                    | $\simeq 0.03$ | $\simeq 0$ |     | $\simeq 0.35$ | 7     | 10     | 0.16                                                 | 30             |                      | 1.5                  |           | 2                 | 100            | 182      | i    |

|                                                                   |               |            |     | $\simeq 0.55$ |       |        |                                                      | 30             |                      |                      |           | D                 | 0              | 20       |      |

| ace $(mm^2)$                                                      | 403           | 74         | 4   | -             | 735   | 450    | 459                                                  | $\simeq 1$     |                      | $\simeq 1$           |           | 0                 | 250            | 1020     |      |

| mounted                                                           | 80            | 44         | 8   | 528           | 9000  | 24500  | 400                                                  | 45             |                      | 2.5                  | a         | D                 | 20             | 100      | i    |

|                                                                   |               |            |     |               |       |        |                                                      |                |                      |                      | ь         | - 5               | 25<br>5        | 50<br>20 |      |

| to produce                                                        | 192           | 107        |     | 1267          | 21600 | 58800  | 1920                                                 | 45             |                      | 2.5                  |           |                   | 50             | 350      |      |

| per wafer                                                         | 45            | 22         | 2   | -             | 22    | 45     | $\simeq 50$                                          |                |                      |                      |           | 0                 | 0              | 50       |      |

| s produced                                                        | 12            | 48         | 2   | 60            | 1000  | 1300   | $\simeq >75$                                         |                |                      |                      | cd        | 0                 | 0              | 150      |      |

| *                                                                 |               |            |     |               |       |        |                                                      |                |                      |                      |           | 0                 | 50             | 100      |      |

| produced                                                          | 540           | 105        | 56  | 1596          | 22000 | 58800  | 3600                                                 |                |                      |                      |           | 0                 | 100            | 200      |      |

| ixels                                                             | 60M           | 660        | M   | 720M          | 8.2G  | 13G    | 360M                                                 |                |                      |                      |           | 0                 | 200            | 300      |      |

| adders                                                            | 10            | 56         |     | 66            | 280 ? | 192    | 40                                                   |                |                      |                      |           | D                 | 200            | 250      |      |

|                                                                   |               |            |     |               |       |        |                                                      |                |                      |                      |           | 0                 | 0              | 50       |      |

| ayers                                                             | 2             | 4          |     | 6             | 4     | 7      | 2                                                    |                |                      |                      |           | 60                | 1450           | 4410     |      |

| per ladder                                                        | 8             | 8          |     | -             | 24/42 | е      | 10                                                   |                |                      |                      | f         |                   |                |          |      |

|                                                                   |               |            |     |               |       |        | Assumed 2 eng<br>212 (inner) + 48<br>High unit costs | 8 (outer) wafe |                      |                      |           |                   |                |          |      |

| С                                                                 | ost           |            | Se  | ensors        | Mec   | hanics | Eletr                                                | onics          | Ser                  | vices                | Ins       | stall             | ation          | T        | otal |

| $\frac{1152}{\text{Material}} \frac{1152}{1152} \frac{452}{1152}$ |               |            | 52  | 48            | 86    | 7      | 70                                                   |                | 10                   | 0                    | 29        | 960               |                |          |      |

|                                                                   | power         |            |     | 100           |       | 500    | 40                                                   |                |                      | 250                  |           | 20                |                |          | 450  |

|                                                                   |               | R)         |     | 1252          |       | )52    | 88                                                   |                |                      | 020                  |           | 300               |                |          | 410  |

| TOTAL (kEUR) $1252$ 952                                           |               |            |     |               | 04    | 000    |                                                      | 1020           |                      |                      | 00        | 0                 | -1.            | 110      |      |

ILD Integration, Feb. 2019

Detector

VXD

Auguste Besson

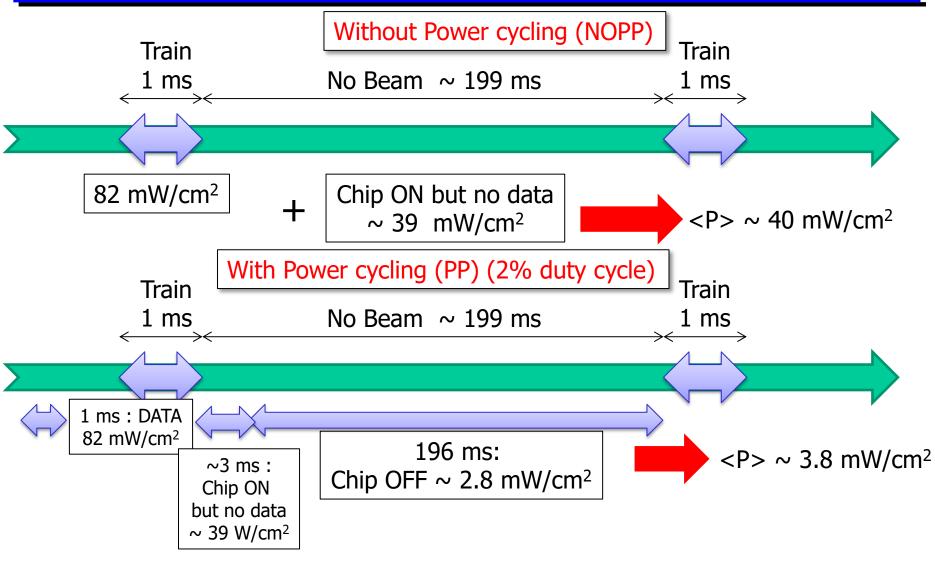

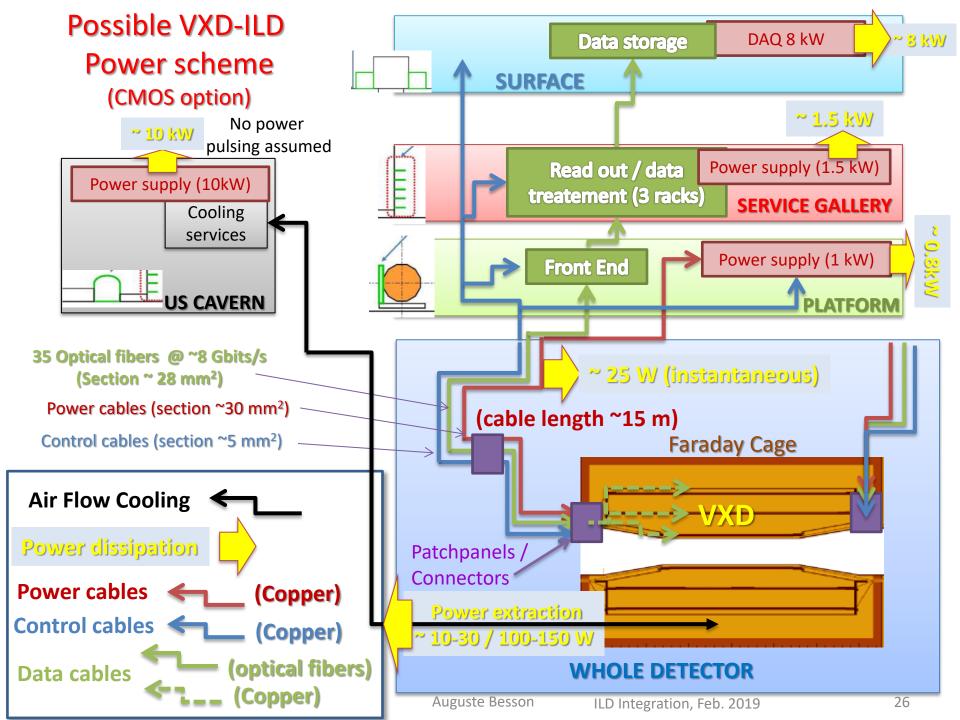

#### Power estimates

# Power scheme for VTX-ILD (inner layer)

Hypothesis: 3 double sided layers (3483 cm<sup>2</sup>), PSIRA architecture (4  $\mu$ s / 4  $\mu$ m), DBD background @  $\sqrt{s} = 500$  GeV, no safety factor ILD Integration, Feb. 2019 Auguste Besson

|     | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | : Results                       |                | Power Analog $(mW/chip)$ Power Bias $(mW/chip)$ Power PriorityEncoder $(mW/chip)$ Power DigitalPeriphery $(mW/chip)$ |                                                               |        |                      |                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|----------------------|-----------------|

| •   | Chip read-out speed<br>– 2 ms - 4 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 | Po             | Power PLL ( <i>i</i><br>wer Serializer With<br>er Serializer With M<br>Power LVDS (                                  | <i>nW/chip)</i><br>Data ( <i>mW</i> )<br>No Data ( <i>m</i> ) | //chip |                      | 3.5<br>.06<br>) |

| •   | Power pulsing <ul> <li>Power ON, no beau</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | am during 1-3 ms                |                | Period                                                                                                               | F                                                             |        | ve Energy            | Ľ               |

|     | <ul> <li>Leading param</li> <li>Power OFF: 10-30</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | neter With NO P.P.<br>D mW/chip | E be           | E during train<br>tween train (Power                                                                                 | ON)                                                           |        | mJ ~ 4 %<br>mJ ~ 6 % |                 |

| •   | Leading paramodeling paramod |                                 | E bet          | E between train (Power OFF) 5740 mJ ~ 9                                                                              |                                                               |        |                      |                 |

|     | <ul><li>Lower occupancy</li><li>Power is dominat</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |                | Layers                                                                                                               | Relative<br>Power                                             |        |                      |                 |

| •   | Beam background r<br>– DBD – DBD x 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |                | Layers 0/1                                                                                                           | ~ 10 %                                                        |        |                      |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                | Layers 2/3                                                                                                           | ~ 35%                                                         |        |                      |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                | Layers 4/5                                                                                                           | ~ 55 %                                                        |        |                      |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Beam background rate            | Read-out speed | <power (no="" p.p.)<="" th=""><th>) <pc< th=""><th>ower&gt;</th><th>(P.P.)</th><th></th></pc<></th></power>          | ) <pc< th=""><th>ower&gt;</th><th>(P.P.)</th><th></th></pc<>  | ower>  | (P.P.)               |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 | (μS)           | (W)                                                                                                                  | Conserv                                                       | ative  | Ambitious            |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DBD                             | 4 μs           | 102 W                                                                                                                |                                                               |        |                      |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DBD                             | 2 μs           | 122 W                                                                                                                |                                                               |        | 10.11/               |                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4 μs                            | 107 W          | 7 W ~31 W                                                                                                            |                                                               | ~12 W  |                      |                 |

| ILD | Integration, Feb. 2019                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DBD x 2                         | 2 μs           | 127 W                                                                                                                |                                                               |        |                      | 18              |

#### **Power consumption**

• Power estimates: Relatively robust when playing with different parameters

> 100-130 W range with NOPP, 10-30 W range with PP (uncertainties to be reduced with MIMOSIS)

- Valid for this architecture only.

- Air Cooling:

- STAR HFT demonstrated that 23°C air flow cooling @  $\sim$  10 m/s could extract up to  $\sim$  150 mW / cm<sup>2</sup> ( $\sim$ 350 W in total)

The STAR MAPS-based PiXeL Detector NIM, A 907 (2018) 60-80

Caveat: 15 cm diameter flexible ducts was used (not possible for ILD)

- Margin of improvement:

- Optimize each layer ?

- Smaller feature size ⇒ lower digital Power

#### **Cabling discussion**

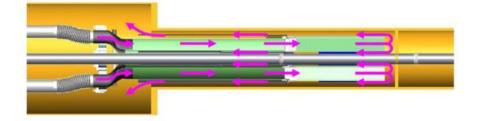

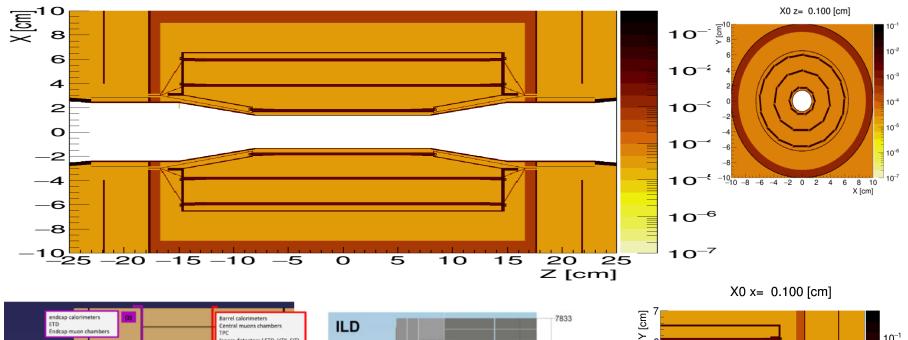

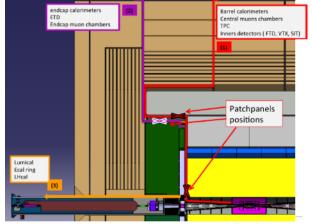

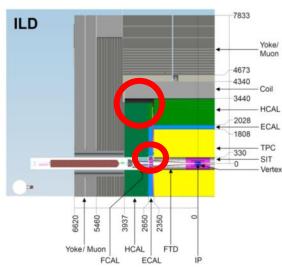

#### Read-out scheme: connectors/patchpanels

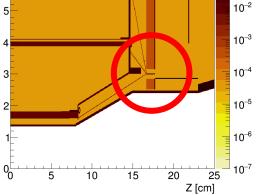

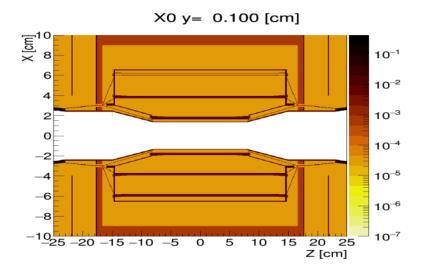

X0 y = 0.100 [cm]

C. Clerc et al. (2009)

ILD Integration, Feb. 2019

Auguste Besson

$10^{-1}$

ILD Integration, Feb. 2019

#### Architecture assumed

• Direct translation of MIMOSIS (for CBM) design adapted to ILD

- What will/may change in the future

- R & D towards faster read-out

- Feature size technology

- Stitching capabilities

- Material budget optimization

- What still needs to be studied more extensively

- Cooling

- Mechanics

- DAQ

# Data encoding & rates (assuming 4 µs read-out time)

- Beam background hits (new lumi @  $\sqrt{s} = 250$  GeV); no safety factor.

- Total number of hits/read-out

- Layer 0+1: ~ 12 000 hits

- Layer 2+3: ~ 1400 hits

- Layer 4+5: ~ 500 hits

- Total hits (in 4 us) ~15 000 hits

- Data encoding:

- 16 bits/pixel x 5 pixels/cluster + trailers/headers ~ 100 bits/hit

- Instantaneous data flux (No safety factor !)

- Flux = 15 000 hits x 100 bits/hit / 4x10<sup>-6</sup> s ~ 375 Gbits/s

- Optical fibers (assuming ~8 Gbits/s as a standard)

- Ladders 0/1 -> 40 fibers

- Ladders 2-3-4-5 (1 fiber/ladder) -> 28 fibers

- ⇒ ~35 fibers on each side

- Diameter: ~ 1 mm  $\Rightarrow$  28 mm<sup>2</sup> ~ Section

| • | Surf | aces:                                                                |

|---|------|----------------------------------------------------------------------|

|   | -    | L0: ladders: $1.1 \times 12.5 \times 10 = 137.5 \text{ cm}^2$        |

|   | -    | L1: ladders: 1.1 x 12.5 x 10 = 137.5 cm <sup>2</sup>                 |

|   | -    | L2: ladders: $2.2 \times 12.5 \times 2 \times 11 = 605 \text{ cm}^2$ |

|   | -    | L3: ladders: $2.2 \times 12.5 \times 2 \times 11 = 605 \text{ cm}^2$ |

|   | -    | L4: ladders: 2.2 x 12.5 x 2 x 17 = 990 cm <sup>2</sup>               |

|   | -    | L5: ladders: 2.2 x 12.5 x 2 x 17 = 990 cm <sup>2</sup>               |

|   | -    | TOTAL : ladder surfaces = 3461 cm <sup>2</sup>                       |

|   |      |                                                                      |

# Cables (no shielding included)

#### • Power consumption VXD (instantaneous)

| INSTANTANEOUS POWER                            |          |         |        |       |       |       |  |  |  |  |

|------------------------------------------------|----------|---------|--------|-------|-------|-------|--|--|--|--|

| Power ON During Train per chip $(mW/chip)$     | 293.4    | 293.4   | 178.1  | 178.1 | 171.1 | 171.1 |  |  |  |  |

| Power ON Between Train per chip $(mW/chip)$    | 138.8    | 138.8   | 101.2  | 101.2 | 101.2 | 101.2 |  |  |  |  |

| Power OFF Between Train per chip $(mW/chip)$   | 10       | 10      | 10     | 10    | 10    | 10    |  |  |  |  |

| Power ON During Train per $cm^2 (mW/cm^2)$     | 82.21    | 82.21   | 49.92  | 49.92 | 47.95 | 47.95 |  |  |  |  |

| Power ON Between Train per $cm^2 (mW/cm^2)$    | 38.9     | 38.9    | 28.37  | 28.37 | 28.37 | 28.37 |  |  |  |  |

| Power OFF Between Train per $cm^2$ $(mW/cm^2)$ | 2.802    | 2.802   | 2.802  | 2.802 | 2.802 | 2.802 |  |  |  |  |

| Power ON During Train per layer $(W/layer)$    | 11.73    | 11.73   | 31.35  | 31.35 | 46.54 | 46.54 |  |  |  |  |

| Power ON Between Train per layer $(W/layer)$   | 5.553    | 5.553   | 17.81  | 17.81 | 27.53 | 27.53 |  |  |  |  |

| Power OFF Between Train per layer $(W/layer)$  | 0.4      | 0.4     | 1.76   | 1.76  | 2.72  | 2.72  |  |  |  |  |

| TOTAL : Surface= $3483 \ cm^2$ ; T             | otal Pea | k Power | = 179. | 3 W   |       |       |  |  |  |  |

- ~ P\_{tot}  $\sim$  200 W ; @ 1.8 V  $\Rightarrow$   $I_{tot} \sim$  100 A  $\Rightarrow$   $I_{1side}$  = 50 A per end caps

#### • Power cables

- Assuming copper (Aluminium doesn't change the picture)

- > Cable length L  $\sim$ 15 m

- >  $P_{diss}(cables) \sim 25 W \Rightarrow \Delta V = P_{diss}(cables) / I_{1side} = 0.5 V$

- > R =  $\rho$  L / S =  $\Delta$ V / I<sub>1side</sub>  $\Rightarrow$  S =  $\rho$  L I<sub>1side</sub> /  $\Delta$ V ~ 30 mm<sup>2</sup> ~ Section

#### • Control cables (copper)

- Section ~ 5 mm<sup>2</sup>

#### SIT

| Geometry |       |              |  |  |  |  |  |

|----------|-------|--------------|--|--|--|--|--|

| R[mm]    | Z[mm] | $\cos\theta$ |  |  |  |  |  |

| 153      | 368   | 0.910        |  |  |  |  |  |

| 300      | 644   | 0.902        |  |  |  |  |  |

# SIT

- Costing done in parallel

- Much more open integration questions

- ➤ More educated guesses...

- PLUME ladders have to be revisited

- Geometry

R[mm]

Z[mm]

cosθ

153

368

0.910

300

644

0.902

- Length / double sided ladder thickness / stiffness not the same

- ➤ Larger flex cable

- Stitching = improved stiffness ?

- > ALICE ITS upgrade:

Comparable dimensions and surfaces (not double sided though)

- Cabling / data flow schemes to be done

- Power (raw estimate with MIMOSIS architecture, 2 μs)

- Distribution in parallel ? (ALICE = 1 cable / ladder)

- Total surface: ~ 67 000 cm<sup>2</sup>

- Very low occupancy w.r.t to the VXD

- > <P> ~ 30 mW/cm<sup>2</sup> (NO power pulsing)  $\Rightarrow$  2 kW  $\otimes$

- $> < P > ~ 3.5 \text{ mW/cm}^2$  (with power pulsing)  $\Rightarrow 235 \text{ W}$

- More space for air flow

- Faster read-out (0.5 1  $\mu$ s range) would need more power.

ILD Integration, Feb. 2019

#### SIT costing

| Figures per lay                              | ers                        |             |                     |          |

|----------------------------------------------|----------------------------|-------------|---------------------|----------|

| Layer                                        | 0                          | 1           | 2                   | 3        |

| Layer Radius $(mm)$                          | 153                        | 155         | 298                 | 300      |