## **Devt of CMOS Sensors for an ILC Vertex Detector:**

**Progress since Summer '07 — Plans for 2008**

Marc Winter (IPHC-Strasbourg)

contributions from DAPNIA-Saclay, LPSC-Grenoble

▷ More info. on IPHC Web site : http://wwwires.in2p3.fr/ires/web2/rubrique.php3?id\_rubrique=63

## OUTLINE

- Tests of sets of sensors in real experimental conditions :

- \* Beam telescopes : EUDET (European project), TAPI

- **\*** STAR HFT telescope

- Fast sensors with digitised outputs :

- \* Fast column // architecture with integrated discriminators : beam tests, new chips

- \* Zero-suppression micro-circuit : lab tests

- Summary & Plans for 2008

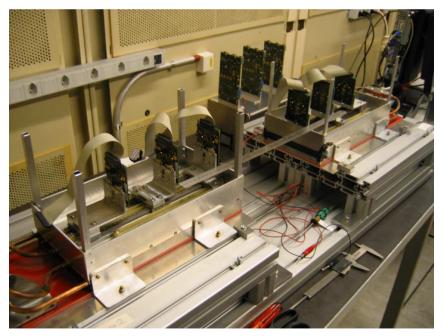

### Commissionning and Use of a MIMOSA Telescope

New beam telescope operated at DESY and CERN-SPS:

- ▶ T.A.P.I. = TELESCOPE A PIXELS DE L'IPHC

- ♦ 3 or 4 MIMOSA-17 or/and -18 sensors (more in future)

- ♦ Commissionning in June '07 at DESY

- ♦ Real data taking in Sep. & Nov. '07 at CERN-SPS

- $\diamond~$  R.o. freq.  $\sim~$  10 (M-18) or 25 frames/s (M-17)

- ♦ Running in front of Si-strip telescope ▷▷▷▷▷▷▷

Several studies at CERN-SPS:

CMOS-VD

- ightarrow response of sensors to inclined tracks:  $0 80^{\circ}$

- ← performances of sensors exposed to non-ionising radiation

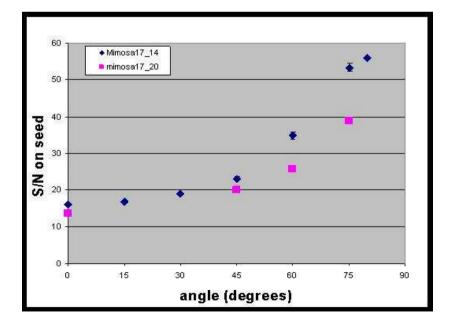

- ightarrow comparison of "14  $\mu m$ " to "20  $\mu m$ " epitaxy

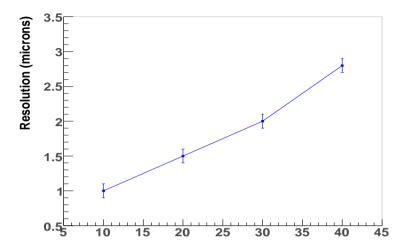

Mimosa resolution vs pitch

Single point resolution versus pixel pitch:

clusters reconstructed with eta-function,

exploiting charge sharing between pixels (12-bit ADC)

$oldsymbol{a}$   $\sigma_{f sp} \sim {f 1}~\mu{f m}$  (10  $\mu m$  pitch)  $ightarrow {ig 3}~\mu{f m}$  (40  $\mu m$  pitch)

Recent result obtained with very small pitch :

$\Rightarrow$  MIMOSA-18 : 512imes512 pixels with 10  $\mu m$  pitch, analog output, S/N  $\sim$  30

- $\Rightarrow$  tested on Si-strip telescope at CERN-SPS (120 GeV  $\pi^-$ ) in Nov. '07

- $\Rightarrow$  single point resolution observed (prelim.)  $\lesssim$  1  $\mu m$  !!!

- $\longleftrightarrow$  for EUDET telescope to allow  $\lesssim$  1  $\mu m$  on DUT surface with few GeV e^ beam

#### Motivation

- ⇔ simulate clusters from particules produced at shallow angle or from low  $e_{BS}^{\pm}$  (low p → curling in  $\phi$ )

- $\Leftrightarrow$  collect cluster data at various angles  $\rightarrowtail$  data base

- ⇔ adapt signal processing µcircuits and cluster rec. algo. to inclined tracks : 2–3 seed pixels, large signal, large clusters, …

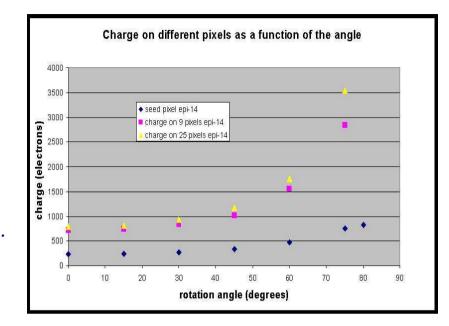

### Measurements performed with TAPI at CERN-SPS

- $\Rightarrow$  MIMOSA-17 (30  $\mu m$  pitch, rad. tol. pixel), T<sub>room</sub>

- $\Rightarrow$  measure Q, S/N,  $\sigma_{sp}$ ,  $\sigma_{\theta}$  at  $\theta$  = 0, 15, 30, 45, 60, 75, >80°

- ⇔ set-up data base for complete VD simulations (Lol)

- $\Rightarrow$  model cluster characteristics vs p &  $\theta$  for "fast" VD simul.

- work performed together with Lukazc Maczewski (Warsaw) (also: gyroscopic sensor support installed on DESY beam)

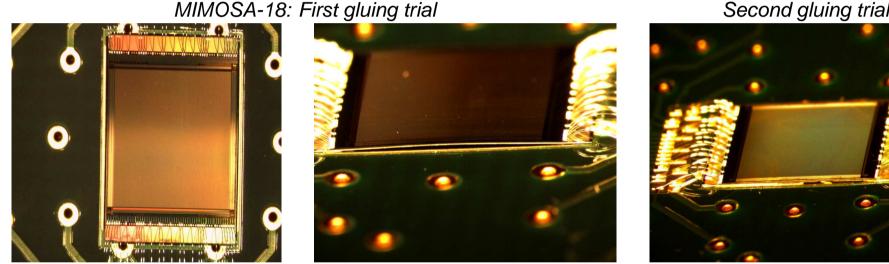

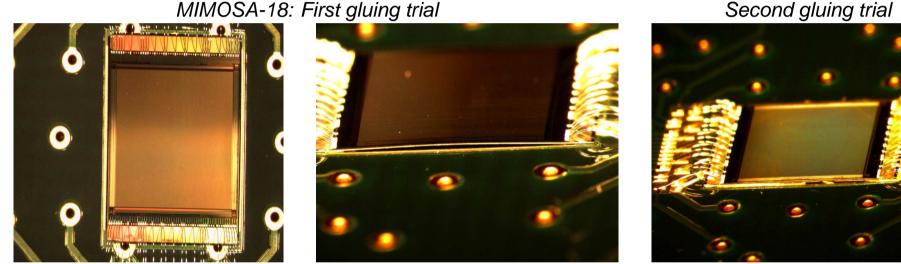

Thinning of AMS-0.35 engineering run reticles :

- ← Thinning performed by APTEK (S.F. bay) via LBNL (STAR coll.)

- $\Rightarrow$  Thickness claimed by provider : 50  $\mu m \rightarrow$  measured with IPHC bonding machine :  $\sim$  50–70  $\mu m$

- $\Rightarrow$  MIMOSA-18 (5.5×7.5 mm<sup>2</sup>) & -17 (8×9 mm<sup>2</sup>) mounted on PCB for tests  $\rightarrow$  keep them flat !

Second gluing trial

- $\Rightarrow$  Tests with <sup>55</sup> Fe source show no performance loss (noise, gain)

- $\Rightarrow$  Tests of MIMOSA-18 mounted on TAPI with 120 GeV  $\pi^-$  at CERN-SPS (Nov. '07)

- $\mapsto$  no performance loss observed  $\mapsto \epsilon_{det}$  = 99.79  $\pm$  0.15 % (prelim.)

**Preliminary conclusion :** Thinning down to  $\sim$  50  $\mu m$  seems on a good track

CMOS-VD

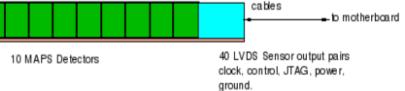

## Vertexing Applications of MIMOSA Chips: Short & Mid-Term

Vertex Detector upgrade for STAR expt at RHIC

- ightarrow 2 cylindral layers :  $\sim$  1600 cm $^2$

- $m \simeq \gtrsim$  160 million pixels ( $\leq$  30  $\mu m$  pitch)

- $\triangleright \triangleright$  2007: telescope (3 MIMO-14)  $\rightarrow$  BG meast, no pick-up !

- $\diamond$  2008/09: digital outputs without arnothing ( $\leq$  640  $\mu s$ )

- $\diamond$  2010/11: digital outputs with integrated Ø ( $\leq$  200  $\mu s$ )

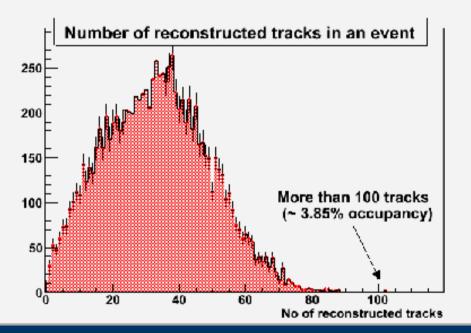

Beam telescope (FP6 project EUDET )

- $m \simeq$  provide  $\lesssim$  1  $\mu m$  resolution on 3 GeV e $^-$  beam (DESY)

**≏ 2 steps** :

- ⊳⊳ 2007: analog outputs

- ightarrow telescope commissionned & running ( $\lesssim$  100 tracks / frame)

- ightarrow used by non JRA-1 members at SPS (e.g. SILC)

- $\diamond$  2008/09: digital outputs with integ. arnothing ( $\sim$  100  $\mu s$ )

# Performances...

• This impressive plot is showing the pretty mature development stage of the tracking software.

CERN large multiplicity data taken two weeks ago

# **Integration of Signal Processing**

# **Inside Pixels and on Chip Periphery**

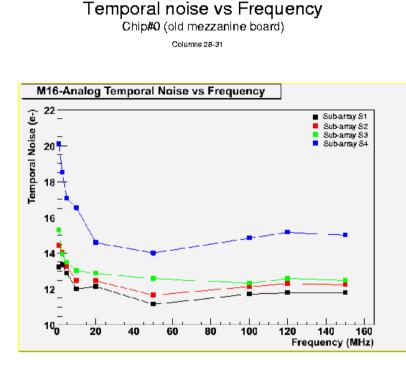

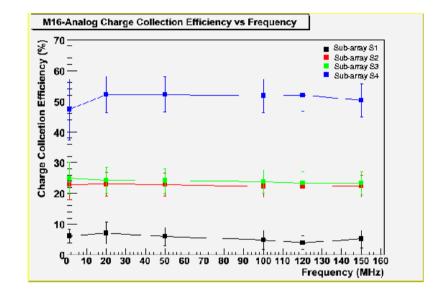

### High R.-O. Speed Architecture : 2nd Prototype = MIMOSA-16

MIMOSA-16 design features :

- AMS-0.35 OPTO translation of MIMOSA-8  $\hookrightarrow \sim$  11–15  $\mu m$  epitaxy instead of  $\lesssim$  7  $\mu m$

- $\bullet$  32 // columns of 128 pixels (pitch: 25  $\mu m$ )

- on-pixel CDS (DS at end of each column)

- 24 columns ended with discriminator

- 4 sub-arrays :

CMOS-VD

- S1 : like MIMOSA-8 (1.7x1.7  $\mu m^2$  diode)

- S2 : like MIMOSA-8 (2.4x2.4  $\mu m^2$  diode)

- S3 : S2 with ionising radiation tol. pixels

- S4 : with enhanced in-pixel amplification (against noise of read-out chain)

Tests of analog part ("20" & "14"  $\mu m$  epitaxy) :

- ullet sensors illuminated with  $^{55}$ Fe source and F $_{r.o.}$  varied up to  $\gtrsim$  150 MHz

- measurements of N(pixel), FPN (end of column), pedestal variation, CCE (3x3 pixel clusters) vs  $F_{r.o.}$

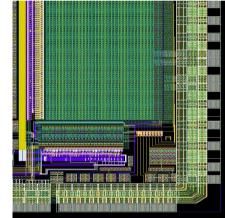

M.i.p. detection with Si-stip telescope studied at CERN in Sept. '07 ightarrow characterisation of digital response :

- $ullet \pi^-$  beam of  $\sim$  180 GeV/c

- measurements of SNR, det. efficiency, fake rate, cluster characteristics, spatial resolution vs discri. threshold

CMOS-VD

ERN-SPS ( $\sim$  180 GeV  $\pi^-$ )  $\rightarrow$  results of S4 ("14  $\mu m$ " epitaxy)

**Read-out time**  $\sim$  **50**  $\mu s$  ( $\sim$  1/4 of max. freq. due to DAS limitations)

Major result  $\rightarrowtail$  at least one pixel architecture validated for next steps : S4 (SNR  $\sim$  16)

| Discri. Threshold | det. efficiency           | fake rate                   | sgle pt resolution     |  |

|-------------------|---------------------------|-----------------------------|------------------------|--|

| 4 m V             | 99.96 $\pm$ 0.03 (stat) % | $\sim$ 2 $\cdot$ 10 $^{-4}$ | $\sim$ 4.8–5.0 $\mu m$ |  |

| 6 m V             | 99.88 $\pm$ 0.05 (stat) % | $< 10^{-5}$                 | $\sim$ 4.6 $\mu m$     |  |

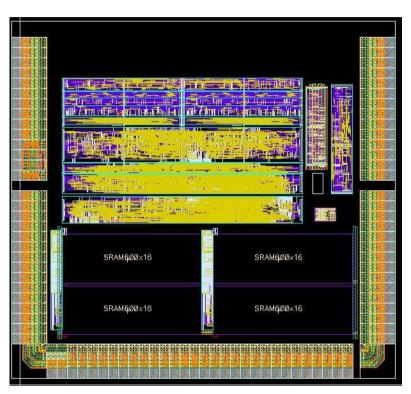

## Zero Suppression Micro-Circuit : SUZE-01 Fabrication & Tests

Ist chip (SUZE-01) with integrated  $\emptyset$  and output memories (no pixels) :

- \* 2 step, raw by raw, logic :

- $\diamond$  step-1 (inside blocks of 64 columns) : identify up to 6 series of  $\leq$  4 neighbour pixels per raw delivering signal > discriminator threshold

- $\diamond$  step-2 : read-out outcome of step-1 in all blocks and keep up to 9 series of  $\leq$  4 neighbour pixels

- \* 4 output memories (512x16 bits) taken from AMS I.P. library

- $\%\,{\rm surface}\sim {\rm 3.9}\times {\rm 3.6}\,{\rm mm}^2$

#### Status :

CMOS-VD

- \* back from foundry end of Sept. '07  $\rightarrow$  tests almost completed

- \* design performances reproduced up to 1.15  $\times$  design read-out frequency (T<sub>room</sub>) :

- > noise values as predicted, no pattern encoding error

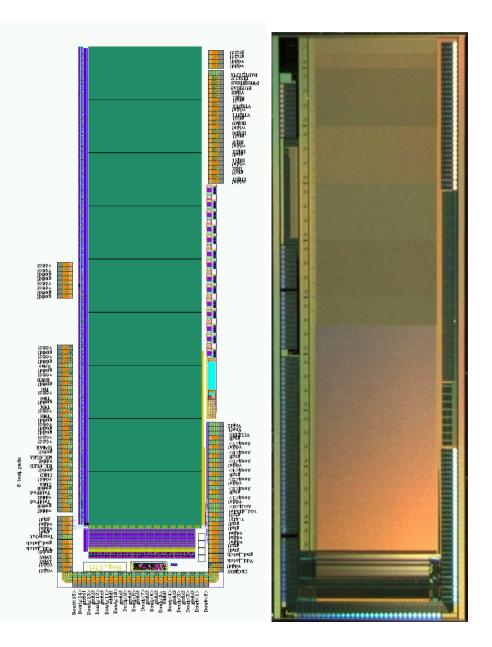

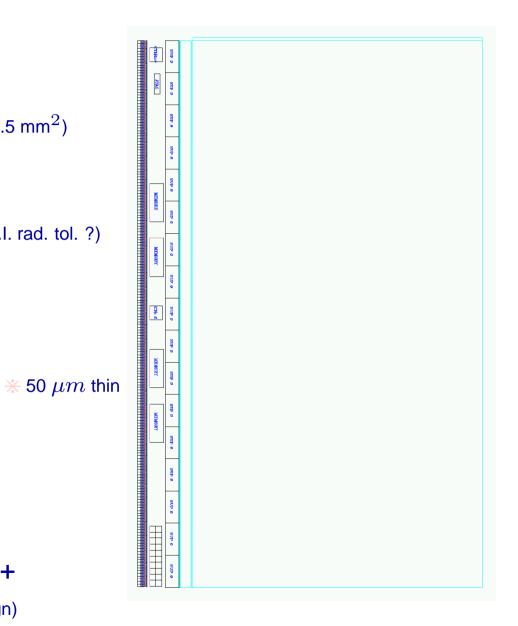

Final prototype with column // architecture : MIMOSA-22

### Extension of MIMOSA-16 $\rightarrowtail$ larger surface, smaller pitch, optimised pixel, JTAG, more testability

■ Pixel characteristics (optimal charge coll. diode size ?):

- st pitch : 18.4  $\mu m$  (compromise resolution/pixel layout)

- \* 128 columns ended with discriminator

- \* 8 columns with analog output for test purposes

- \* 9 sub-matrices of 64 rows :

- 17 pixel designs w/o ionising rad. tol. diode

- $\Rightarrow$  active digital area : 128 x 576 pixels ( $\sim$  25 mm<sup>2</sup>)

#### Testability :

CMOS-VD

- $\ensuremath{ \ensuremath{ \times } }$  JTAG + bias DAC  $\rightarrowtail$  programmable chip steering

- 2 additionnal DC voltages to emulate pixel's output for independent discriminator performance assessment

\* output frequency < 40 MHz</li>

#### Status :

- Back from foundry  $\rightarrow$  tests started in Feb.'08 (analog outputs)

- $ightarrow {}^{55}$ Fe source : chip active over whole surface (35°C, 92  $\mu s$ )

Steady progress towards perfo. adapted to running conditions with beam BG >> MC simulations

- **2008 :** \* final EUDET telescope sensor fab.:  $1 \times 2 \text{ cm}^2$ ; 0.6 Mpix; 100  $\mu s$ ; digital output with  $\emptyset$ ; 50  $\mu m$  thin \* STAR-HFT1 sensor fab.:  $2 \times 2 \text{ cm}^2$ ; 0.4 Mpix; 640  $\mu s$ ; digital output; 50  $\mu m$  thin  $\rightarrow$  D<sup>0</sup> phys. in 2010 \* several other R&D lines: fast archi. with ADC, new fab. proc., system integ., etc.  $\rightarrow$  FP-7 \* vertex detector design optimisation with physics processes  $\rightarrow$  Lol

- ► > 2008 : \* proto-ladder for outer/inner layers in 2010/2011 ( $\leq 0.2 \% X_0$ ), based on STAR-HFT ladder ( $\leq 0.28 \% X_0$ ) \* final sensor designs for outer/inner layers in 2010/2011 \* STAR-HFT2 sensor (data taking starting in 2011)

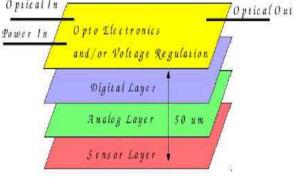

Perspective :  $3DIT MIMOSA \equiv 4$  chip sandwich

$\hookrightarrow$  optimal technology for each tier

# **BACK-UP SLIDES**

Pixel design :

- st adapt existing pixel architectures from 25  $\mu m$  to < 20  $\mu m$  pitch

- st adapt sensing diode dimensions to maximise CCE (surface  $\nearrow$ ) & gain (surface  $\searrow$ ) : optimum  $\sim$  10–15  $\mu m^2$

- ▶ find optimal pixel pitch : single point resolution (pitch  $\searrow$ ) against reliable design (pitch  $\nearrow$ )

Column read-out architecture :

- st adapt existing S&H and discriminators from 25  $\mu m$  to < 20  $\mu m$  pitch

- $\ensuremath{\overset{\scriptstyle }}$  integrate  $\ensuremath{\mathcal{O}}$  and output memories

Row and pixel steering (consequences of large surface) :

- \* adapt pixel steering (speed) inside column to avoid capacitance due to large nb of switches  $\rightarrow$  pixel design

- \* adapt row steering to their length (2 cm)

Sensor autonomy and testability :

- \* JTAG + bias DAC  $\rightarrowtail$  programmable chip steering

- \* 2 or 3 additionnal DC voltages to emulate pixel's output for independent discriminator performance assessment

### Developments simultaneously oriented towards well focussed applications and towards generic objectives useful to several applications

| Application              | version                     | 2006      | 2007         | 2008        | 2009        | 2010      | 2011      |

|--------------------------|-----------------------------|-----------|--------------|-------------|-------------|-----------|-----------|

| STAR HFT-1               |                             | R&D       | final proto. | Prod.       |             |           |           |

|                          | HFT-2                       | R&D       | R&D          | R&D         | proto final | Prod.     |           |

| EUDET                    | BT-1                        | 2 Prod.   | commissioned |             |             |           |           |

|                          | BT-2                        | R&D       | final proto  | Prod.       |             |           |           |

| Imaging                  |                             | R&D       | final proto  | Prod. ?     |             |           |           |

| Generic topics           |                             |           |              |             |             |           |           |

| Fast sensors :           | o architecture              | R&D       | R&D          | R&D +       | R&D ++      | ILC proto | CBM proto |

|                          | ○ ADC                       | R&D       | R&D          | final proto | ~           |           |           |

|                          | <ul> <li>digital</li> </ul> | pre-study | R&D          | final proto | ~           |           |           |

| Radiation tolerance      |                             | R&D       | R&D          | R&D         | R&D         | 7         |           |

| Fabrication technologies |                             | R&D       | R&D          | R&D         | R&D         | ∕`???     |           |

| Thinning                 |                             | R&D       | D            | D           | OK ???      |           |           |

### Radiation Tolerance: Summary of AMS-0.35 OPTO Evaluation

Established ionising radiation tolerance (reminder): 1 MRad –  $2 \cdot 10^{12} n_{eq}/cm^2$  –  $10^{13} e_{10 MeV}^{-}/cm^2$  OK

Non-ionising radiation tolerance (Summer / Autumn 2007):

\* MIMOSA-18 irradiated with  $\leq$  10<sup>13</sup> O(1 MeV) n/cm<sup>2</sup> (+ 100–200 kRad  $\gamma$  gas)  $\Rightarrow$  tested on  $\sim$  120 GeV  $\pi^-$  beam (SPS)

▷ Preliminary results:

CMOS-VD

• T =  $-20^{\circ}$ C • t<sub>r.o.</sub> ~ 3 ms • cuts at 5N (seed) & 2N (crown)

| Seed pixel noise for re | eal track cluster 10 <sup>13</sup>     | Charge in 9 pixels                                            |                                      | Fluence (n $_{eq}$ /cm $^2$ )                           | 0                      | $6{\cdot}10^{12}$      | $1 \cdot 10^{13}$    |

|-------------------------|----------------------------------------|---------------------------------------------------------------|--------------------------------------|---------------------------------------------------------|------------------------|------------------------|----------------------|

| 5000                    | 6X10 <sup>13</sup><br>— not irradiated | 400<br>350<br>300                                             | 6X10 <sup>13</sup><br>mot irradiated | Noise (e $^{-}ENC$ )<br>(-20 $^{\circ}$ C, 3 ms, 5N/2N) | <b>10.8</b><br>± 0.3   | <b>12.2</b><br>± 0.3   | <b>14.3</b><br>± 0.3 |

| 4000                    |                                        | <b>250</b>                                                    |                                      | ${f Q}_{clust}$ (e )                                    | 1026                   | 680                    | 560                  |

| 3000                    |                                        |                                                               |                                      | S/N (MPV)                                               | 28.5                   | 20.4                   | 14.7                 |

| 2000                    |                                        | 150 <b>[</b> ] <b>] ] ]</b>                                   |                                      |                                                         | $\pm$ 0.2              | $\pm$ 0.2              | $\pm$ 0.2            |

|                         |                                        | 100<br>50<br>0<br>50<br>0<br>50<br>50<br>50<br>50<br>50<br>50 | 0 2500 3000 3500 4000                | Det. Eff. (%)                                           | <b>99.93</b><br>± 0.03 | <b>99.85</b><br>± 0.05 | <b>99.5</b><br>± 0.1 |

$\sim$  10 $^{13}$  n/cm $^2$ /s affordable at T < 0 $^{\circ}$ C & t $_{r.o.}$   $\sim$  O(1) ms & 10  $\mu m$  pitch

$\hookrightarrow$  study tolerance vs pitch, diode size, r.o. speed, digital output, ......, annealing ?????

# **Integration of Signal Processing**

# **Inside Pixels and on Chip Periphery**

#### Pixel noise and charge collection efficiency ("20 $\mu m$ " epitaxy) :

Charge Collection Efficiency vs Frequency

Chip#0 (old mezzanine board)

Columns 28-31

### $\Rightarrow$ Noise performance satisfactory (like MIMOSA-8 and -15)

- $\Rightarrow$  CCE: very poor for S1 (1.7x1.7  $\mu m^2$ ) & poor for S2/S3 (2.4x2.4  $\mu m^2$ )

- ightarrow already observed with MIMOSA-15 but more pronounced for "20  $\mu m$ " option

- $\hookrightarrow$  suspected origin: diffusion of P-well, reducing the N-well/epitaxy contact, supported by CCE of S4 (4.5x4.5  $\mu m^2$  diode)

4

### Next steps :

- *Mid-term : EUDET, STAR → real experimental conditions*

- Long-term full sensor prototyping : CBM ( and ILC)

Integrated  $\varnothing

ightarrow$  real scale sensors without ADC ( $\sigma_{sp} \sim$  4–6  $\mu m$ ) :

- \* EUDET telescope (2008)

- \* STAR-HFT1/2 (2010/11)

- **★ CBM-MVD (**≥ 2012)

Increasing read-out speed and replacing discriminators with 4-5 bit ADC (ILC) :

\* read-out speed  $\rightarrow$  CBM-MVD ( $\gtrsim$  2012)

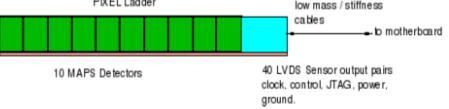

Autumn 2008 : MIMOSA-22+ = Final EUDET Sensor \* MIMOSA-22 complemented with  $\emptyset$  (SUZE-01) 1 or 2 sub-arrays (best pixel architectures of MIMOSA-22) Active surface : 1088 columns of 544/576 pixels (20.0 x 10/10.5 mm<sup>2</sup>) st Read-out time  $\sim$  100  $\mu s$ \* Chip dimensions :  $\sim$  20 x 12 mm<sup>2</sup>  $\triangleright$  Opportunity for an engineering run combining various chips (N.I. rad. tol. ?) Devts performed in *//* : \* June 2008 : submission of final STAR-HFT1 sensor  $ightarrow \sim 2 \times 2 \text{ cm}^2$ \* 400 kpix/sensor  $* \leq 640 \ \mu s$  $\hookrightarrow$  equip 2 or 3 sectors of 1 + 3 ladders (10 chips/ladder) \* explore new tracks : XFAB, IBM-0.18 OPTO, 3DIT, ...

**Beyond 2008:**

$\texttt{ * design sensor for STAR-HFT2} \rightarrowtail \texttt{ extension of MIMOSA-22+}$

st increase r.o. frequency by  $\sim$  50 % (new  $extsf{Ø}$  & memory design)

# **System Integration Studies**

# Thinning

# Ladder design

Data Flow

Thinning motivations and constraints :

- $\Leftrightarrow$  thin sensors to  $\lesssim$  material budget of "mechanical support"

- ⇔ minimal thickness of CMOS sensors :

10–15  $\mu m$  (metal layers and SiO $_2$ ) + 15  $\mu m$  (T + epitaxy) + 5–10  $\mu m$  (substrate) pprox 30–40  $\mu m$

- thinned sensors should be "easy" to handle

- ⇔ thinning procedure should have high mechanical yield and preserve detection performances

- $\Rightarrow$  CMOS technology fab. yield  $\rightarrow$  foster diced sensors (despite few 10<sup>-4</sup> X<sub>0</sub> add. mat. budget / ladder)

- ⇔ thinning of individual sensors seems preferable to full wafer thinning : cheaper but same quality ?

MIMOSA-5 : 6" wafer

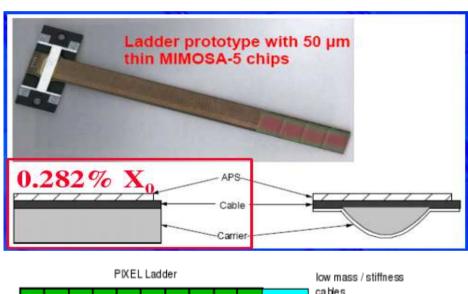

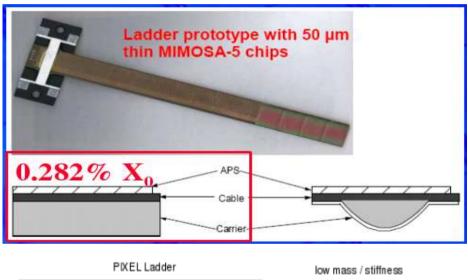

### Status of Thinning Studies and Ladder Prototyping (STAR)

Predominantly driven by STAR HFT project at LBNL

Thinning of MIMOSA-5 wafers :

CMOS-VD

- $\Rightarrow$  3 wafers thinned via LBNL to 50  $\pm$  5  $\mu m$

- result satisfactory (after pre-dicing): sensors can be manipulated and mounted on support

⇒ 3 ladder prototypes fabricated at LBL (≥ 0.25 % X<sub>0</sub>)

$\rightarrowtail$  up to 9 sensors mounted on ladder and tested

Thinning of individual sensors to  $\sim$  50  $\mu m$ :

$\Rightarrow$  several chips of  $\sim$  0.2 – 3.5 cm<sup>2</sup> (MIMOSA-5, -10, -14, -17, -18, -20, etc.) thinned individually via LBNL

$\Rightarrow$  recent result: MIMOSA-18 prototype thinned to 50  $\mu m$  was successfuly tested with  $^{55}$  Fe at IPHC

$\rightarrowtail$  no change of performances (e.g. noise, gain, det.eff, ...)  $\rightarrowtail$  next slide

⇔ Plans : • replace present (thick) sensors (MIMOSA-17, -18) equipping telescopes (EUDET, TAPI, ...)

- equip STAR-HFT1 with thinned sensors (2008/09)  $\rightarrow$  0.25 0.3 % X<sub>0</sub>

- extend ladder devt to ILC Vertex Detector (LBNL-ILC team ?)  $\rightarrow$  goal  $\leq$  0.2 % X<sub>0</sub>

Thinning of AMS-0.35 engineering run reticles :

- ← Thinning performed by APTEK (S.F. bay) via LBNL (STAR coll.)

- $\Rightarrow$  Thickness claimed by provider : 50  $\mu m

ightarrow$  measured with IPHC bonding machine :  $\sim$  50–70  $\mu m$

- $\Rightarrow$  MIMOSA-18 (5.5×7.5 mm<sup>2</sup>) & -17 (8×9 mm<sup>2</sup>) mounted on PCB for tests  $\rightarrow$  keep them flat !

Second gluing trial

- $\Rightarrow$  Tests with <sup>55</sup> Fe source show no performance loss (noise, gain)

- $\Rightarrow$  Tests of MIMOSA-18 mounted on TAPI with 120 GeV  $\pi^-$  at CERN-SPS (Nov. '07)

- $\mapsto$  no performance loss observed  $\mapsto \epsilon_{det}$  = 99.79  $\pm$  0.15 % (prelim.)

**Preliminary conclusion :** Thinning down to  $\sim$  50  $\mu m$  seems on a good track

Data flow:

- hundreds of millions of fast pixels ⇒ data flow is a MAJOR CONCERN !!!

- $\Rightarrow$  U.L.M. Photonics : 250x250  $\mu m^2$  electro-optical converters  $\mapsto$  several Gbits/s

- ⇔ design of laser driver under study at IPHC

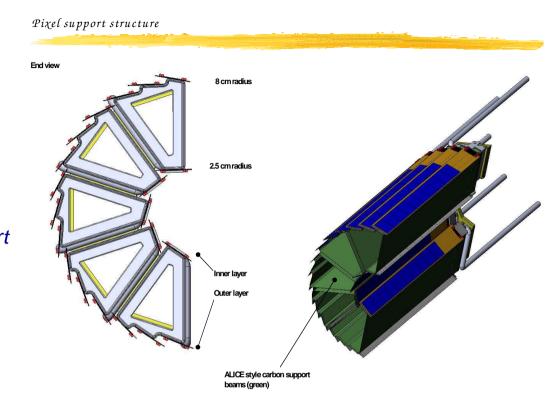

New concept of mechanical support & heat extractor:

- ⇔ objective : mount, connect & operate  $\sim$  4 MIMOSA-18 (?) sensors, thinned to 50  $\mu$ m, on 50–100  $\mu$ m thin, aluminised, CVD diamond slabs  $\equiv$  mech. support heat extractor cable support

- $\Leftrightarrow$  status : 3 diamond 3" wafers fabricated  $\rightarrow$  electroplating and lithography, etc.

- >>> proto-ladders back at IPHC-Strasbourg before Summer

**General remark :**

- CMOS sensors call for CHALLENGING system integration solutions : connexions (flex cable), data flow, ...

- $\Rightarrow$  Lot of expertise and effort needed  $\Rightarrow$  Forces needed NOW !

- Minimise multiple scattering inside detector material wherever possible (b  $\searrow$  )

- → thickness, amount and choice of material for mechanical support, gluing, electrical connexions, thermal conductivity, power dissipation (avoid active cooling), ...

- Goal : < 0.2 % radiation length / layer (including chip + support + services) (  $\Leftrightarrow$  < 200  $\mu m$  of silicon )

- Presently < 0.3 % seems achievable (STAR vertex detector)

- STAR ladder : kapton cable contributes with 0.090 % and carrier with 0.110 % of radiation length

- $\Rightarrow$  replace them with aluminised CVD diamond ?

- $\hookrightarrow$  bonus in thermal transport

- (CMOS) Sensor fabrication yield is a concern

⇒ diced sensors prefered to stitched sets of 5–10 sensors

- $\hookrightarrow$  inactive zones (  $\gtrsim$  40  $\mu m$  wide ) at sensor edge from dicing

- $\Rightarrow$  can these zones be reduced to  $\lesssim$  few  $\mu m$  with plasma etching ?

- Minimise multiple scattering inside detector material wherever possible (b  $\searrow$  )

- → thickness, amount and choice of material for mechanical support, gluing, electrical connexions, thermal conductivity, power dissipation (avoid active cooling), ...

- Goal : < 0.2 % radiation length / layer (including chip + support + services) (  $\Leftrightarrow$  < 200  $\mu m$  of silicon )

- Presently < 0.3 % seems achievable (STAR vertex detector)

- STAR ladder : kapton cable contributes with 0.090 % and carrier with 0.110 % of radiation length

- $\Rightarrow$  replace them with aluminised CVD diamond ?

- $\hookrightarrow$  bonus in thermal transport

- (CMOS) Sensor fabrication yield is a concern

⇒ diced sensors prefered to stitched sets of 5–10 sensors

$\hookrightarrow$  inactive zones ( \gtrsim 40  $\mu m$  wide ) at sensor edge from dicing

$\Rightarrow$  can these zones be reduced to  $\lesssim$  few  $\mu m$  with plasma etching ?

## ► 3D Integ. Techno. include thinning and dicing capacities of great interest