# An ILD vertex detector with CMOS sensors

status report

J.Baudot, for the IPHC group baudot@in2p3.fr

Orsay 2011 May 23

- Detector specifications

- x CMOS sensor architecture

- x Perspective toward the DBD

- x Beyond the DBD

- x Summary

- x Back-up slides

## The CMOS sensor-based VXD

### Inner layer – internal side

- X Optimized for resolution

- x 16 x 16  $\mu$ m<sup>2</sup>

- X Q encoding: binary

- x  $t_{Integration} \sim 40 \ \mu s$

- ✗ Sensitive area ~ 2 cm²

## Outer layer

- x Optimized for low power

- x 35 x 35  $\mu$ m<sup>2</sup>

- x Q encoding: 4-bits

- $\textbf{\textit{x}} \quad t_{\text{Integration}} \sim \! 100 \; \mu \text{s}$

- ✗ Sensitive area ~ 4 cm²

#### Inner layer – external side

- x Optimized for r.o. speed

- x 16 x 64 μm<sup>2</sup>

- x Q encoding: binary

- x  $t_{Integration} \sim 10 \ \mu s$

- ✗ Sensitive area ~ 2 cm²

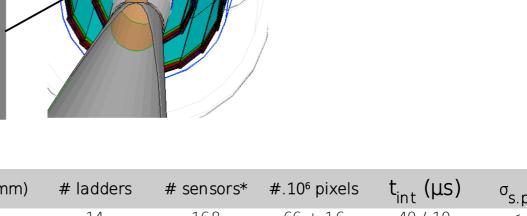

| layer | ra dius (mm) | length (mm) | # ladders | # sensors* | #.10 <sup>6</sup> pixels | t <sub>int</sub> (µs) | σ <sub>s.p.</sub> (μm) |

|-------|--------------|-------------|-----------|------------|--------------------------|-----------------------|------------------------|

| 1     | 16/18        | 125         | 14        | 168        | 66 + 16                  | 40 / 10               | < 3 / ~5               |

| 2     | 37/39        | 250         | 26        | 312        | 2x112                    | 100                   | < 4                    |

| 3     | 58/60        | 250         | 40        | 480        | 2x173                    | 100                   | < 4                    |

| total |              |             | 80        | 960        | 652                      |                       |                        |

<sup>\*</sup> Numbers corresponding to current CMOS technology (0.35 μm) prototypes

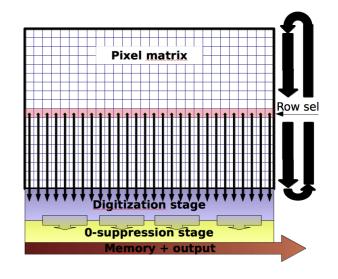

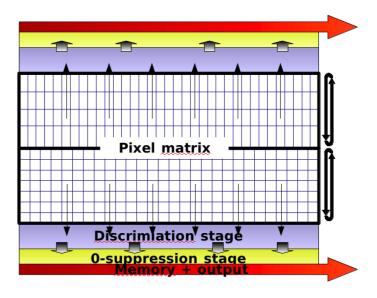

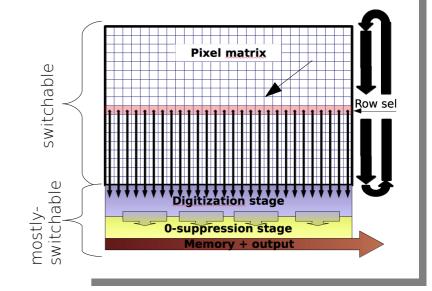

## **Architecture concepts**

#### CMOS sensors: high granularity & low power

- x In-pixel: pre-amplification pedestal suppression

- periphery: digitization + zero-suppression

- x Readout strategy = rolling-shutter (column //)

- → single row active at a time → save power

- $\rightarrow$   $t_{integration} = t_{read-out}$

- Active only during train (2 to 4 ms)

- → Power pulsing with duty cycle 1/100 to 1/50

- x Collaboration: IPHC, IRFU

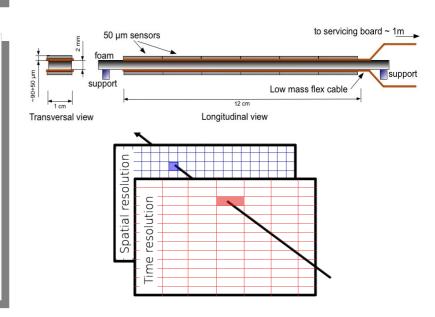

#### Ladders:

- x Sandwich: sensor+cable / stiffener / cable+sensor

- → Increased stiffness → low mass spacer (foam)

- → Allows to combine sensors with different spec.

- x Air cooling assumed

- **x** PLUME collaboration:

- → DESY, IPHC, Uni. Bristol, Uni. Oxford

## **CMOS** sensor prototypes

- Test points for:

- Pixels out (analogue)

- > Discriminators

- > Zero suppression

- Data transmission

- Row sequencer

- Width: ~350 µm

- 1152 column-level discriminators

- offset compensated high gain preamplifier followed by latch

- Zero suppression logic

- Reference Voltages

Buffering for 1152

discriminators

- I/O Pads

Power supply Pads

Circuit control Pads

LVDS Tx & Rx

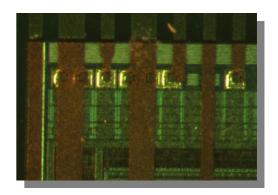

MIMOSA 26:

CMOS 0.35 µm OPTO technology

Chip size: 13.7 x 21.5 mm2

- Pixel array: 576 x 1152, pitch: 18.4 μm

- Active area: ~10.6 x 21.2 mm²

- In each pixel:

- Amplification

- CDS (Correlated Double Sampling)

■ Current Ref.

Bias DACs

- Readout controller

- JTAG controller

- Memory management

- Memory IP blocks

- PLL, 8b/10b optional

- x EUDET Final Telescope chip

- $\mathbf{x}$  Fabricated in 2009 & 2010 with standard (few Ω.cm) & high resistivity (400 Ω.cm)

- x Yield 75% for "perfect" sensors, 90% for usable

- x Thinned down to 50 μm

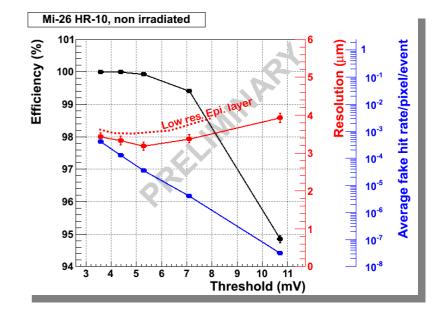

## **CMOS** sensor prototypes

#### MIMOSA 26

- x Readout time (pixel clock 80 MHz)  $\sim$  100  $\mu$ s

- $\rightarrow$  > 10<sup>6</sup> part/cm<sup>2</sup>/s

- Power dissipated ~250 mW/cm²

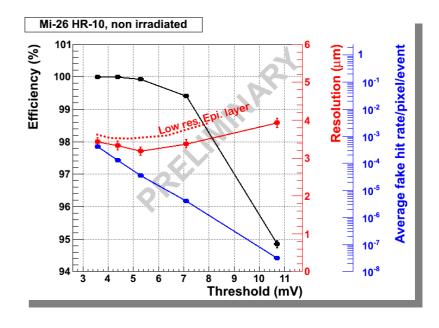

#### MIMOSA 22 High Resistivity (400 Ω.cm), fab 2010

## **CMOS** sensor prototypes

#### MIMOSA 26

- x Readout time (pixel clock 80 MHz)  $\sim$  100  $\mu$ s

- $\rightarrow$  > 10<sup>6</sup> part/cm<sup>2</sup>/s

- x Power dissipated ~250 mW/cm²

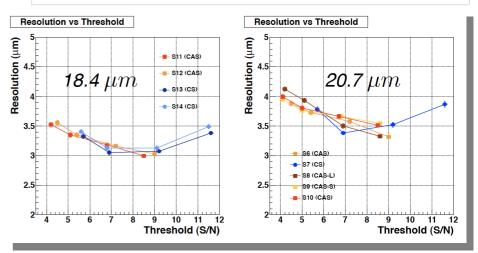

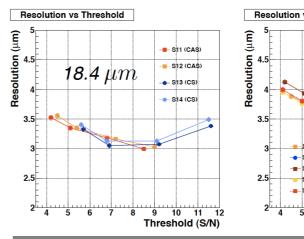

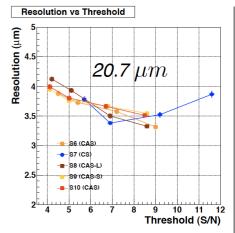

## • Spatial resolution $(\sigma_{s,p})$

- x Depends on: pitch, epi. layer, SNR, q-encoding

- x Extrapolation from previous measurements

| Pitch (µm)             | 20.7            | 18.4            | 16                  |

|------------------------|-----------------|-----------------|---------------------|

| Nb of bits             | 1               | 1               | 1                   |

| Epi. layer             | high R.         | high R.         | high R.             |

| σ <sub>s.p.</sub> (μm) | measured<br>3.5 | measured<br>3.1 | extrapolated<br>2.7 |

| Pitch (µm)             | 20       | 20                          | 30       | 35                  | 40            |

|------------------------|----------|-----------------------------|----------|---------------------|---------------|

| Nb of bits             | 12       | 4                           | 12       | 4                   | 12            |

| Epi. layer             | low R.   | low R.                      | low R.   | low R. high R.      |               |

| σ <sub>s.p.</sub> (μm) | measured | re-<br>processe<br>d<br>1.7 | measured | extrapolated<br>< 4 | measured<br>3 |

#### MIMOSA 22 High Resistivity (400 Ω.cm), fab 2010

## DBD perspective: sensors

#### Inner layer sensors

- x MIMOSA 30

- x Two-sided readout

- $\rightarrow$  256 rows with pitch 16x16 µm<sup>2</sup>

- · Spatial resolution < 3 μm

- → 64 rows with pitch 16x64 µm<sup>2</sup>

- · Spatial resolution ~5 μm

- x 128 columns with binary output

- → with pixel clock @ 100 MHz

- → Readout time < 50 µs

#### Outer layers sensor

- x MIMOSA 31

- x Pitch 35x35 μm<sup>2</sup> & 4-bits output

- → Spatial resolution < 4 μm

- x 48 columns over 64 rows

- → Readout time ≤ 100 µs

#### For both sensors

- x CMOS 0.35 μm technology

- x fabrication Q4 2011 (if funding available)

- x Beam test before mid-2012

- → Translation into 0.18µm techno. underway

## DBD perspective: ladders

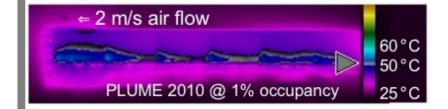

#### PLUME ladder 2010 design

- x Focus on <u>functionality</u> (8 Mpixels, 9 W cont. readout 100 μs)

- Material budget ~ 0.6% X0 (= 2x target value)

- → low-mass cable very wide & uses copper traces

- → Stiffener SiC foam with 8% density

- x Lab tests

- → Air cooling @ 2 m/s

- → Positioning precision + stability (ongoing)

- → Crude power pulsing test (MIMOSA 26 not optimized)

- Beam test: November 2011

- → Impact on resolution from air cooling & power pulsing

Thermal measurement

## DBD perspective: ladders

#### PLUME ladder 2010 design

- x Focus on <u>functionality</u> (8 Mpixels, 9 W cont. readout 100 μs)

- **x** Material budget  $\sim 0.6\% \times 10^{-2}$  X0 (= 2x target value)

- → low-mass cable very wide & uses copper traces

- → Stiffener SiC foam with 8% density

- x Lab tests

- → Air cooling @ 2 m/s

- → Positioning precision + stability (ongoing)

- → Crude power pulsing test (MIMOSA 26 not optimized)

- **x** Beam test: November 2011

- → Impact on resolution from air cooling & power pulsing

Thermal measurement

#### PLUME ladder 2011design

- x Optimized for <u>material budget</u>

- → Final figure depends on cable mass & stiffener (design finalized Spring'10) assuming 13 µm aluminum traces & 4% SiC foam

- → Transversal cross-section ~ 0.29 % of X0

- → Average over the ladder surface (weight/sensitive area) ~ 0.47 % of X0

- New low-mass cable fabrication Summer 2011

- → First ladder ~ fall 2011, Beam test summer 2012

#### Extrapolation with:

- same concept

- thinner sensor

- thinner cable

- → average ~0.3 % X0

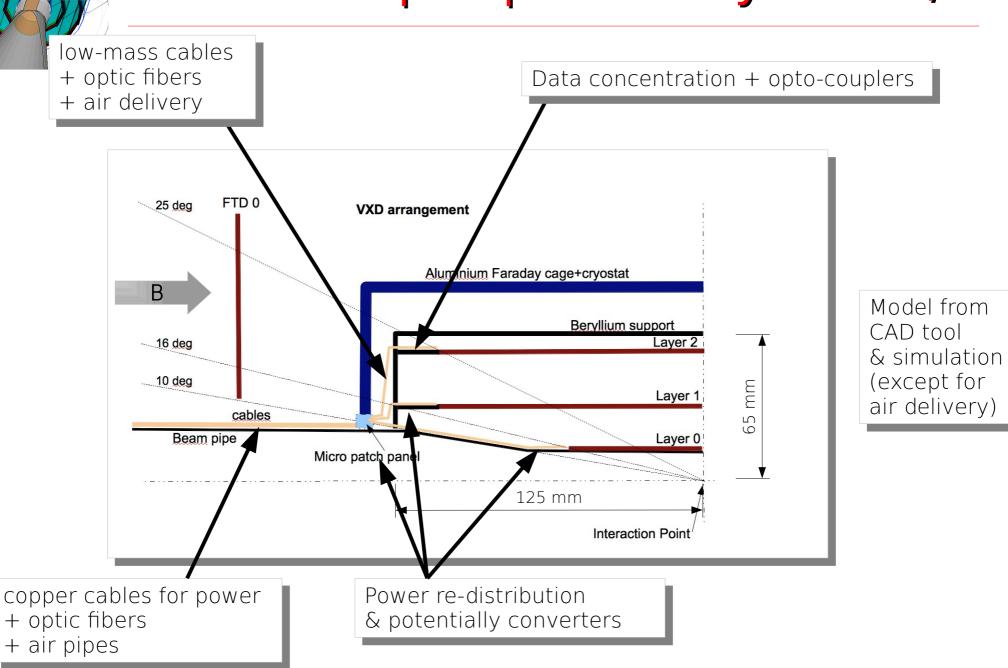

## DBD perspective: system 1/3

## DBD perspective: system 2/3

### Powering

- x Estimation done:

- → Overall dissipation during train (power on) ~ 900 W (0.35 µm techno) > 700 W (0.18 µm techno.)

- $\rightarrow$  Duty cycle 1/50 to 1/100  $\rightarrow$  20 to 30 W in average

- **x** Delivery strategy to be optimized:

- → Cable size for 700W seems OK / material budget (< 10 g/ cm on pipe)

- → BUT potential gain with DC-DC converters and/or regulators and/or capacitor

- → Location of converters and patch panel not fixed

- → Several scenario to be identified for DBD

- Sensor-level power delivery studies ongoing @ IPHC

- → Timeline beyond DBD

#### Data flow

- **x** Estimation done:

- $\rightarrow$  Driven by the first layer with an average rate of 5 part/cm<sup>2</sup>/bunchX x 10 (security factor x fluctuation)

- → During train: O(1)Tbps data throughput within 1 ms

- Optimization with serializer & opto-converter

- → Work in collaboration with SMU-Dallas (ATLAS)

- → Will not converge for DBD

## DBD perspective: system 3/3

#### Faraday cage & cryostat

- x Current model extrapolated from SLD

- No recent work...

- → Option to share with first FTD stations?

- x Potential tests with PLUME ladders but not scheduled yet

#### Mechanical support

- x Current Beryllium support model extrapolated from SLD

- No changes expected within 12 months

#### Cooling

- x Air cooling "seems" sufficient for 20 to 30 W but which air speed?

- Study for 1 ladder will be completed within PLUME

- x Simulation for whole detector possible @ DESY

- x No work on the air delivery pipe yet

- **1**s 0.5 → 1 TeV

- **x** Effects: beam bckd x2, physics  $x\sqrt{s}$ , longer decay distances

- **x** Impacts:

- → Sensors with shorter integration time

- → Geometry may be revisited

### 2D CMOS 0.18 μm technology upgrade

- x Lower power or higher speed (20 to 30%)

- Also: higher data reduction, smaller pitch, higher radiation tolerance, smaller size peripheral circuitry, stitching

- x First prototype to submit in Q4 2011

- → <u>4-5 years program</u> to reach "final" sensors

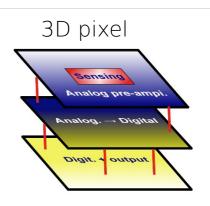

#### 3D integration technology

- x Optimizes CMOS techno. for each functionality / tier

- x Very high expectations: O(10)  $\mu m$  pitch with O(1)  $\mu s$  readout or 50 ns time-stamping

- x First prototypes fabricated within consortium coordinated by FNAL

- → Long term program

### 2D CMOS 0.18 μm technology upgrade

- x Lower power or higher speed (20 to 30%)

- Also: higher data reduction, smaller pitch, higher radiation tolerance, smaller size peripheral circuitry, stitching

- x First prototype to submit in Q4 2011

- → <u>4-5 years program</u> to reach "final" sensors

#### 3D integration technology

- x Optimizes CMOS techno. for each functionality / tier

- $ilde{\textbf{x}}$  Very high expectations: O(10)  $\mu m$  pitch with O(1)  $\mu s$  readout or 50 ns time-stamping

- x First prototypes fabricated within consortium coordinated by FNAL

- → Long term program

# Sensing Analog pre-ampl. Analog. — Digital Digit. • output

#### Ladders

- x Further decrease mat. budget

- → Stitching, embedded sensors

- x single-sided ladders

- x cooling/support alternatives

#### 2D CMOS 0.18 µm technology upgrade

- x Lower power or higher speed (20 to 30%)

- Also: higher data reduction, smaller pitch, higher radiation tolerance, smaller size peripheral circuitry, stitching

- x First prototype to submit in Q4 2011

- → <u>4-5 years program</u> to reach "final" sensors

#### 3D integration technology

- x Optimizes CMOS techno. for each functionality / tier

- × Very high expectations: O(10) μm pitch with O(1) μs readout or 10 ns time-stamping

- x First prototypes fabricated within consortium coordinated by FNAL

- → Long term program

# Sensing Analog pre-ampi. Analog. — Digital Digit. + output

#### Ladders

- x Further decrease mat. Budget

- → Stitching, embedded sensors

- x single-sided ladders

- x cooling/support alternatives

## Algorithm studies

- x Validated on theam within AIDA project & PLUME collab.

- **x** Benefits of 2-sided ladders

- → Alignment, track matching

## Summary

#### The CMOS sensor VXD concept

#### x 2 sensor flavors

- $\rightarrow$  inner layers:  $\sigma_{s.p.} < 3 \mu m$  for 40 /10  $\mu s$  integration

- $\rightarrow$  outer layer:  $\sigma_{s.p.}$  < 4 $\mu$ m for 100  $\mu$ s integration

- x Based on well established MIMOSA 26 architecture

#### Toward the DBD

- x Prototypes for the 2 sensor flavors fabricated & tested (beam)

- X Double-sided ladder with material budget of

0.6% X0 in 2011 ≥ 0.3 to 0.45 % X0 in 2012 fabricated & tested (beam)

- x Detailed needs estimated for services

#### Beyond the DBD

- x Technology migration for enhanced performances (2D short-term, 3D long-term)

- → Mitigate integration difficulty (material budget, power)

- → Answer 1 TeV challenges

- x Development of services

- Benefits expected from synergy with other projects: STAR, CBM, ALICE, AIDA

→ sensor stitching, readout speed, material budget, integration techniques

#### Additional slides

- x Computing the spatial resolution

- x DEPFET status

- Pixelated SiT

- Power pulsing

- Power & low mass cables

- x Parameter space for VXD

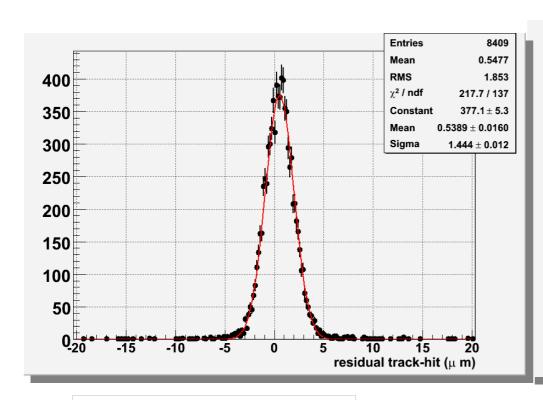

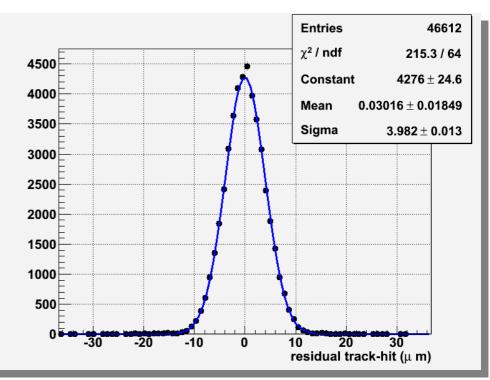

# Defining the spatial resolution

#### From the residual resolution

- x Fit with a single gaussian

- $\mathbf{x}$  Spatial resolution = single gaussian std. deviation

Analog sensor case: MIMOSA 18, pitch 10 μm

Binary sensor case: MIMOSA 26, pitch 18.4 μm

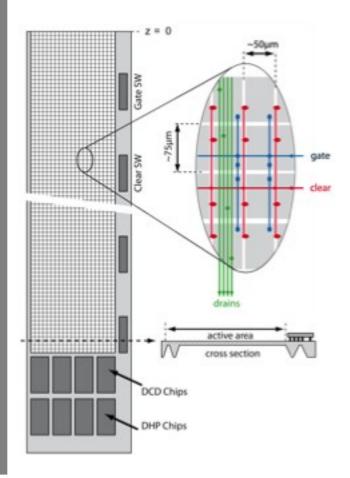

## The DEPFET-based VXD

#### The Belle II VXD as ILD demonstrator

- x 2 single-sided ladders with DEPFET APS ladders

- x L1: radius 14 mm, 90x12.5 mm2, 8 ladders, 50x50μm2, 1600x250 pix/ladder

- x L2: radius 22 mm, 126x12.5 mm2, 12 ladders, 50x75μm2, 1600x250 pix/ladder

- x Thin (50μm) sensitive area, ladder concept like in ILD

- → 0.19 % X0 in fiducial volume

- Frame rate 100kHz (L1) and 50kHz(L2), continuous read-out

- x Line rate: 12.5 MHz, "rolling shutter" mode

- Power dissipation per ladder (20 ladders)

- → Sensor ~1 W + switcher ~1 W

- → DCD+DHP chips ~ 8 W

- x Radiation damage: a few Mrad/year

- No requirements in forward region relaxed end-of-ladder (EOL) specs for material and services

- no power pulsing possible, but aggressive (liquid) cooling on EOL allowed

- x first Belle II data expected 2014

From L.Andricek, 2010

# the pixelated SiT option

## Power pulsing sensor

### Pulsing strategy

- x Activity period ~ 2 to 4 ms over the 200 ms train

- → Estimated duty cycle range: 1/50 to 1/100

- **x** For stability reasons, not all element switchable

- → Test started for the analog part

- → To be done for the digital circuitry

| Assuming: 0.18µm techno.<br>& 1.8 V voltage<br>& continuous operation |             | sensor  |          | 2-sided ladder |         |          | whole detector |         |          |       |

|-----------------------------------------------------------------------|-------------|---------|----------|----------------|---------|----------|----------------|---------|----------|-------|

|                                                                       |             | switch. | not-swi. | total          | switch. | not-swi. | total          | switch. | not-swi. | total |

| inner<br>layer                                                        | power (W)   | 1,575   | 0,025    | 1,6            | 18,9    | 0,3      | 19,2           | 688 W   | 12 W     | 700 W |

|                                                                       | current (A) | 0,875   | 0,014    | 0,89           | 10,5    | 0,17     | 10,67          | OOO W   | IZ VV    | 700 W |

| outer<br>Layers                                                       | power (W)   | 0,490   | 0,010    | 0,5            | 5,88    | 0,12     | 6              | 382 A   | 7 A      | 390 A |

|                                                                       | current (A) | 0,272   | 0,006    | 0,28           | 3,27    | 0,07     | 3,33           | 362 A   | / A      | 390 A |

Average power (integrating pulsing) 20 to 30 W

→ Air cooling probably good enough

## Power pulsing & low mass cables

#### Wire bonds

- ✗ Average current through powering wires ~10 mA

- → Small residual force in B=4T but vibrations possible

- x Monolithic sensors are easy to handle

- → Possibility to embed in polyimide & connect through metallization

- → IMEC+CMST & CERN projects

# connection Metal traces kapton sensor profile view

Top view 1st trial of a MIMOSA embedded by IMEC

#### Lorentz force on low mass cable

- x Many "small" transverse traces

- → Residual force could reach few g ≈ cable mass!

- X Double-sided structure could be used to counter-balance the effect

- → Cable design with reverse current path on each side

- X Switching sensors with some delay and not simultaneously → reduce current

- → Require specific sensor functionalities

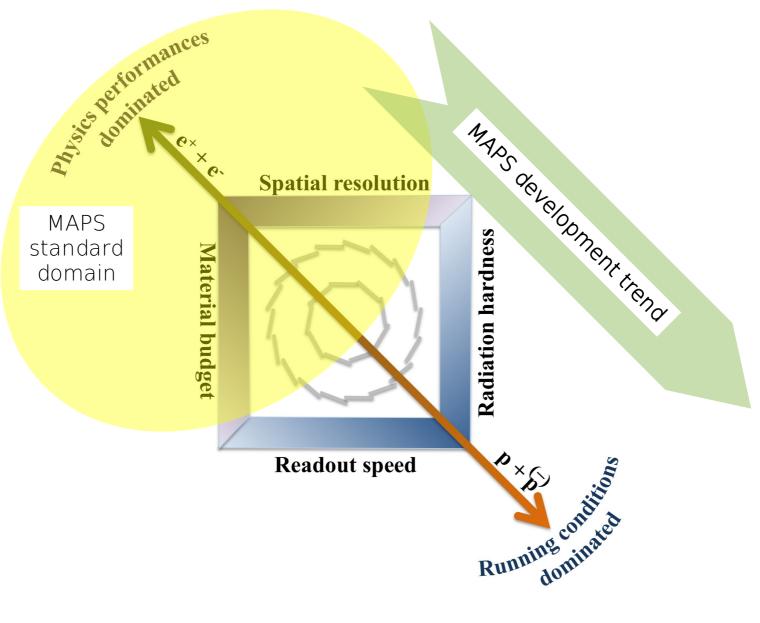

## Parameter space for a VXD