#### **DEPFET** active pixel detectors

Marcel Vos - IFIC Valencia

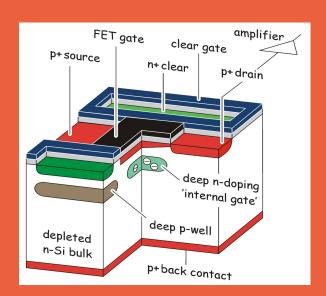

#### The DEPleted Field Effect Transistor

Fully depleted sensor with in-pixel amplification

Fast signal collection

Excellent noise performance

→ thin sensors!

Signal collected when pixel is "off" Low power consumption!

Clear the signal

DEPFE X

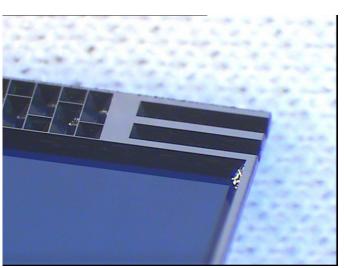

#### The all-silicon module

#### The all-silicon module

- Use anisotropic etching on bonded wafers to create a thin, self-supporting sensor

- Auxiliary electronics located on the sensors, signals routed in metal layer

- One material uniform (and small) thermal expansion

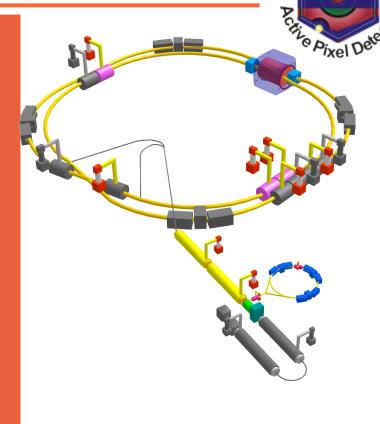

### Future colliders - ILC vs. Belle-II

Belle-II detector upgrade

4 layer DSSD →

2 layer pixels + 4 DSSD

challenges for the detector Watch your material budget!! 0.19 %X<sub>0</sub> in total (0.15 % Si)

**Building a complete system**

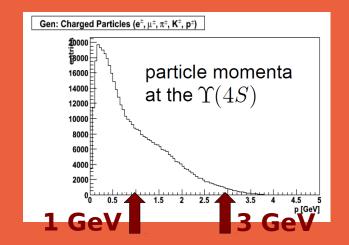

### ILC vs Belle-II

|                | ILC                                                                                      | Belle-II                                                                                                  |  |

|----------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| occupancy      | 0.13 hits/μm²/s                                                                          | 0.4 hits/μm²/s                                                                                            |  |

| radiation      | < 100 krad/year                                                                          | > 1Mrad/year                                                                                              |  |

| Duty cycle     | 1/200                                                                                    | 1                                                                                                         |  |

| Frame time     | 25-100 μs                                                                                | 10 μs                                                                                                     |  |

| Momentum range | All momenta                                                                              | Low momentum (< 1 GeV)                                                                                    |  |

| Acceptance     | 6°-174°                                                                                  | 17°-150°                                                                                                  |  |

|                | Excellent spatial resolution (3-5 μm) AND material budget (0.12 % X <sub>0</sub> /layer) | Lowest possible material<br>budget (0.15 % X <sub>0</sub> /layer)<br>Moderate pixel size<br>(50 x 75 μm²) |  |

Belle-II presents a more severe challenge than the ILC in several aspects!

#### Future collider - ILC

#### **VXD:** impact parameter resolution $5 - 10 \mu m$ .

This precision is required to achieve excellent heavy flavour tagging, particularly for couplings of the Higgs boson to charm ( $c\tau \sim 150 \mu m$ ) and bottom ( $c\tau \sim 450 \mu m$ )

|     | a (μm) | b (μm GeV) |  |

|-----|--------|------------|--|

| LEP | 25     | 70         |  |

| SLD | 8      | 33         |  |

| LHC | 12     | 70         |  |

| ILC | 5      | 10         |  |

(small pixels, 20x20 µm²) Coulomb scattering term

(material: 0.1 %  $X_0$  / layer ~ 100  $\mu$ m Si)

To meet the resolution requirement ILC DEPFETs need small pixels (order 25x25  $\mu$ m<sup>2</sup> pixels, Belle-II pixels are 50x75  $\mu$ m<sup>2</sup>).

The feasibility and performance of small pixels have been demonstrated long ago, but long columns put pressure on the read-out speed

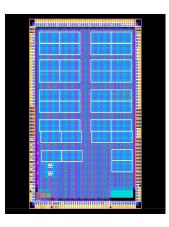

# The sensor: PXD6 production

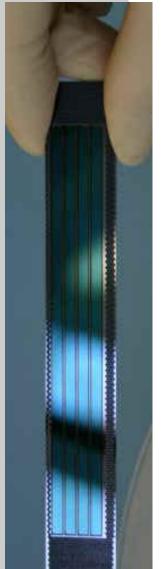

### **50 μm thin DEPFETs!**

PXD6 production was split before the 1<sup>st</sup> metal layer:

- batch 1 (4 wafers, 3 SOI) finished, 3 wafers cut, one wafer repaired with many shorts

- batch 2 (4 wafers, 3 SOI) finished,2 wafers repaired & cut, matrixcharacterization ongoing

- batch 3 (2 SOI wafers with DHP footprint), partially processed

| Yield          | Batch I                                | Batch II (after repair)                | Batch III                           |

|----------------|----------------------------------------|----------------------------------------|-------------------------------------|

| Small matrices | 30%                                    | 99%                                    | 98%                                 |

| Half ladders   | ~6% (1/16)<br>(after Al1 6.25% - 1/16) | 25% (4/16)<br>(after Al1 100% - 16/16) | 50% (4/8)<br>(after Al1 100% - 8/8) |

Measuremtents of full size matrices started

### The sensor: PXD9 production

cādence

X: 27515 Y: 81820 (FS)Select: 0 Sel(N): 0 DRD: OFF CAE: OFF dX: dY: Dist: Cmd

|| 🏲 🔒 || 🥱 🥜 🚸 🗓 🔟 🗶 🕦 🕕 || 🔞 😥 🖄 🧠 🔻 " || 🔍 » || 🤻 » || Workspace: Classic

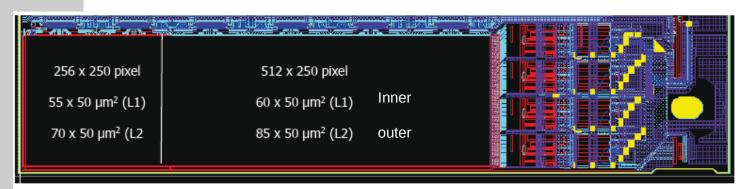

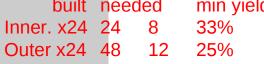

Original Plan (Nagoya, July 2012): Production with 2x6 wafers for Fast Prototype run, to be followed by main production

2 inner modules

4 outer modules

- ⇒1 inner ladder

- ⇒2 outer ladders

built needed min yield 33%

Last PXD6 batch: ~ 50%

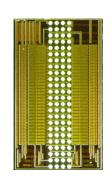

### The ASICs are ready!

The full-size close to final versions of the ASICs are designed, produced and found to work.

DCDBv2 (some excess noise is to be understood, but still better than v1) SWITCHERBy1 and SWITCHERB18

DHP02 (in 90nm IBM technology) NEW (but needs to be redesigned for TSMC 65nm). The layout of the module periphery has been done as well

DCDBv2 180nm UMC (Heidelberg)

**SWITCHERB** (Heidelberg)

**SWITCHERB18** 350nm HV AMS 180nm HV AMS

**DHP0.2** 90nm IBM

(Bonn with help from Barcelona)

Milestone!

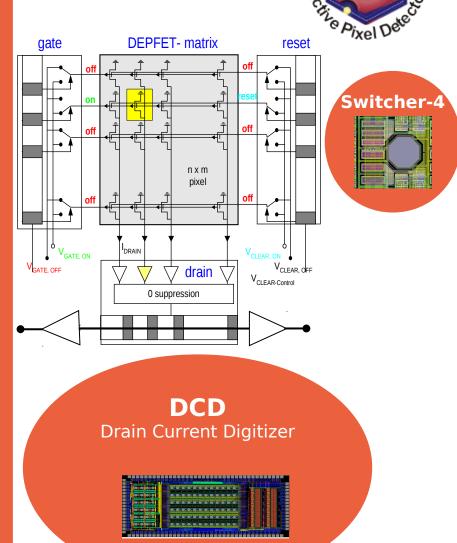

### **Drain Current Digitizer - DCD**

- 0.18 µm technology

- regulated cascode

- current memory cells

- two 8-bit algorithmic ADCs

- 6:1 multiplexed LVDS outputs

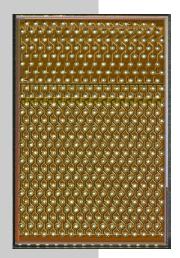

- bump bond IOs + wire bonds for testing

### **Measured performance**

Fully functional at 600 MHz clock-speed Noise at 12.5 MHz:

0.6 – 1 LSB (w/o cap. input load)

< 2 LSB with up to 82 pF load

Input range: [0..24μA] (19 MIPs @ 50 μm)

LSB: 100 nA (higher than designed)

Gain:  $10 \pm 0.1 \, LSB / \mu A$

Power: 6 mW/channel

DACs & control

6 x 12 input channels

University of Heidelberg

6 x 2 output drivers

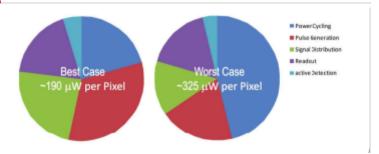

#### Thermal issues

Carlos Mariñas, thesis U. Valencia, CERN-THESIS-2011-101

#### System issues

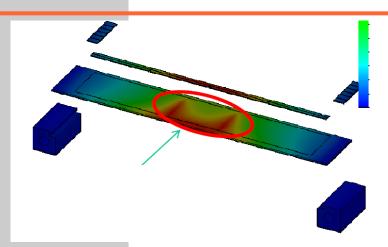

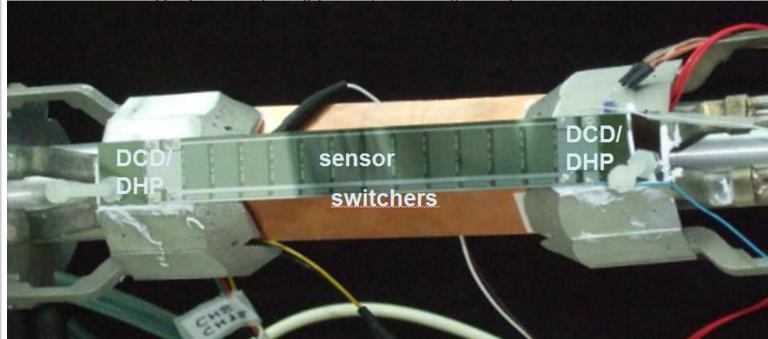

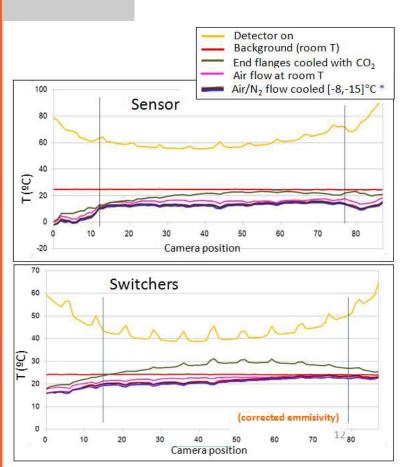

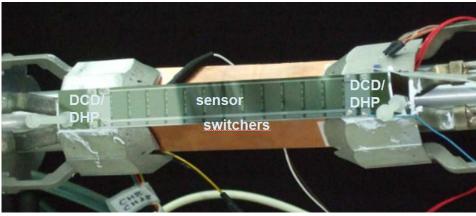

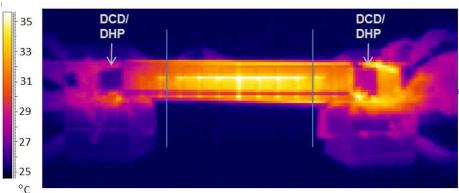

Cooling/mechanics are being addressed for Belle-II by a combination of measurements on a mock-up and simulations.

Belle-II; combination of liquid and air cooling required to remove power dissipated by DCDs, switchers and sensor ILC; only air cooling to remove much-reduced heat load

### Thermal performance

The key element: mechanical "dummy" sensor: mechanically identical to the real thing, but with circuits designed as "heaters" in the metal layer

Integrate into Belle-II detector mock-up at IFIC Valencia with realistic supports

and complete set of cooling options (CO plant, cold N flow)

### Thermal performance

## Look at the detector at a different wave length

Confirm Finite Element studies: Modest (1 m/s) air flow needed and sufficient to cool sensor center A. Oyanguren, LCWS11

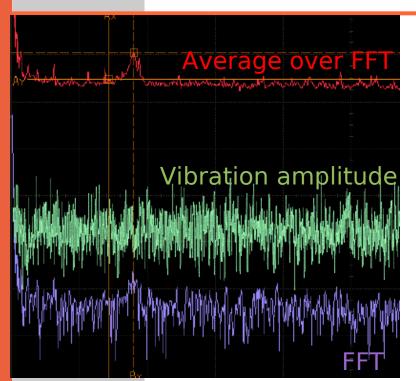

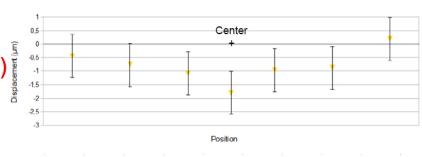

## Mechanical impact of air cooling

Capacitive sensor (Micro-epsilon Capa NCDT 6100) and piezo-electric accelerometer (3PCB Piezotronics model 352A24)

A peak at ~400 Hz (depending slightly on position, orientation) appears for gas flow with a pressure greater than 4 bar

#### **Deformation:**

$2 \mu m$  for nominal gas flow of 2 m/s, up to 8  $\mu m$  for max. pressure (10 bar)

### Vibration @ 400 Hz:

Amplitude =  $0.7 \mu m$  (nominal) Amplitude =  $1.2 \mu m$  (max.)

Deformation for cooling conditions (2 m/s)

## ILC-specific thermo-mechanics

#### Thermal load & cooling concept very different at the ILC

- Power pulsing; exercised at XFEL (MPI/Heidelberg)

- → derive realistic duty cycle

- ✓ Finite Element analysis set up (Bonn)

- preliminary results look good

- ✔ Port Belle-II mockup to ILC (IFIC Valencia)

- → light supports/gas cooling

- Existing infrastructure for thermo-mechanical characterization will be extended within AIDA (DESY, Saclay, Oxford, IFIC, IFCA)

- → similar plans exist at CERN and elsewhere

- → Integrate IFIC Bragg fiber system

Hands-on power pulsing experience for DSSC at XFEL: completely shutting down the DEPFET and the analogue part of the electronics between bursts (~1ms burst, ~100ms gap). The total power consumption is reduced to 1/25.

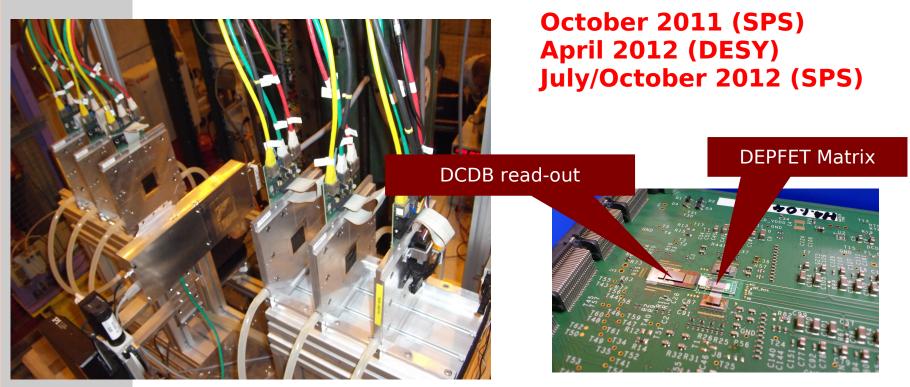

#### Beam tests

### **Devices Under Test:**

**ILC** design

450 μm thick, small-pixel ILC design sensor **Three PXD6 devices**

- Belle-II design (50 x 75 and 50 x 50  $\mu$ m)

- Sensors thinned to 50 μm

- DCDB read-out 100 or 320 MHz

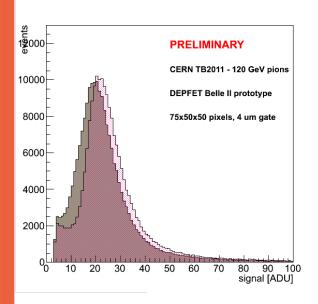

### Result

#### **Most Probable Signal:**

S/N ratio ~ 20 - 40

TB2011 confirms the expected dependence on DEPFET parameters: gate length, oxide thickness

TB2012 → offset current subtraction from DCDBv2

### S/N on Belle-II design ~ 40

- S/N = 60 with 75  $\mu$ m sensor

- Using conservative 5 μm gate length

Within errors of expected ratio

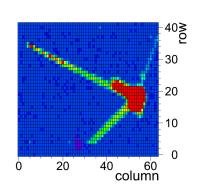

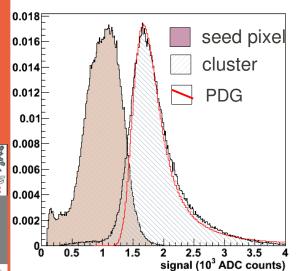

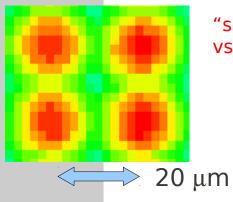

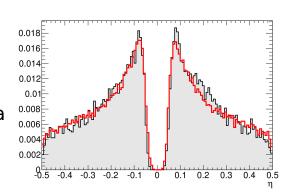

### Charge collection

Charge collection from DEPFET is extensively studied in 7 years of beam tests, mostly on ILC design sensors

"seed" pixel signal vs. position

η distribution in data And digitizer

#### A detailed digitizer exists

- in ILC software

- validated using TB data

Increased realism in DBD: Evaluate

technology-specific performance in ILC?

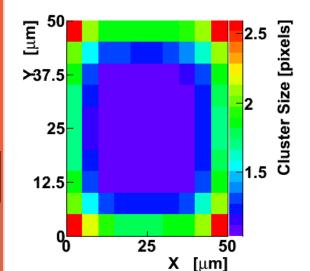

Cluster size vs. in-pixel position for a Belle-II design sensor

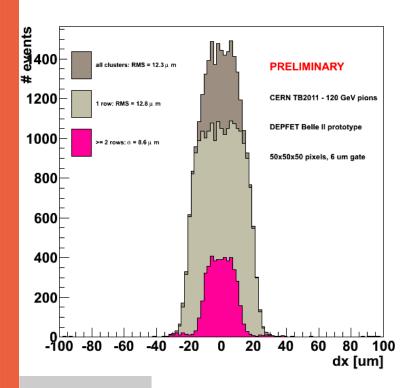

### Spatial resolution

Spatial resolution of module H4.1.04, Belle-II design

DEPFE ,

Single-pixel cluster show expected "box" distribution from -25 to  $\pm$ 25 µm,

- smearing by telescope resolution  $\sim$  2-3  $\mu$ m

- binary RMS = 50  $\mu$ m /  $\sqrt{12}$  = 14.4  $\mu$ m

Multiple-pixel clusters are relatively rare under perpendicular incidence

Spatial resolution depends on incidence angle, S/N, clustering (esp. 0-suppression), bias voltage (scan under analysis)

## Summary

# The DEPFET collaboration is developing pixel sensors with integrated amplification

- ✔ Performance in terms of spatial resolution, sensor material and power consumption well-established

- Applications: transparent and precise VXD for Belle-II and ILC

- Build a real system: auxiliary electronics development, cooling/mechanics

- Small, but steady effort to produce a backup document for the DBD with ILC-specific results