# Tracking with Monolithic Pixel Sensors in SOI Technology

IWLC2010 Geneva, 18-22 October 2010

Marco Battaglia

UCSC, Lawrence Berkeley National Laboratory and CERN

with D Bisello, D Contarato, P Denes, P Giubilato, TS Kim, S Mattiazzo, D Pantano, S Zalusky (LBNL, INFN & Univ. Padova, UCSC)

> in collaboration with Y Arai (KEK) and the SOIPIX Collaboration

## Monolithic SOI Pixel Sensors

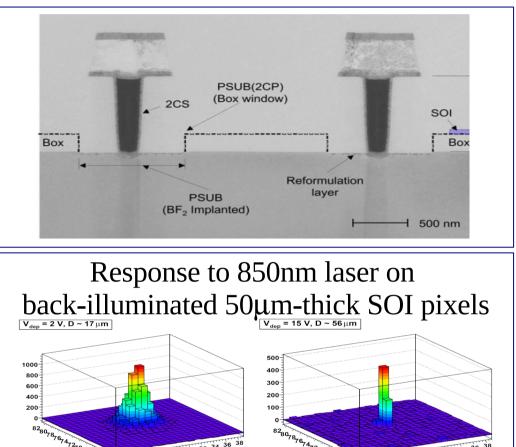

Silicon-On-Insulator technology isolates CMOS from high-res charge collection volume offering full CMOS capabilities, low junction capacitance,potentially radiation tolerant: KEK-OKI offer 0.2µm FD-SOI process with vias through BOX to contact high-res substrate:

Thick fully depleted substrate gives large collected charge, faster collection time and small charge spread compared to conventional CMOS APS on low-res epi:

Results of first pixel detector test structures in OKI SOI technology encouraging but two main issues emerged: transistor back-gating and charge trapped in thick BOX

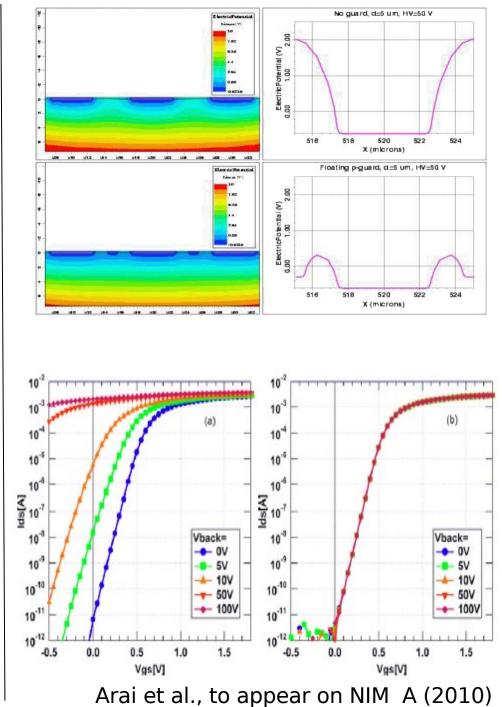

Transistor back-gating

Substrate potential acts as back-gate shifting transistor threshold and increasing leakage current:

- Floating p-type guard-ring around pixel

- Buried p-well

- SOI-3D: vertical integration of r/o electronics

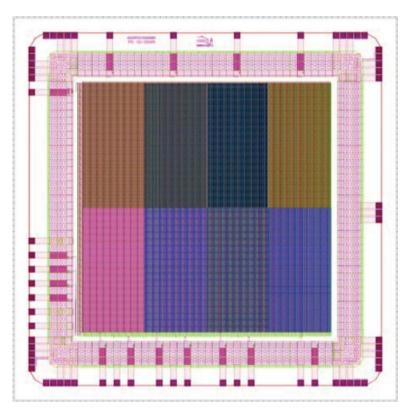

## SOImager2 Pixel Sensor

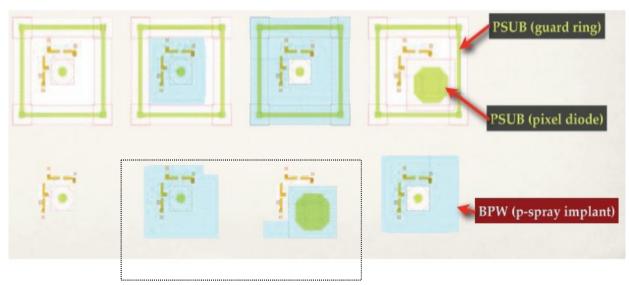

Test chip to optimise pixel cell for charge collection and back-gating effect mitigation;

Study performance of various pixel designs with guard ring and light-doped p implant (BPW);

256x256 (3T) pixels arrayed on a 13.75  $\mu$ m pitch;

Designed at LBNL and produced at OKI in 0.2µm FD-SOI process in Spring 2010 as part of US-Japan collaboration on SOI pixel R&D.

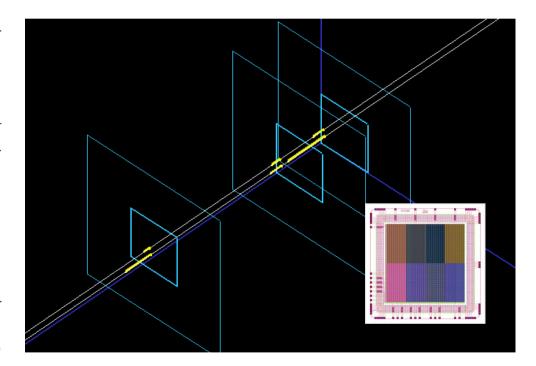

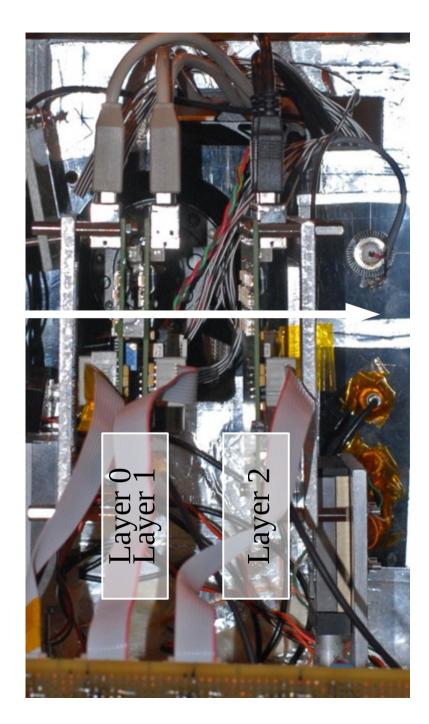

### **CERN Beam Test Setup**

Beam test at SPS on H4 with 200 GeV  $\pi$ at beginning of September 2010;

Small telescope made of three planes of SOImager2 to study charge collection, single point resolution and efficiency as function of depletion voltage, one plane mounted on motorised rotation stage to study charge collection for inclined tracks;

Data acquisition performed using custom ADC+FPGA board, online cluster search using ROOT-based COOL program, tuple output converted to lcio, offline analysis performed with custom processors in Marlin;

Readout at 12.5 MHz corresponding to ~1500 frames/spill, operation at constant temperature (20+/-1)°

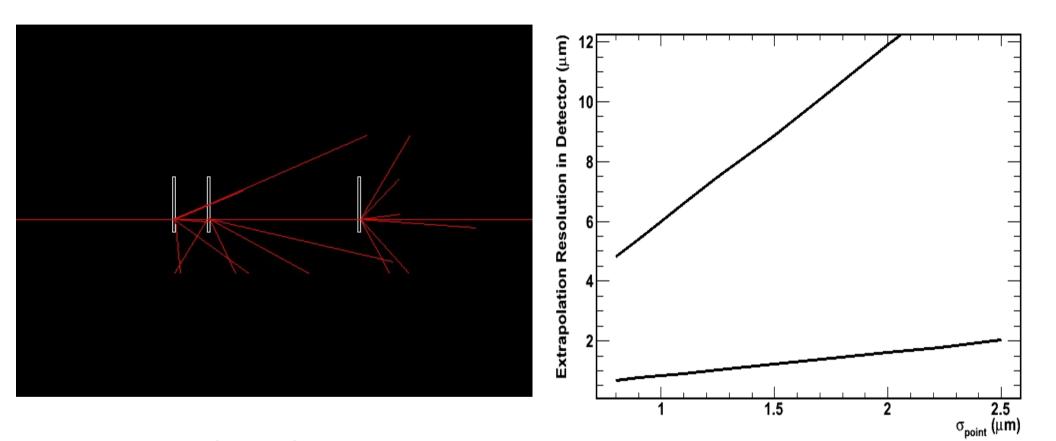

#### Beam Test Setup G4 Simulation

Generate lcio files of simulated SimTrackerHits and MCParticles to test reconstruction and extrapolation resolution;

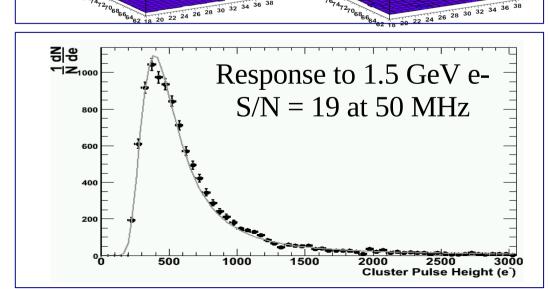

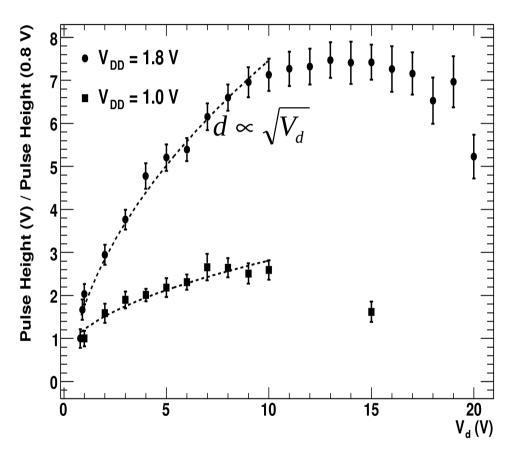

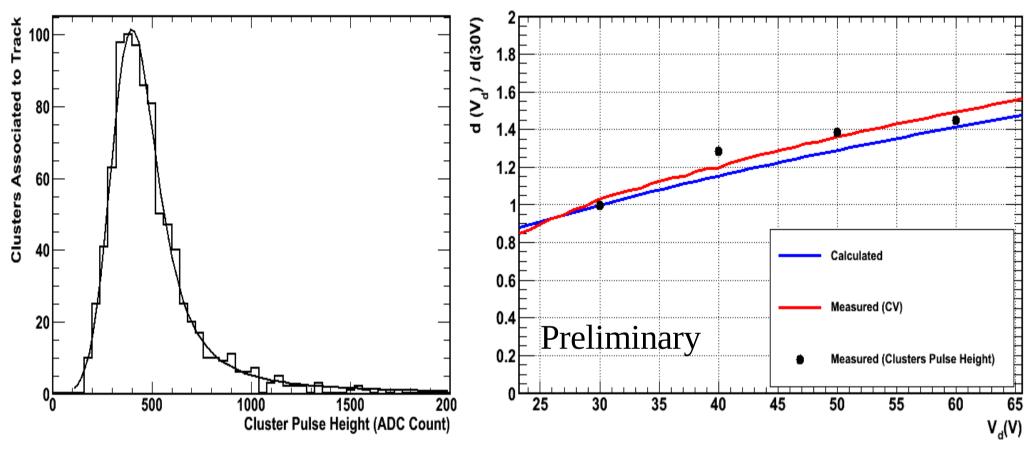

## Beam Test Results: Charge Collection and Depletion Voltage

Cluster reconstruction using double S/N threshold (seed and neighbouring pixels) (seed S/N > 10 and  $N_{pixels} > 1$ )

<u>Calculated</u> depletion from nominal resistivity (200  $\Omega$  cm);

<u>Measured (CV)</u> from CV measurement of the substrate using pixel guard ring as electrode <u>Measured (PH)</u> from signal in cluster pulse height for hits associated to reconstructed track

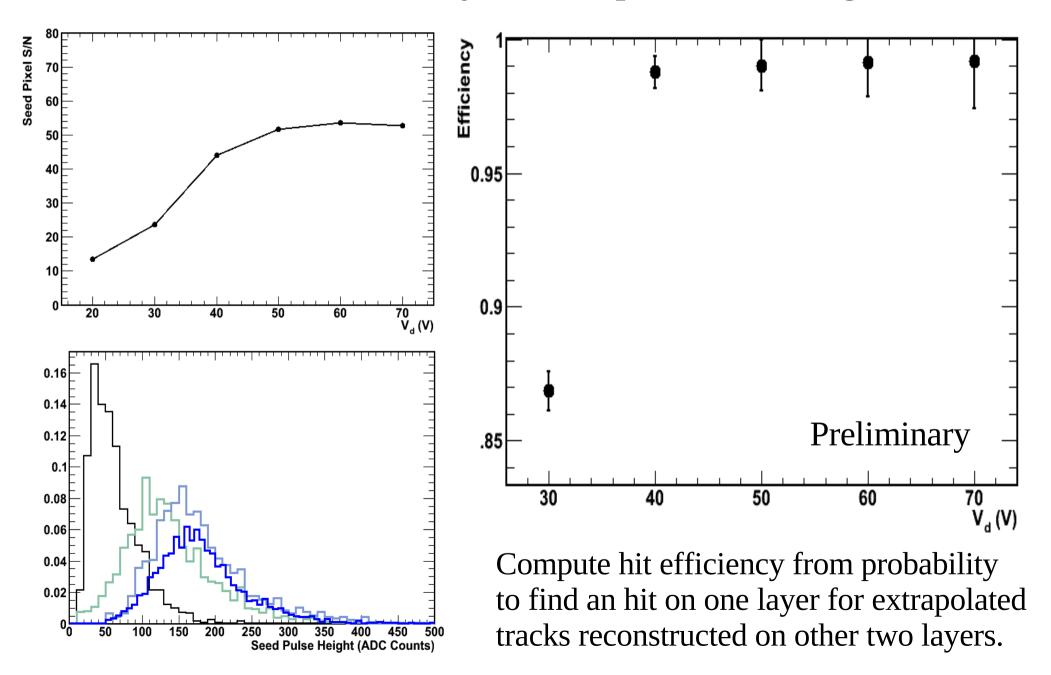

#### Beam Test results: Sensor Efficiency and Depletion Voltage

#### Single Point Resolution

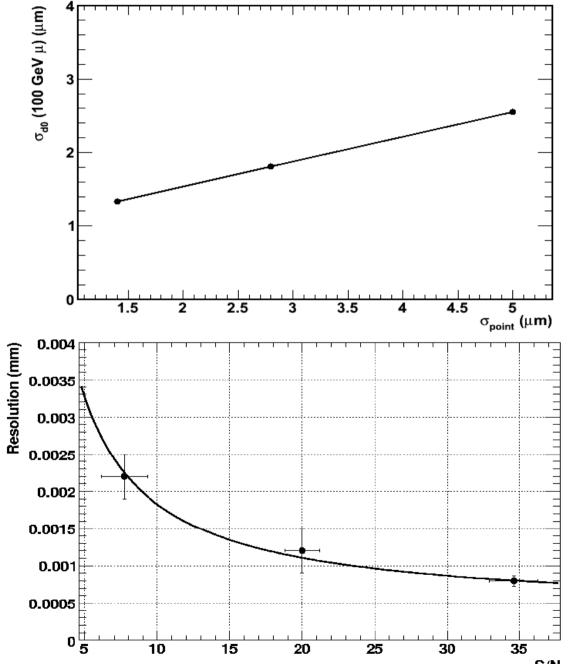

Scaling of asymptotic R-Φ impact parameter resolution (a) with single point resolution for a three double-layered barrel VXD in the CLIC geometry (100 GeV single muons with Mokka+MarlinReco);

First estimate single point resolution by performing pixel scans on SOImager chip with 1060 nm laser focused to ~5 µm spot at various intensities to simulate m.i.p. charge deposition;

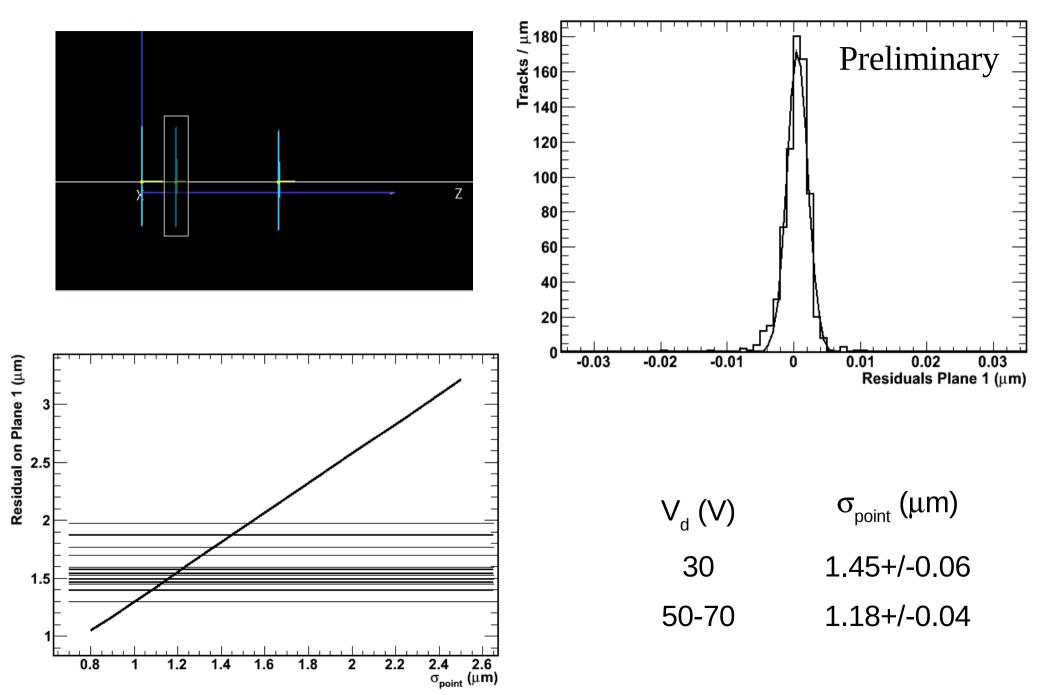

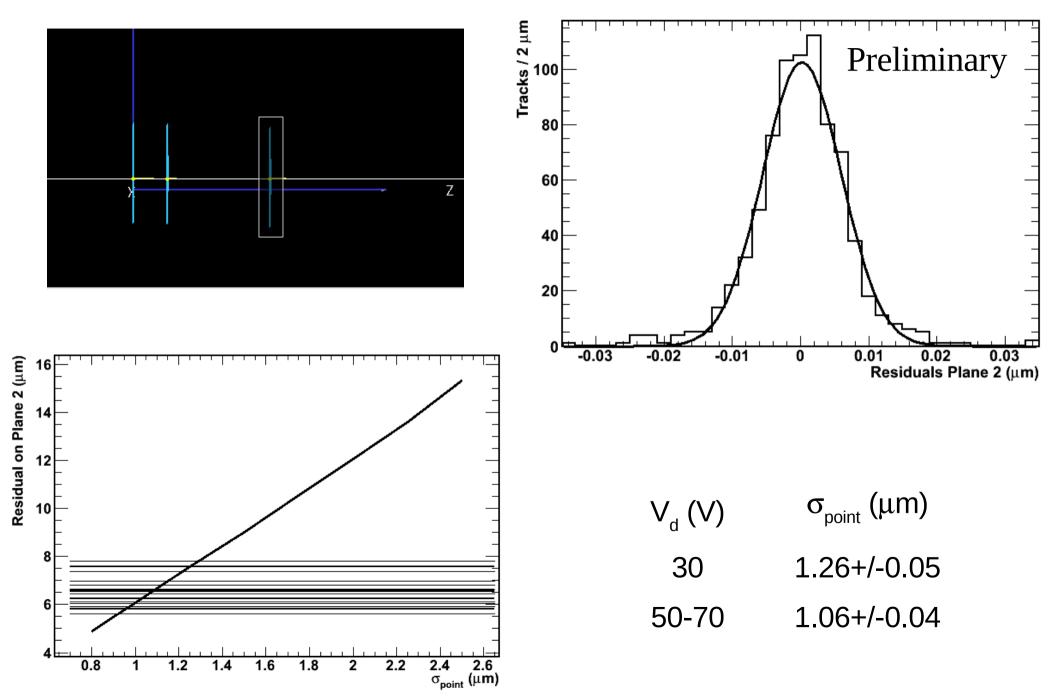

## Beam Test Results: Single Point Resolution

## Beam Test Results: Single Point Resolution

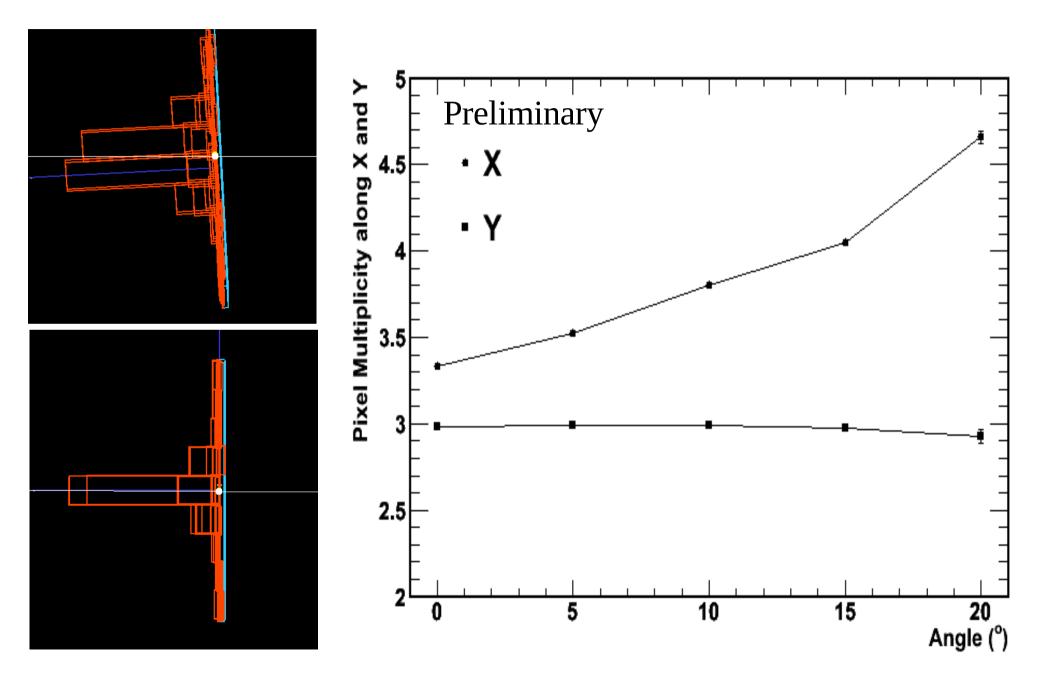

## Beam Test Results: Cluster Size for Inclined Tracks

## Conclusions

The fourth in the series of test chips in OKI SOI technology has been designed at LBNL and tested by a collaboration including LBNL, INFN, Padova and UCSC;

Several pixel cell designs adopting both guard ring and buried-p-well have been implemented and evaluated;

Three sensors installed on the SPS H4 beam line and tested with 200 GeV  $\pi^-$  to study charge collection, efficiency and resolution vs. depletion voltage;

Efficiency > 98% and single point resolution ~1.2  $\mu$ m obtained for 40 < V<sub>d</sub> < 70 V

Study of charge collected on pixels as a function of point of impact of particles for straight and inclined tracks in progress;

Encouraging results motivate next steps towards implementing in-pixel and on-chip functionality;

Role, advantanges and limitations of SOI technology compared to CMOS on high-res sensitive volume and 3D vertical integration sensors to be assessed as part of this R&D.