# **ROC chip status**

S. Callier, S. Conforti, L. Raux, F. Dulucq, C. de La Taille, G. Martin-Chassard, N. Seguin-Moreau

Orsay Micro Electronics Group Associated

Many measurements are still on going on test board and at system level to characterize in detail the ROC chips before submitting 3rd generation chips

- HARDROC3: will be submitted in Feb 2013

- Many measurements performed on SKIROC2 (see Stephane's talk) and on SPIROC2B and 2C

- SKIROC2 and SPIROC2B/2C are the same except for the input preamplifier: same fast and slow channel, same digital part.

mega

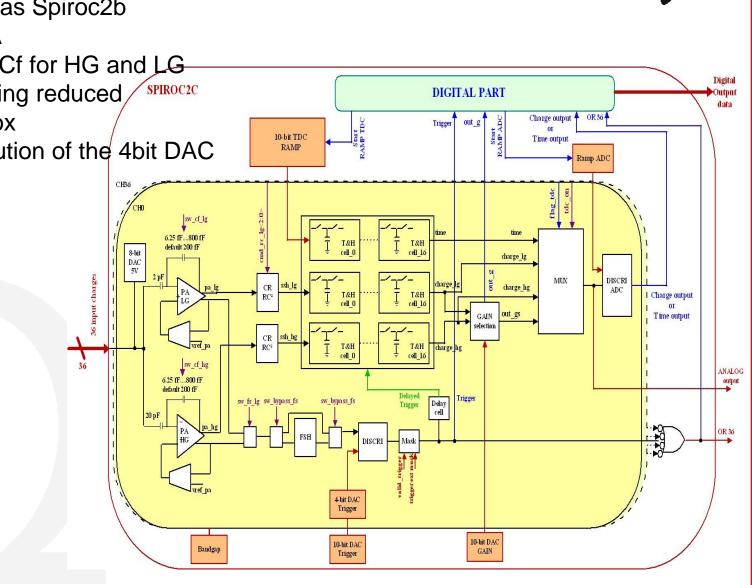

# SPIROC2C

- Same pinout as Spiroc2b

- New input PA

- Independant Cf for HG and LG

- HG/LG coupling reduced,

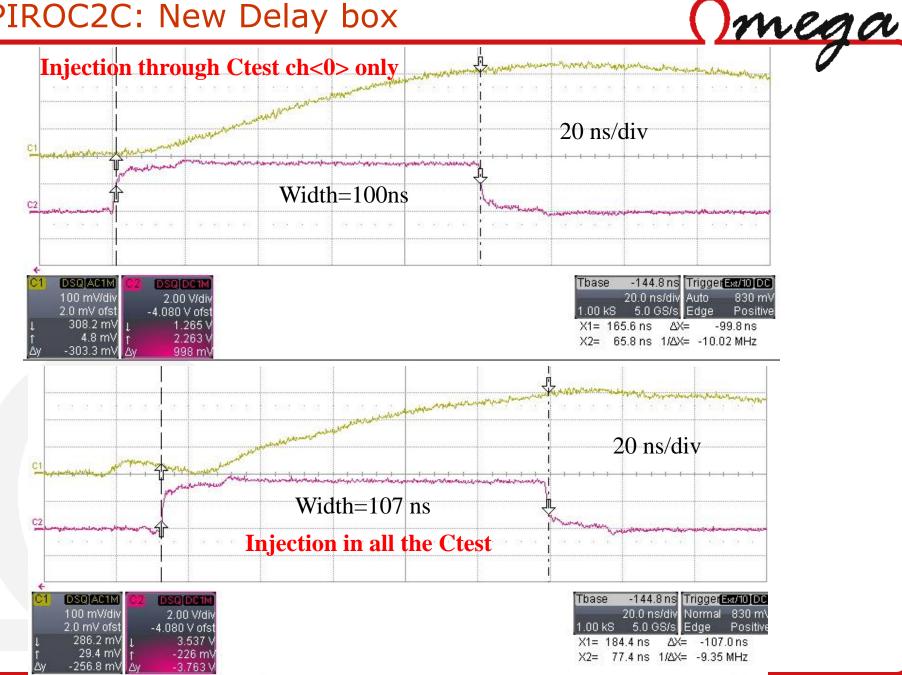

- New delay box

- Better distribution of the 4bit DAC

#### DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

<u> Mega</u>

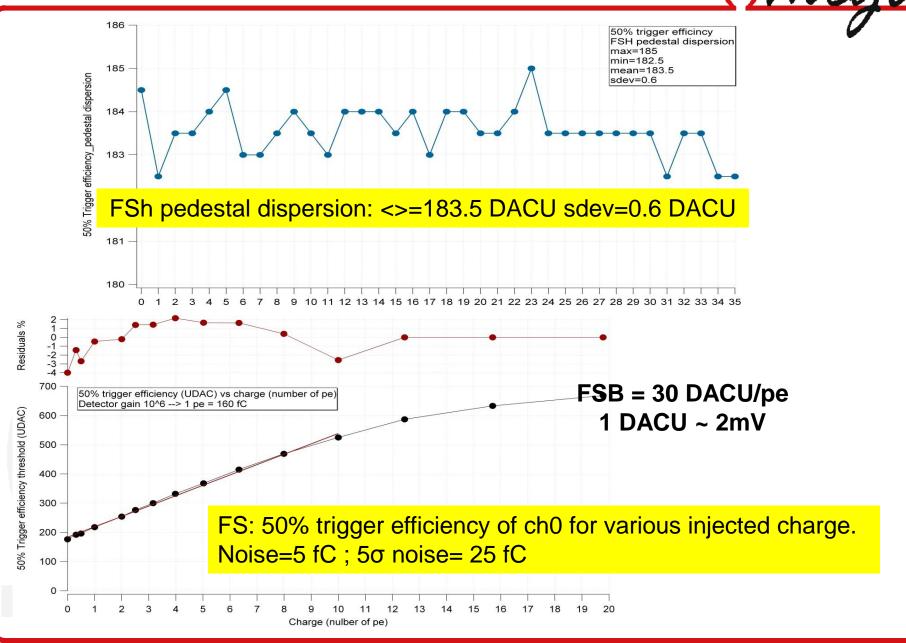

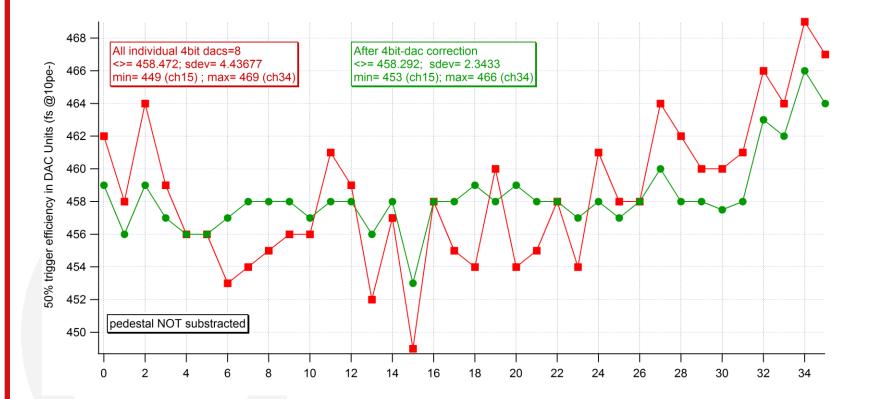

# SPIROC2C: FS Uniformity (HG=200; LG=100) mega

SPIROC2C: 4-bit DAC channel wise tuning

#### FS@ 10 pe injected

DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

<u>(mega</u>

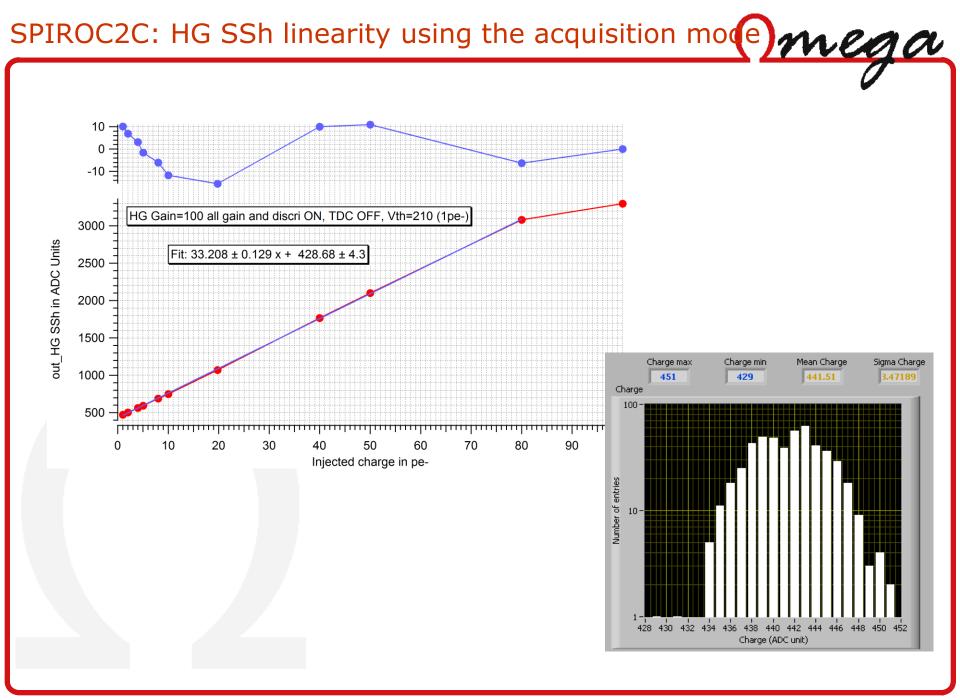

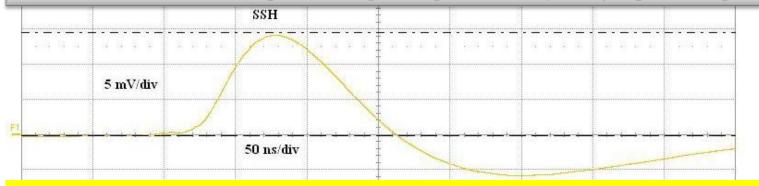

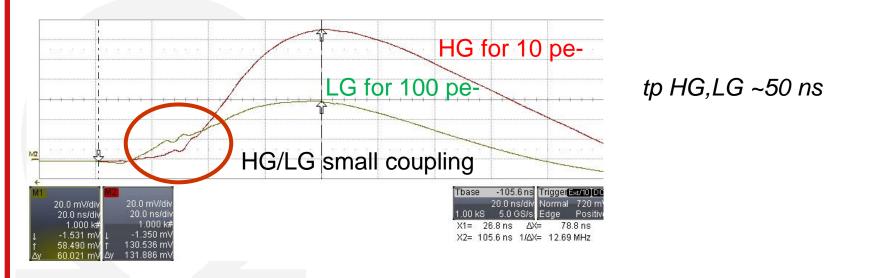

#### **SPIROC2C: HG and LG slow shapers**

PA\_HG=bit100 x 6.25fF=  $625fF => G=20pF/625fF= 32 => dyn range up to 100 pe-PA_LG=bit200x6.25 fF=1.25pF => G=2pF/1.25pF= 1.6 => dyn range up to 1500 pe-$

HG SSh: Vmax= 14.65 mV/pe (1pe=160 fC) RMS noise =  $1.2mV = SNR \sim 12$

mega

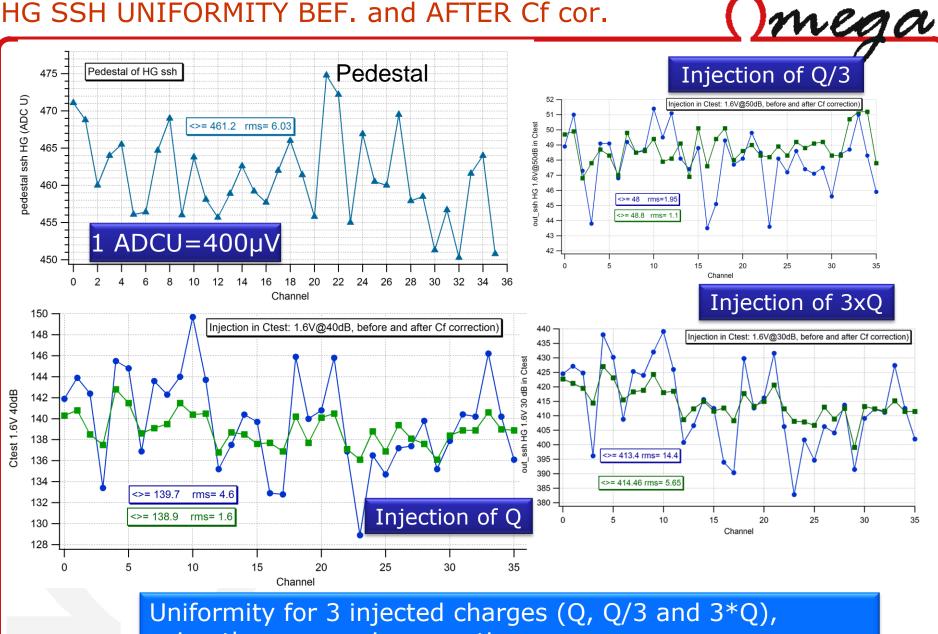

#### HG SSH UNIFORMITY BEF. and AFTER Cf cor.

using the same gain correction

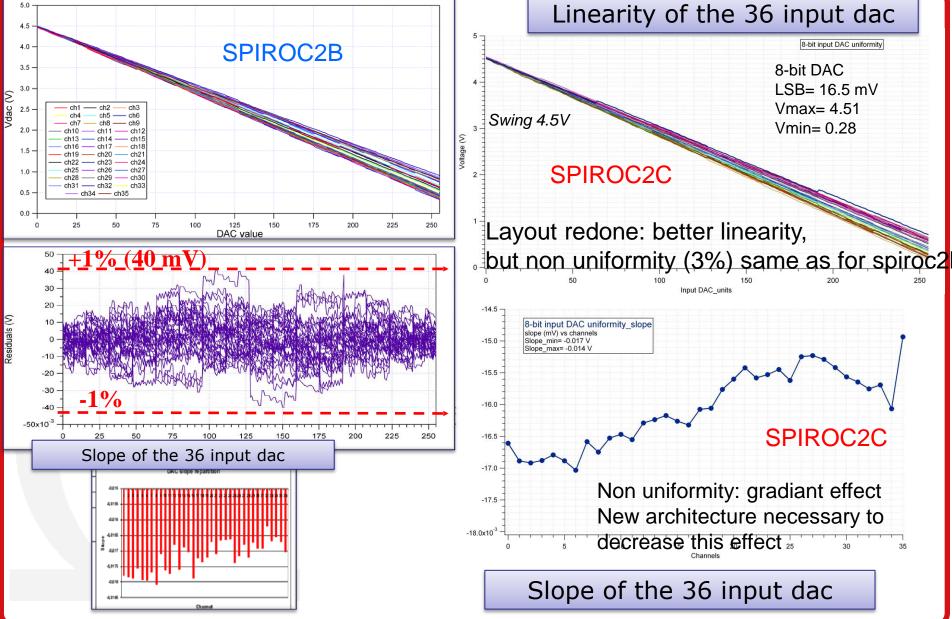

## 8-bit input DAC linearity

<u> Meaa</u>

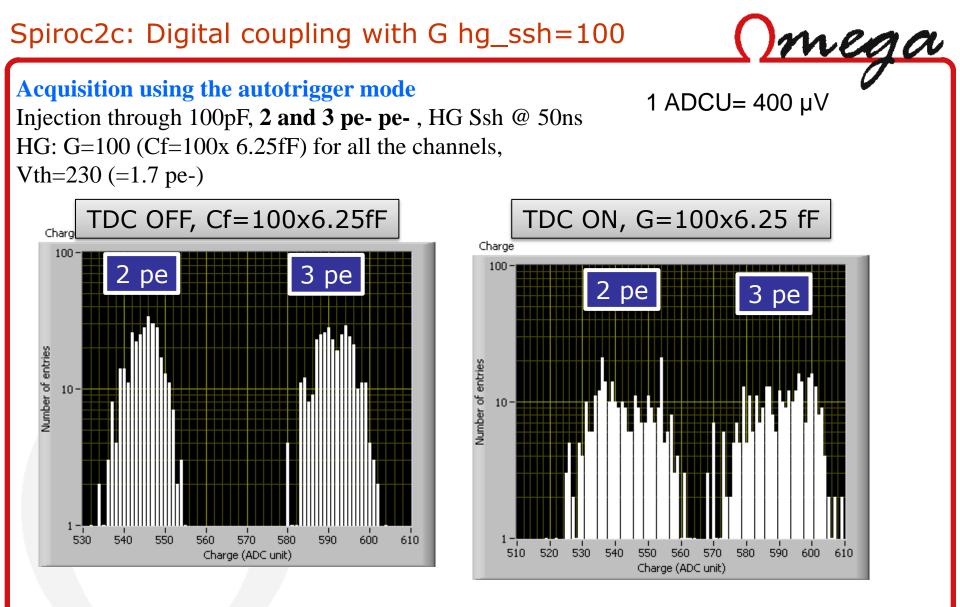

TDC => digital coupling in spiroc2c through the substrate (NMOS preamp connected to gnd) There is no digital coupling in spiroc2b (PMOS transistor connected to vdd)

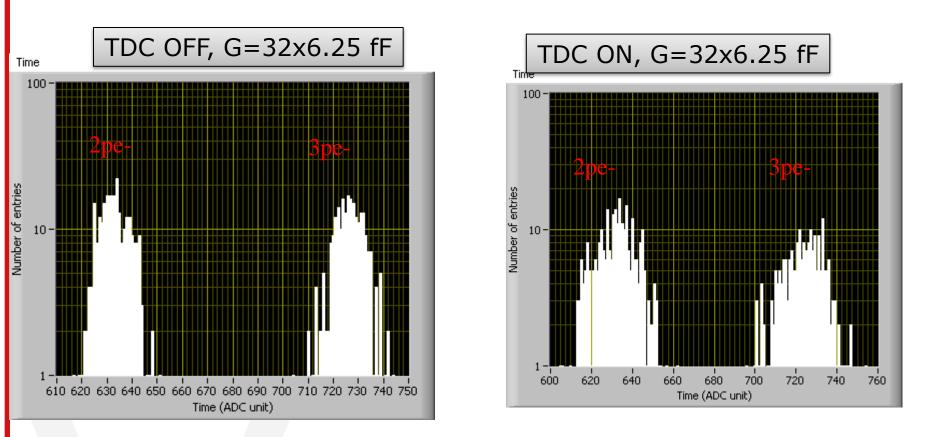

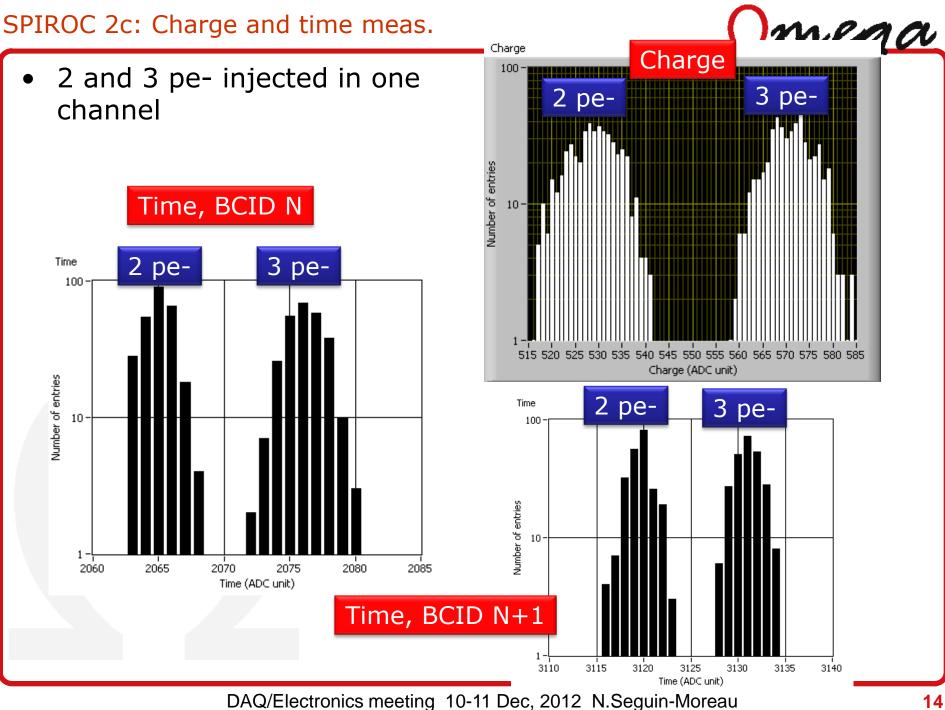

#### Digital coupling in Spiroc2c with G hg\_ssh=32

Injection through 100pF, **2 and 3 pe- HG with G=32** (**32x6.25fF**) for all the channels, ssh@50n Vth=260 (~1pe-)

#### TDC coupling in Spiroc2c doesn't prevent to distinguish 2 and 3 pe-

DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

mega

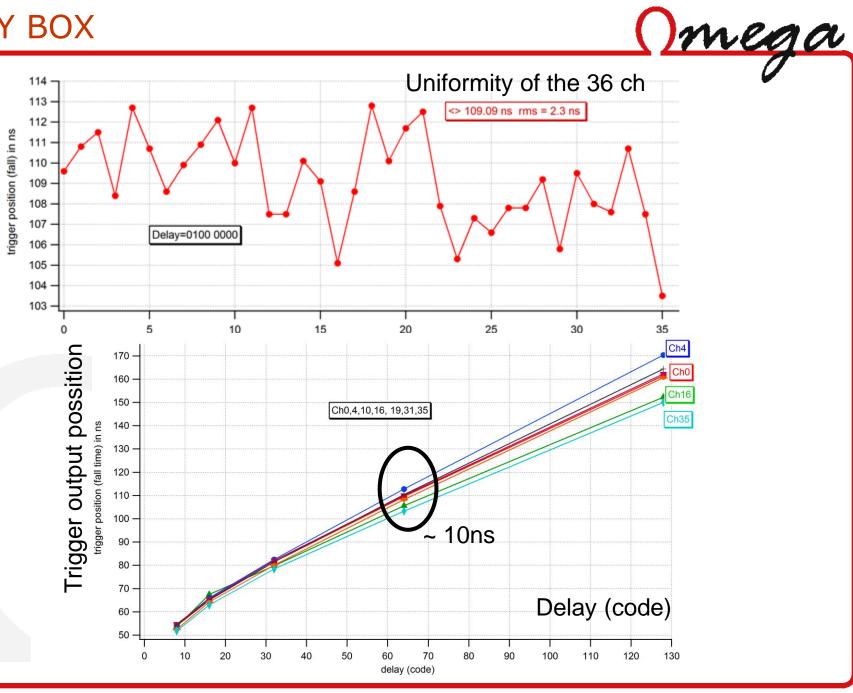

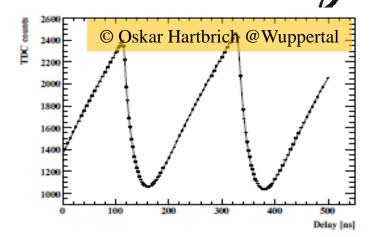

### **DELAY BOX**

#### SPIROC 2c: TDC

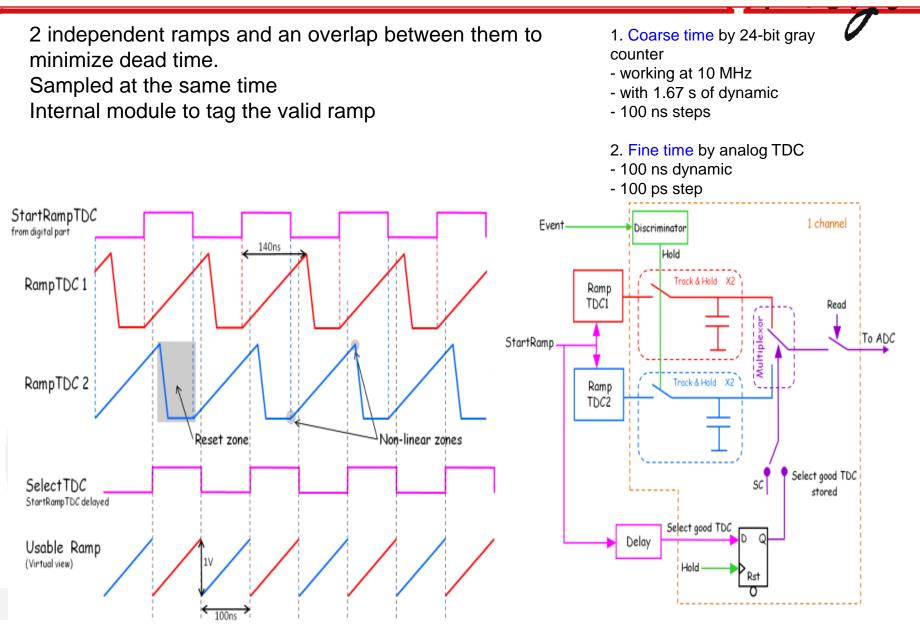

- SPIROC2B TDC: Dead time due to the mutiplexer

- SPIROC2C TDC

- To decrease dead time during transition

=> alternation of a rising and a falling ramp implemented

- Conservative modification

()mega

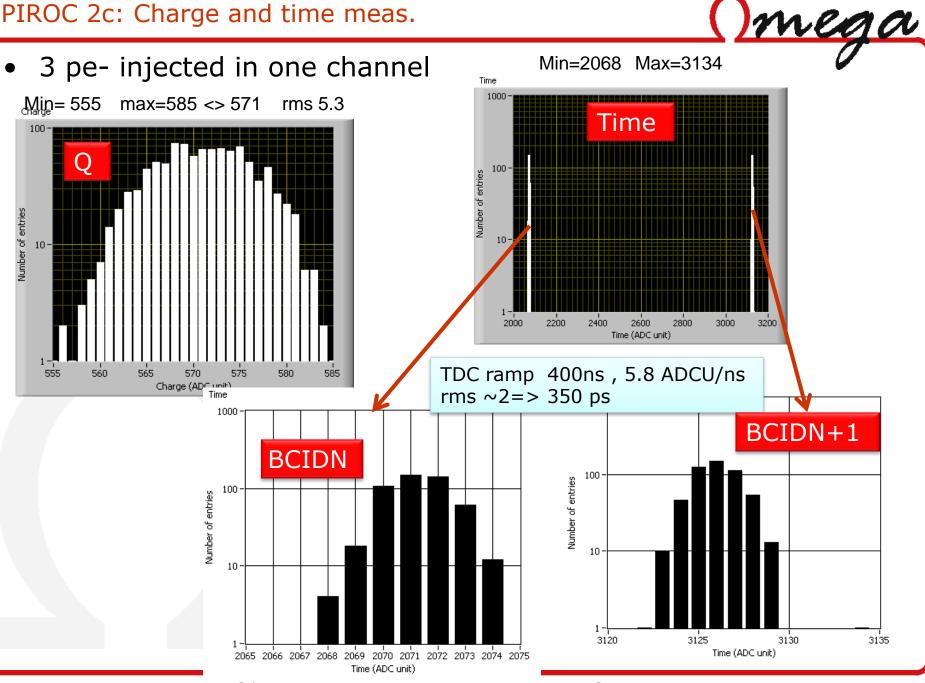

#### SPIROC 2c: Charge and time meas.

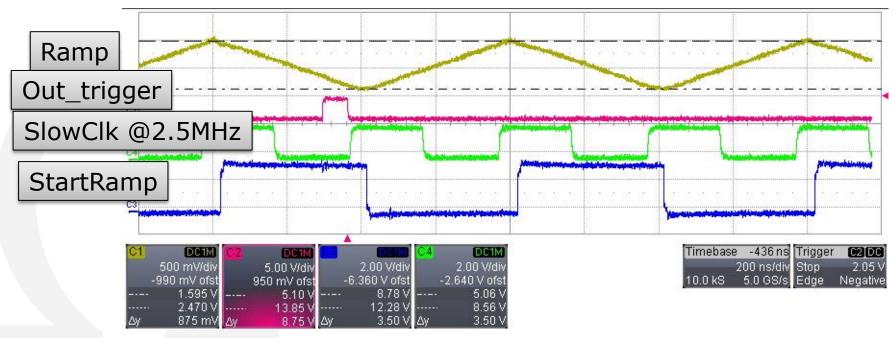

## TDC for SPIROC3: PARISROC TDC ramp ?

tested by IPNO team

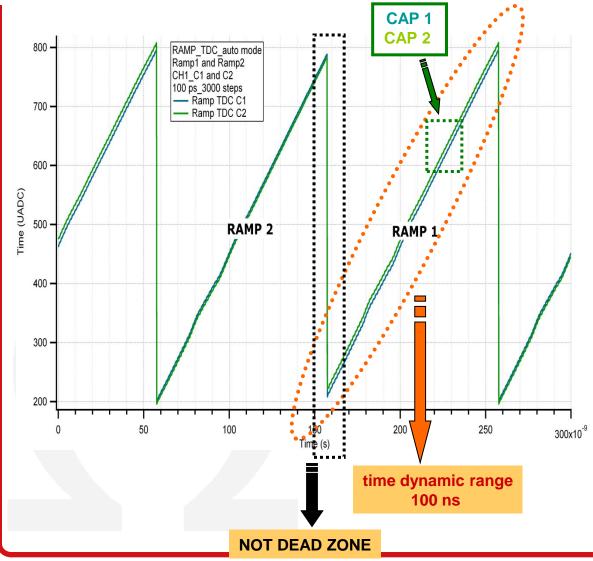

# **PARISROC TDC ramp**

Reconstruction of the ramp from the time values saved in the analog memory and converted by the ADC (10-bit).

The validation of the good ramp is made automatically

|                       | Second version |  |  |

|-----------------------|----------------|--|--|

| Time<br>dynamic range | 100 ns         |  |  |

| "Blind zone"          | 0              |  |  |

| linear zone           | 100 ns         |  |  |

| Ramp 1 linear         | ±1ns           |  |  |

| Ramp 2 linear         | ±1ns           |  |  |

# SPIROC3

#### **Complex chip (internal SCA, ADC, TDC)**

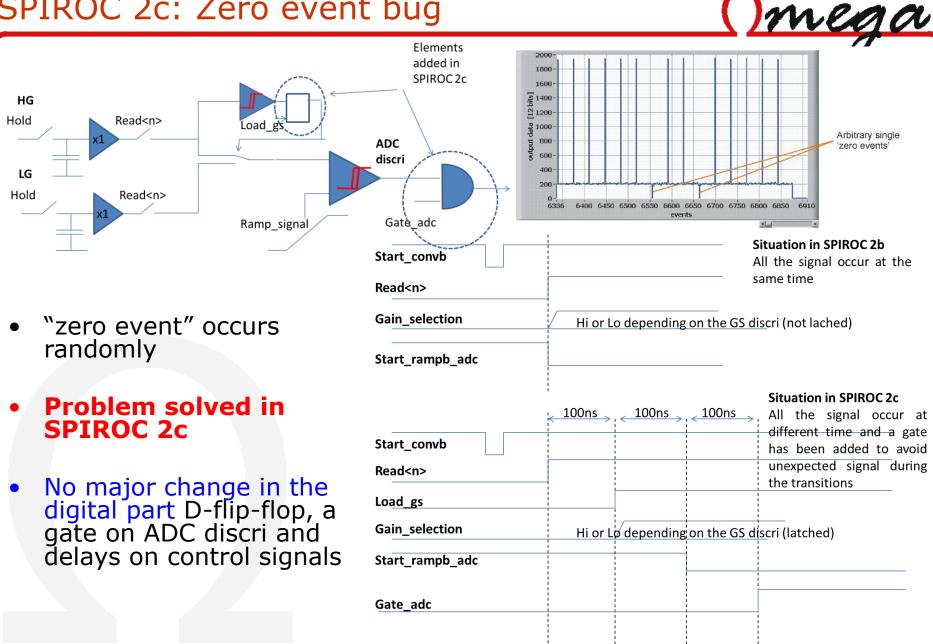

- Many bugs corrected + new features in SPIROC2c:

- HG/LG coupling

- Independent Cf for HG and LG

- 4-bitsDAC

- Delay box

- Rate dependency

- Pedestal shift (to be checked by DESY)

- Zero events

- Still improvements to be done:

- 8-bit input DAC: to be improved

- NMOS or PMOS preamp? = digital coupling vs pedestal shift

AIDA

<u>()mega</u>

- TDC

- HBU with spiroc2c to be tested

- I2C link: feedback from HR3 necessary

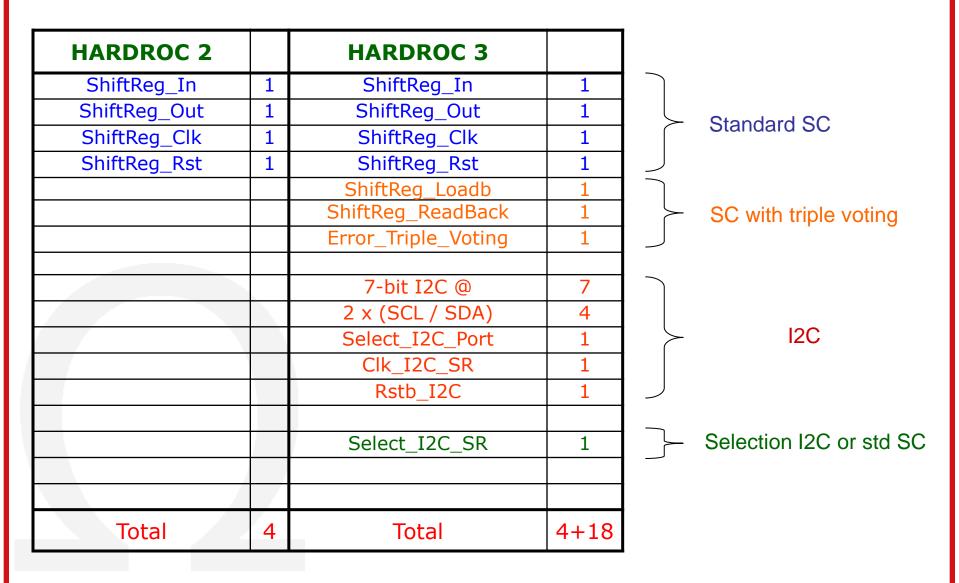

#### HARDROC3

- First of the "3<sup>rd</sup> generation ROC chip" to be submitted

- independent channels, one register/channel, I2C link for SC parameters(@IPNL), triple voting, circular memory, temperature sensor

- Digital part finished in July 2012

- Analog part: No major modifications in the analog part. Extension of the dynamic range to set Vth0=100fC Vth1=5pC and Vth2 > 15 pC

- Die size ~30 mm2

- <u>Submission in FEB 2013</u>=> reception in June 2013.

#### Next: SPIROC3 or SKIROC3 ?

- Still many tests to be done at the system level/testbeam

- Hardroc3 test feedback necessary before submitting Spiroc3/skiroc3

- Spiroc3= 36 channels, 8.5 x 5 mm2 => 42.5 k€ in MPW run

- Skiroc3= 64 channels, 8.5x9.5 mm2 => 81 k€ in a MPW run => dedicated run mandatory

- SPIROC3 and SKIROC3 in Feb 2014 in a dedicated run (AIDA, CALICE and other partners)

mega

DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

<u> Mega</u>

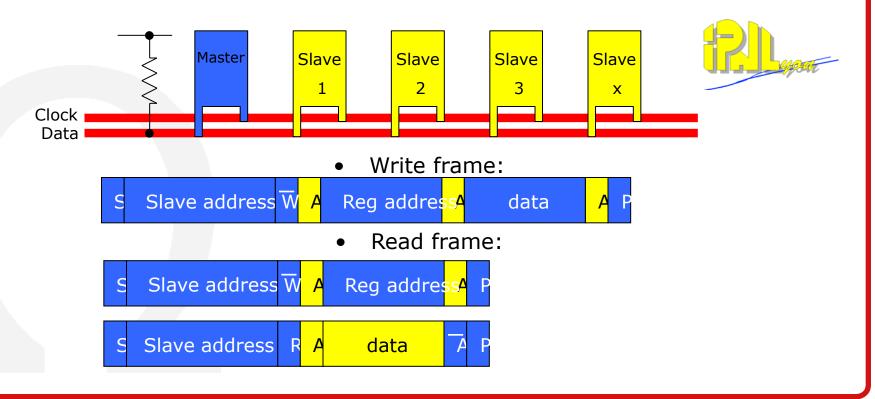

# 3Gen ROC chips: common features

- Slow control parameters:

- Backward compatibility with 2Gen ROC chips slow control

- Use of classical shift register slow control

- Embedded I2C

- 7-bit address + 1 general call address (127 chips can be addressed)

- Access port doubled

- Bidirectional data line with open collector (Driver will be the same as Dout)

- Read back capability of SC bits (non destructive)

DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

(<u>)mega</u>

## 3Gen ROC chips: common features

• Extra pin needed for I2C / SC:

DAQ/Electronics meeting 10-11 Dec, 2012 N.Seguin-Moreau

<u>()mega</u>

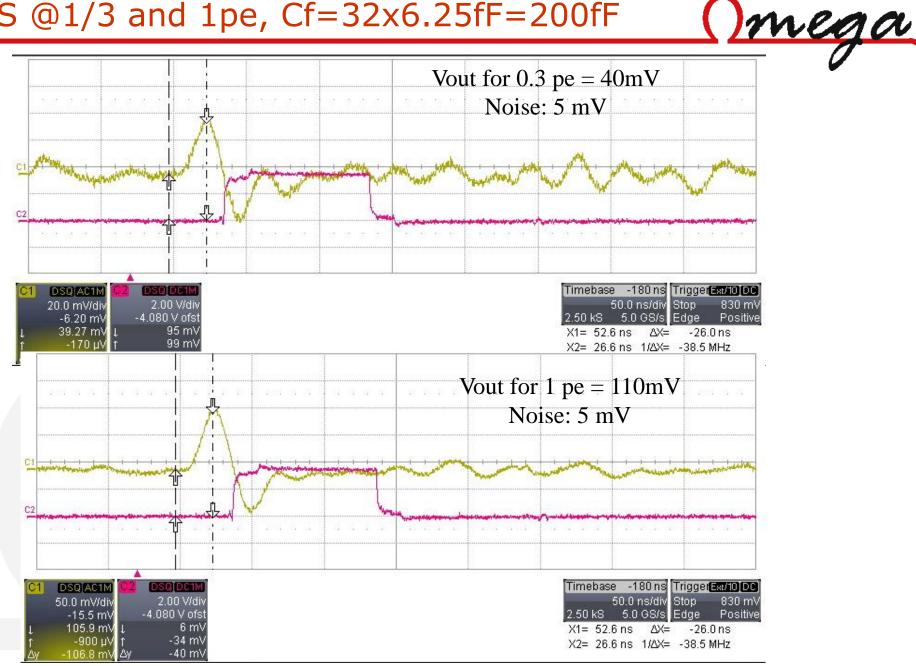

### FS @1/3 and 1pe, Cf=32x6.25fF=200fF

« Pedestal shift » due to coupling on Vdda\_pa on spiroc2b

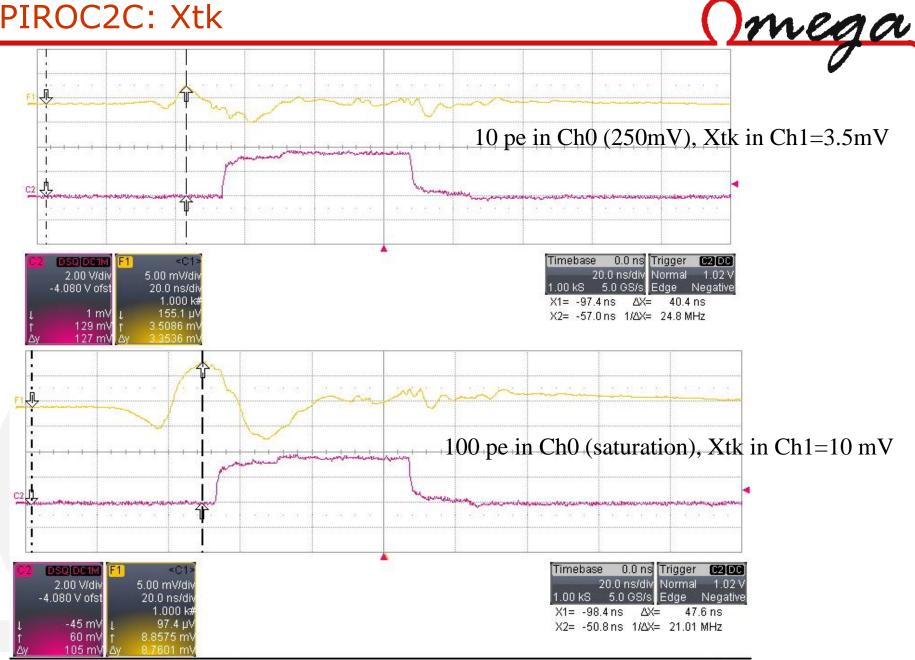

Spiroc2c: Injection of 10, 100, 300 and 1000pe- in ch0 and measurement of the charge (HG) seen on the neighbours (all preamp on but all discris masked except of ch<0>:

|        | 10pe-    | 100pe- | 300pe- | 1000pe- |

|--------|----------|--------|--------|---------|

| Ch<0>  | 950 UADC | 3500   | 3500   | 3500    |

| Ch<1>  | 470      | 470    | 450    | 450     |

| Ch<2>  | 470      | 460    | 440    | 440     |

| Ch<3>  | 460      | 463    | 446    | 446     |

| Ch<20> | 460      | 457    | 450    | 450     |

| Ch<35> | 455      | 457    | 455    | 455     |

When discris of the other channels are ON = > we measure Xtk in the neighbours

mega

## SPIROC2C: Xtk

## SPIROC 2c: Zero event bug

## SPIROC2C: New Delay box