# SKIROC2 O AIDA FEV and testbench measurements

LAL, LLR and OMEGA

Orsay Micro Electronics Group Associated

## **SKIROC : Reminder**

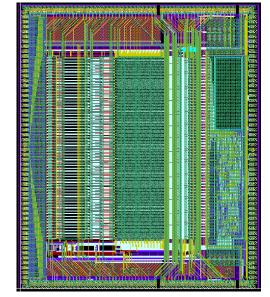

- SKIROC2 :

- Very similar to SPIROC

- 64 channels, 65 mm<sup>2</sup>

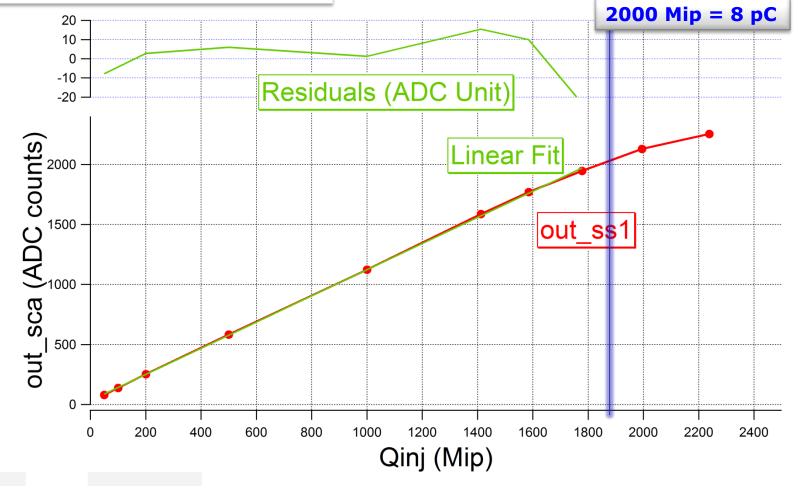

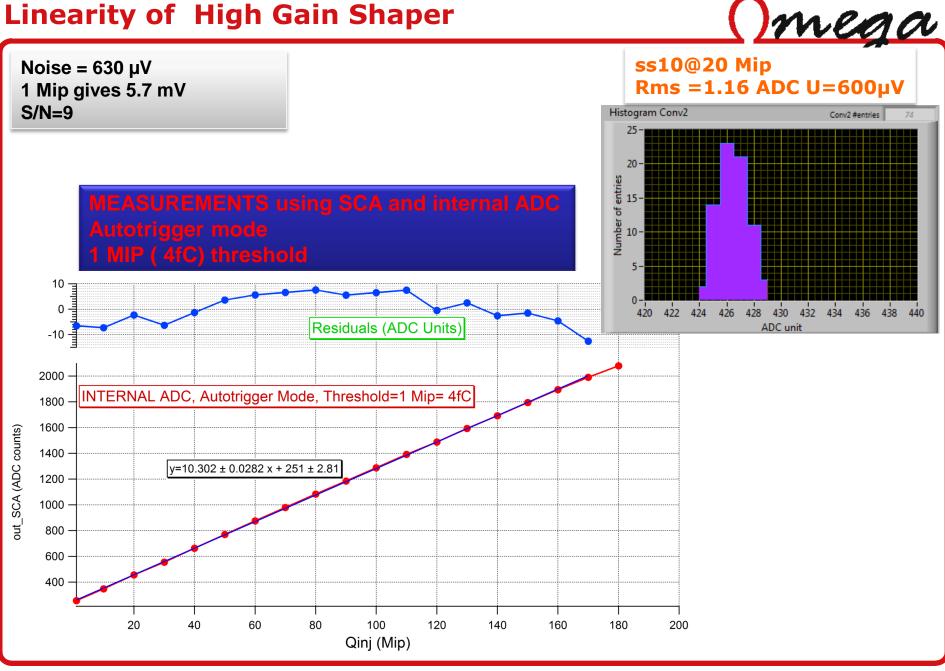

- Very large dynamic range:

- HG for 0.5-500 MIP

- LG for 500-3000 Mip

- Internal 12 bit ADC/TDC

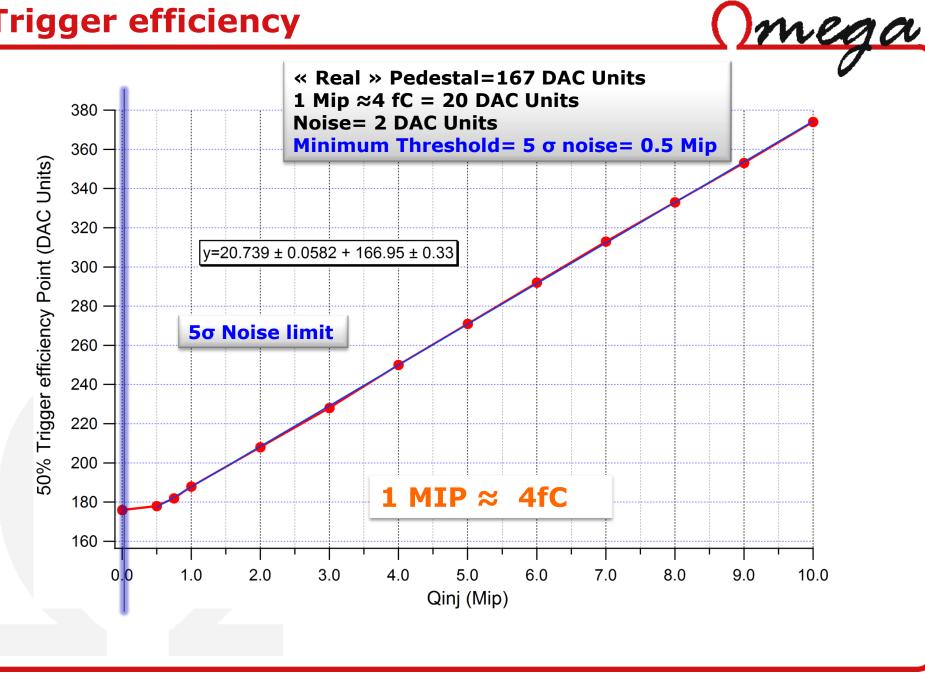

- Autotrigger on MIP (4 fC)

- Sparsified readout compatible

with EUDET 2<sup>nd</sup> generation DAQ

- Pulsed power -> 25  $\mu$ W/ch

- 1200 chips produced in March

2010 (dedicated run => 42 k€)

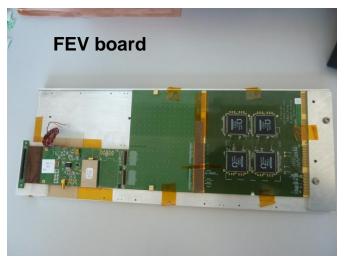

- TB in July 2012:

6 FEV boards equipped with 4 SK2 (1536 channels)

mega

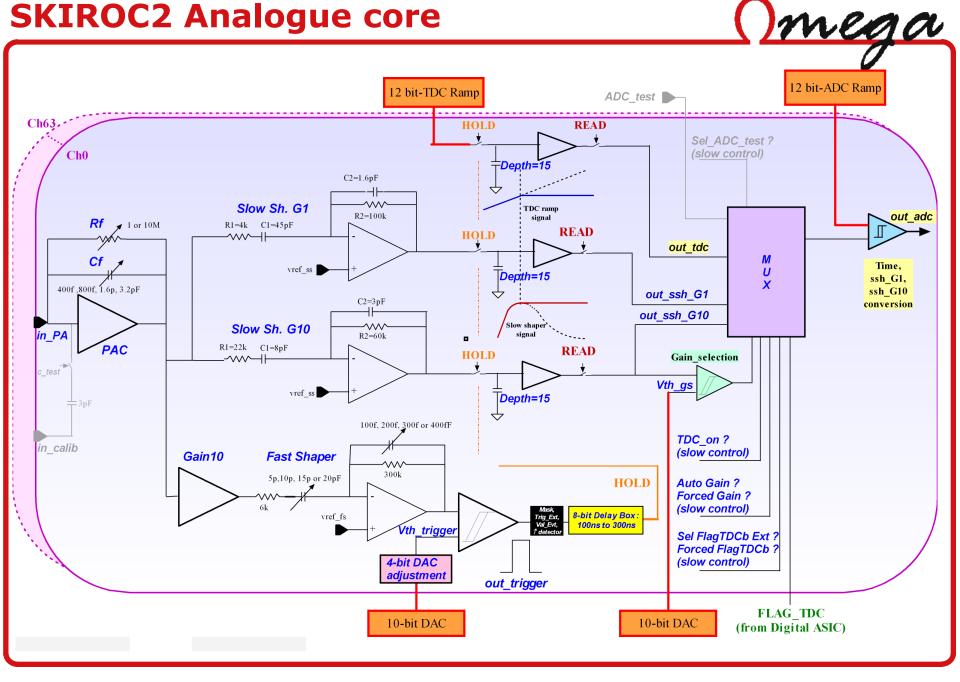

- VERY SIMILAR TO SPIROC, same digital part

- Very low noise (0.4 fC = 2 500 e-) and very large dynamic range (2fC up to 10 pC) charge preamplifier

- **180ns** shaping time Slow Shapers for charge measurement

- 2-bit shaping time adjustable Fast Shaper (50 to 100ns)

- 10-bit DAC for discriminator threshold, With 4-bit adjustment on each channel

- Analogue Memory depth : up to 15 events can be stored

- Trigger Discriminator for autotrigger on 1/2 MIP

- 8-bit adjustable delay to position the Hold signal

- Digitization of either time and charge or of both charges

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

mega

#### **SKIROC2** Analogue core

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

# **Trigger efficiency**

<u> Mega</u>

#### **MEASUREMENTS using SCA and internal ADC**

Autotrigger Mode With 1 MIP (4 fC) threshold

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

#### Linearity of High Gain Shaper

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

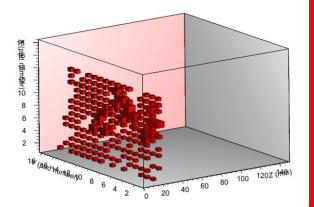

# First test beam with the technological prototype mega

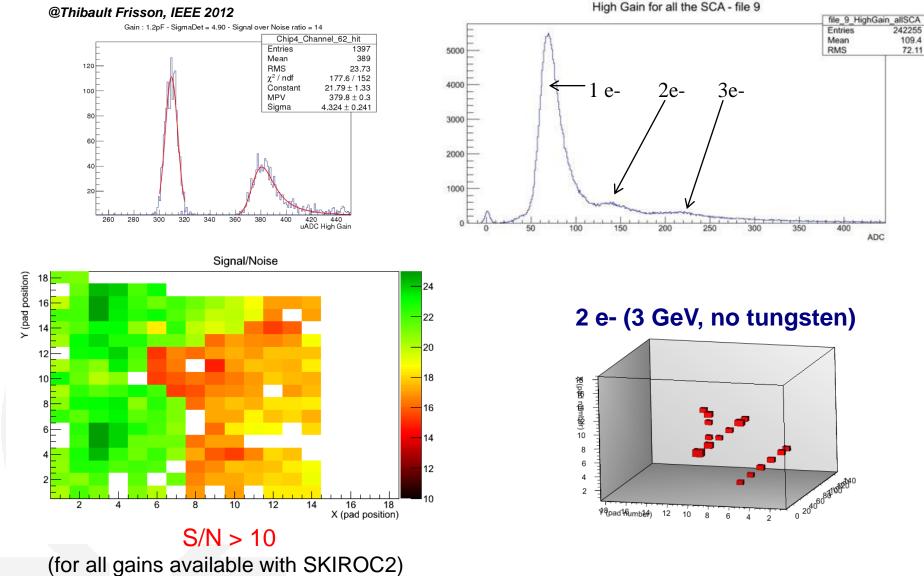

@Thibault Frisson, IEEE 2012

DESY – April and July 2012 e- (1 - 5 GeV)

- 6 layers (FEV8)

- Internal trigger

# .Total = 1536 channels .channels with not aligned pedestal → switched off .total active channels = 1278

#### PVC structure

- position for tungsten plates (2.1 mm)

#### Goals:

- Determine signal over noise ratio of the detector

- Operate first layers of the technological prototype

- Establishment of calibration procedure for a large number of cells

- Homogeneity of response (x,y scan of detector)

#### **First results**

109.4

72.11

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

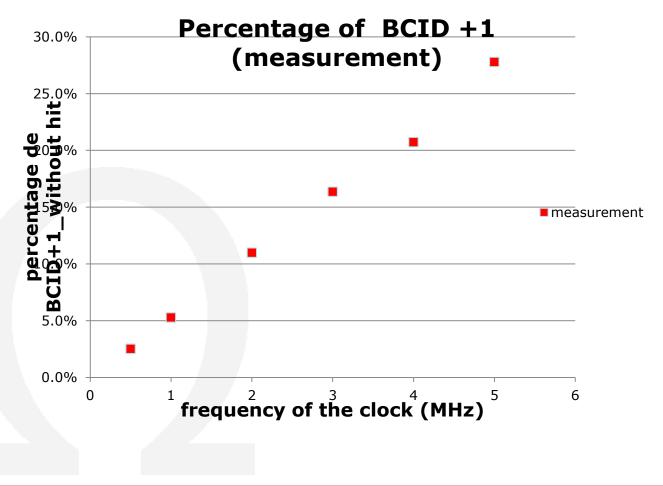

### **BCID+1 events**

- Good test beam results but many points to be undertsood

- Number of BCID +1 events without hit effect : increases with the frequency of the clock

()mega

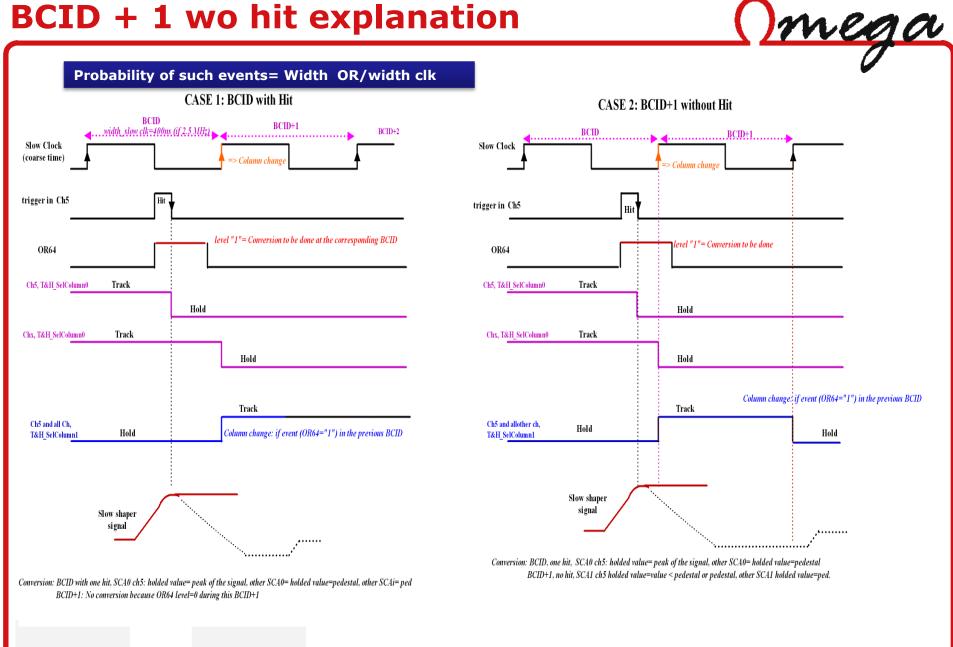

#### **BCID + 1 wo hit explanation**

#### SKIROC2 DAQ/Electronics meeting at DESY

2012, Dec 10th

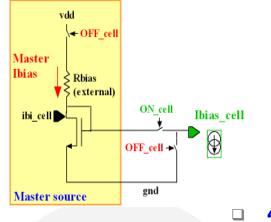

# **POWER PULSING (1)**

- **Requirement:**

- □ 25 µW/ch with 0.5% duty cycle

- **500 µA for the entire chip**

# $\frac{Acq}{Train length:}$ $\frac{Acq}{2820x337ns=950\mu s}$ Time between 2 trains: 200 ms

#### Power pulsing:

- Bandgap + ref Voltages + master I: switched ON/OFF

- Shut down bias currents with vdd always ON

SK2 power consumption measurement:

123 mA x 3.3V ≈ 40 mW => 0.6 mW/ch

Time between 2 bunch crosings:

4 Power pulsing lines : analog, conversion, dac, digital

Each chip can be forced on/off by slow control

| Measurements                                                          |                 |                             |

|-----------------------------------------------------------------------|-----------------|-----------------------------|

| Acquisition                                                           | 88 mA , 290 mW  | Duty Cycle =0.5%, 1.45 mW   |

| Conversion                                                            | 27.3 mA, 90 mW  | Duty Cycle =0.25%, 0.225 mW |

| Readout                                                               | 8.0 mA, 26.4 mW | Duty Cycle =0.25%, 0.066 mW |

| Skiroc2 power consumption with Power pulsing: 1.7 mW ie 27 $\mu W/ch$ |                 |                             |

SKIROC2 DAQ/Electronics meeting at DESY

2012, Dec 10th2

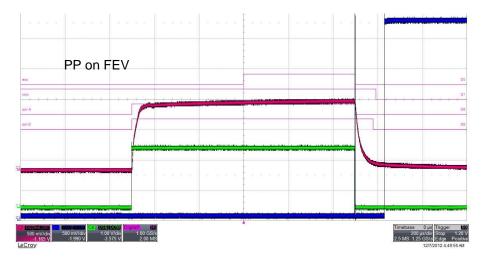

#### **POWER PULSING: Timing**

First measurements by LLR and LAL, performed on testbench (one ASIC) and on FEV with and wo wafers

•

•

•

•

- Power pulsing on testbench: test board wo any decoupling capacitors on bias and on reference Voltages

- Pwr on A and dac= 200µs necessary for the preamp to reach its DC level

- Power pulsing of FEV board

PP on testboard

mega

SKIROC2 DAQ/Electronics meeting at DESY 2012, Dec 10th

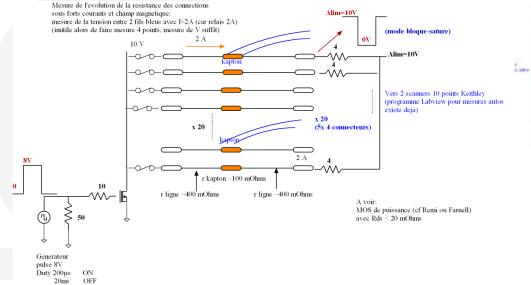

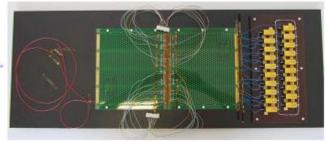

#### **POWER PULSING: TB and B field**

#### TB at DESY next Feb 2013

- Power pulsing in TB conditions of one of the 7 layers: layer 7 wo decoupling capacitors

- scrutinizing understanding of detector response

- Power pulsing of 2 ASUs to test the interconnections in a 2T field and with 2 amps flowing in the connections

- Many measurements on testbench and at system level and many analysis of the last testbeam data still on going:

- BCID + N (N>1) events = plan events to be understood

- To prepare next testbeam (February 2013) and power pulsing

- To prepare SKIROC3:

- 64 independant channels

- Estimated area = 8.5x9.5 mm2

- => dedicated run necessary just as it was in 2010

<u>)mega</u>