## SDHCAL R&D status

I.Laktineh On behalf of the SDHCAL-GRPC groups

Calice meeting Annecy Sep. 2013

# Beyand SDHCAL technologic

A prototype with 48 GRPC of 1 m2 was conceived and realized as a first technological demonstrator

Then what next?

## Road map beyond the DBD

- 1- Build few very large GRPC detectors (2-3 m2) : Gas circulation system, thickness...

- 2- Improve on the readout electronics (I2C, roll mode..)

- 3- Design a new ASU capable to read the large GRPC (up to 3 m<sup>2</sup>)

- 4- Develop a new DIF (low consumption, reduced size, new functionalities)

- 5- Build a small mechanical prototype to host the few large chambers

Large GRPC for ILD:

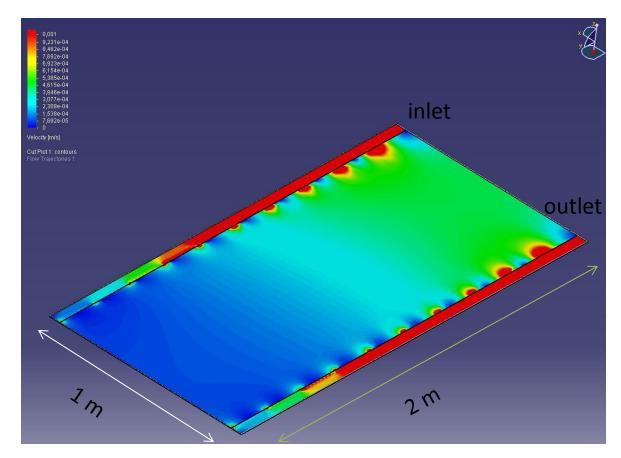

GRPC with a surface  $\leq 3 \text{ m}^2$  are needed.

We intend to build a 2m<sup>2</sup> GRPC (glass are already there).

We are currently studying the gas distribution system to ensure a good gas renewal.

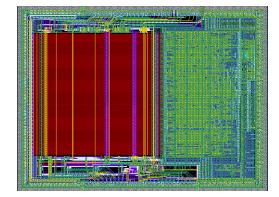

#### Readout electronics :HARDROC3

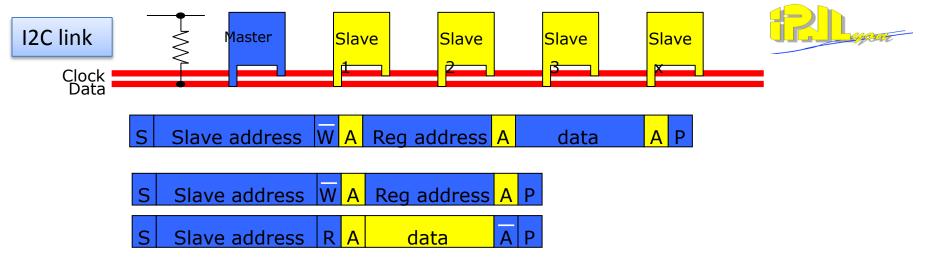

Main issue: To communicate with each ASIC

- 64 independent channels

- I2C link (@IPNL)

- PLL: integrated before in a building block, first measurements are very good

- Input frequency 2.5 MHz =>output frequency: 10, 20, 40, and 80 MHz available

- Bandgap: new one with a better temperature sensitivity, tested in a building block

- Temperature sensor: tested in a building block, slope 6mV/°C

- Die size ~30 mm2 (6.3 x 4.7 mm2)

- To be packaged in a TQFP208

- Test board is designed and being produced

- Tests to start soon.

- 3<sup>rd</sup> generation ROC chip

- Independent channels (= Zero suppress)

- 64/36 address pointers

- ReadOut, BCID

- $\Rightarrow$ Digital part much more complicated

- $\Rightarrow$  Possibility to use "Roll mode" by Slow Control: circular memory very useful for Testbeam

- New Slow Control (Triple voting) using I2C link (while keeping the « old SC » system)

Calice meeting Annecy Sep. 2013

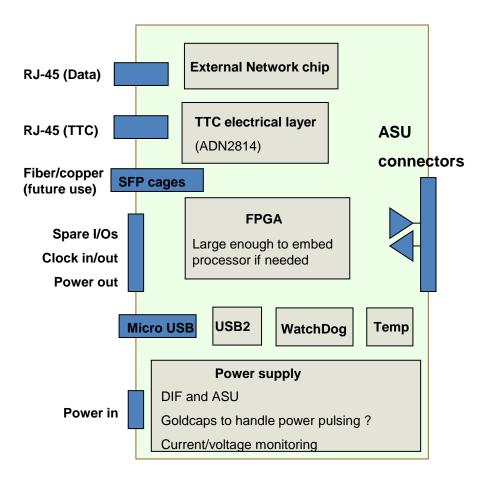

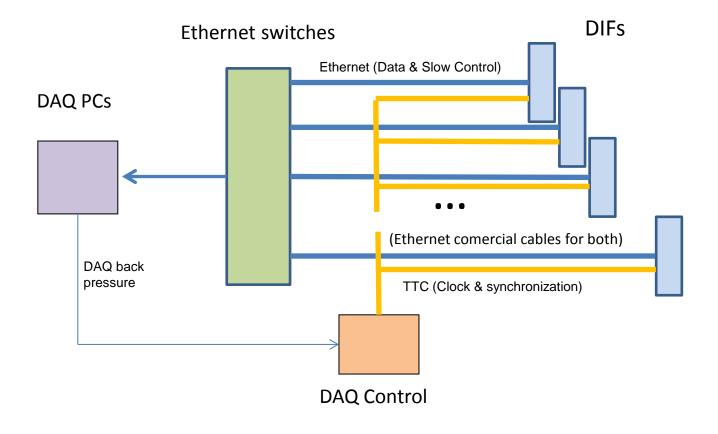

## **DIF: Designed for ILD SDHCAL**

- Only one DIF per plane. For the maximun lenght plane (1x3m) the DIF will handle 432 HR3 chips

- Slow control through the new HR3 I2C bus

- Data transmision to DAQ by Ethernet using comercial switches for concentration

- Clock and syncronization by TTC

- USB 2.0 for debugging

### New SDHCAL DAQ achitecture

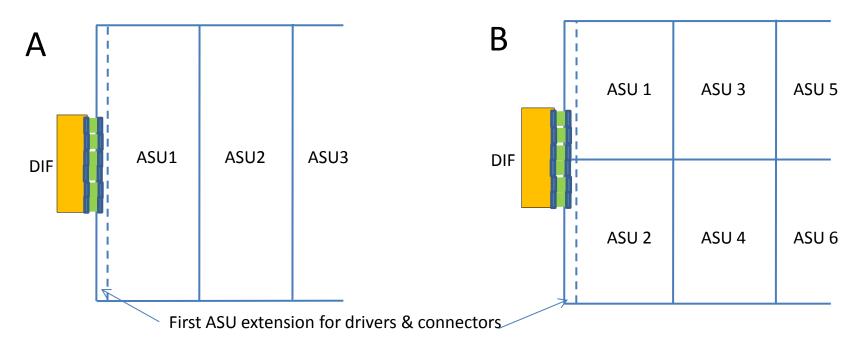

# New ASU layout options

As there will be only one DIF per plane, the distribution of the ASU boards in the plane will be rearranged to reduce the number of conections between the DIF and the plane

- In option B the common signals for the plane have to be sent twice (one per slab) while in option B they can be sent only once

- But, option A looks more risky from the point of view of the feasibility of the 1m long ASU boards.

- In both options the ASUs connected to the DIF will be a bit longer to host the connectors and the buffers for driving the long lines. This extension provides more freedom for the connectors selection and moves the drivers heat disipation to the ventilation area

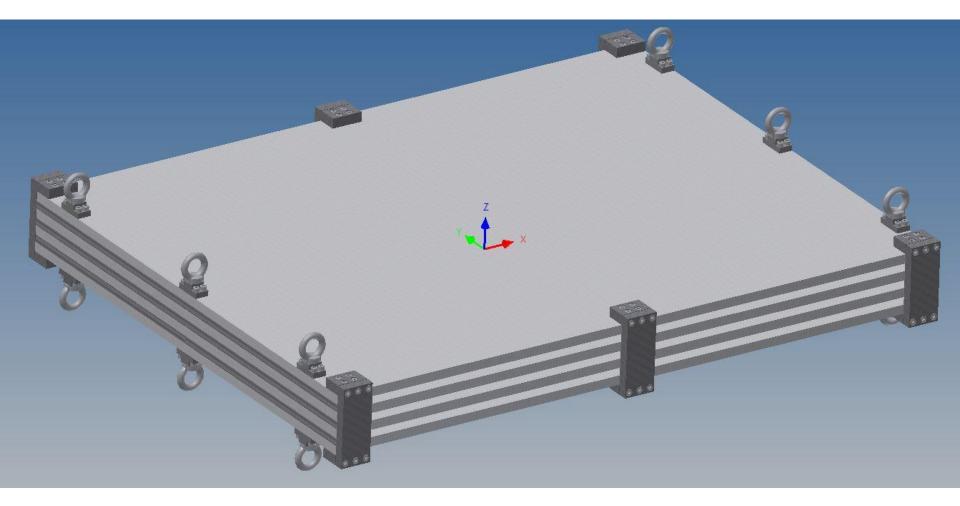

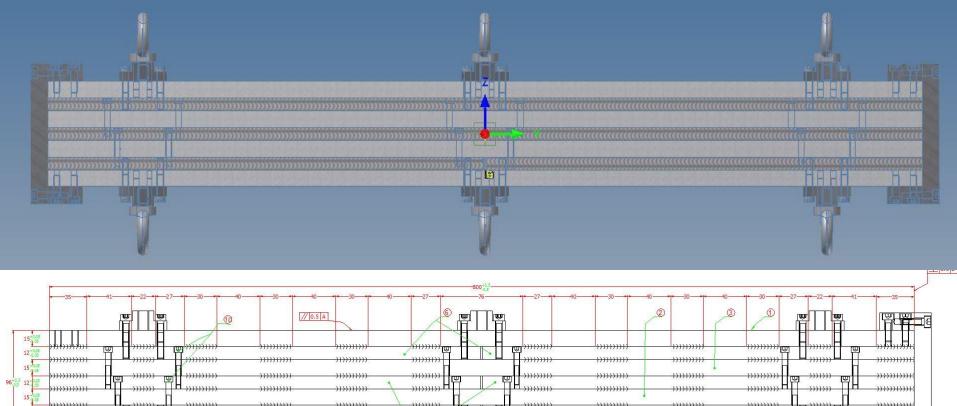

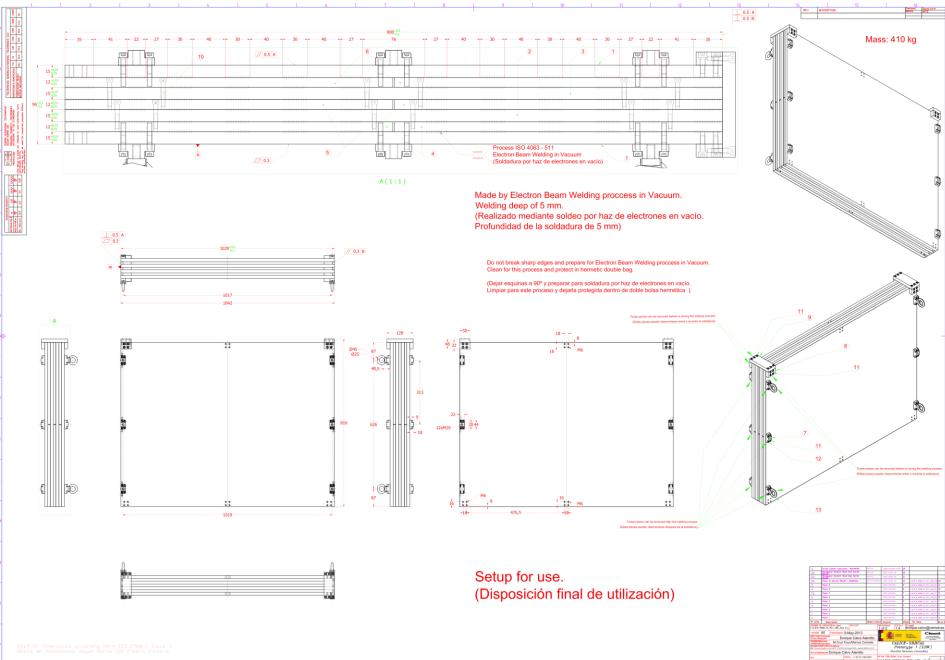

#### Self-supporting mechanical structure

12

Made by Electron Beam Welding proccess in Vacuum. Welding deep of 5 mm.

# Conclusion

- -The work on large detector GRPC for ILD is ongoing but at low

- -The HARDROC3 test results will determine the pace of this whole readout R&D chain in the future months.

- -The detector conception and realization should be achieved soon.