### **HR3: First measurements**

#### OMEGA, 22/11/2013

**OMEGA** microelectronics group

IN2P3-CNRS, Ecole Polytechnique, Palaiseau (France)

#### Organization for Micro-Electronics desiGn and Applications

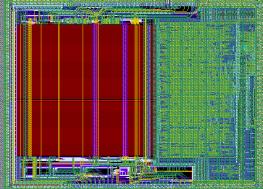

### HARDROC3

- **3**<sup>rd</sup> generation chip for ILD

- Independent channels (zero suppress)

I2C link (@IPNL) for Slow Control parameters and triple voting

□ HARDROC3: 1<sup>st</sup> of the 3<sup>rd</sup> generation chip to be submitted

- analog part: extension of the dynamic

- PLL: integrated to generate clocks internally

- Submitted in Feb 2013 (SiGe 0.35 $\mu$ m), funded by AIDA, received end of June 2013

- Die size ~30 mm<sup>2</sup> (6.3 x 4.7 mm<sup>2</sup>)

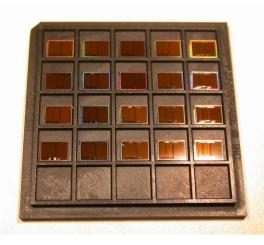

- Packaged in a QFP208,

- HR3 will equip 2-3m RPC chambers

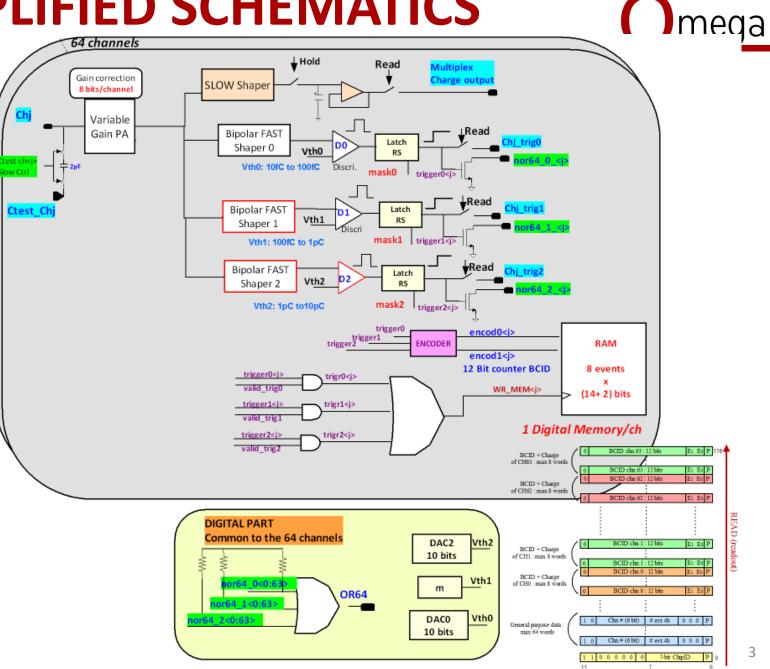

### SIMPLIFIED SCHEMATICS

DESY 9-10/12/2013

3

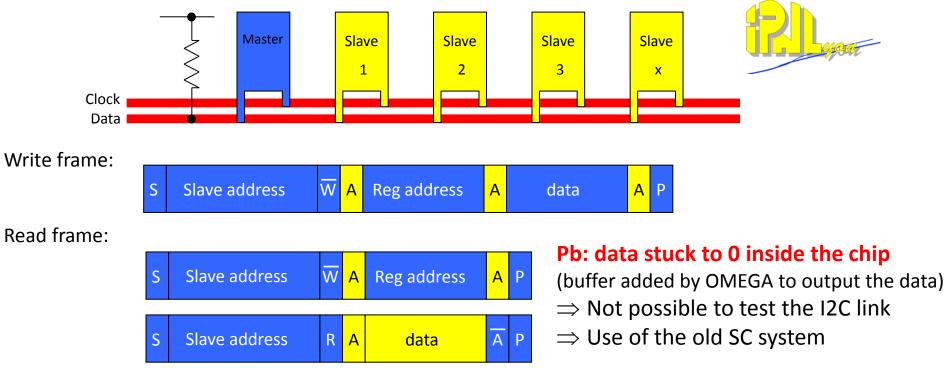

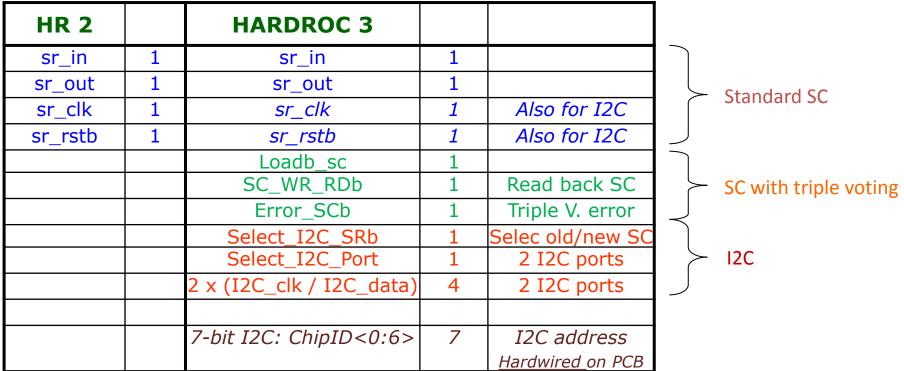

### 3<sup>rd</sup> generation: Slow Control parameters

- Slow control parameters:

- Backward compatibility with 2Gen ROC chips slow control

- Use of classical shift register slow control

- Embedded I2C

- 7-bit address + 1 general call address (127 chips can be addressed)

- Access port doubled

- Bidirectional data line with open collector (Driver will be the same as Dout)

- Read back capability of SC bits (non destructive)

## 3<sup>rd</sup> generation SC

- Extra pin needed for I2C / SC:

- Possibility to choose between old SC registers/ New I2C link (Select\_I2C\_SRb) available on one pin)

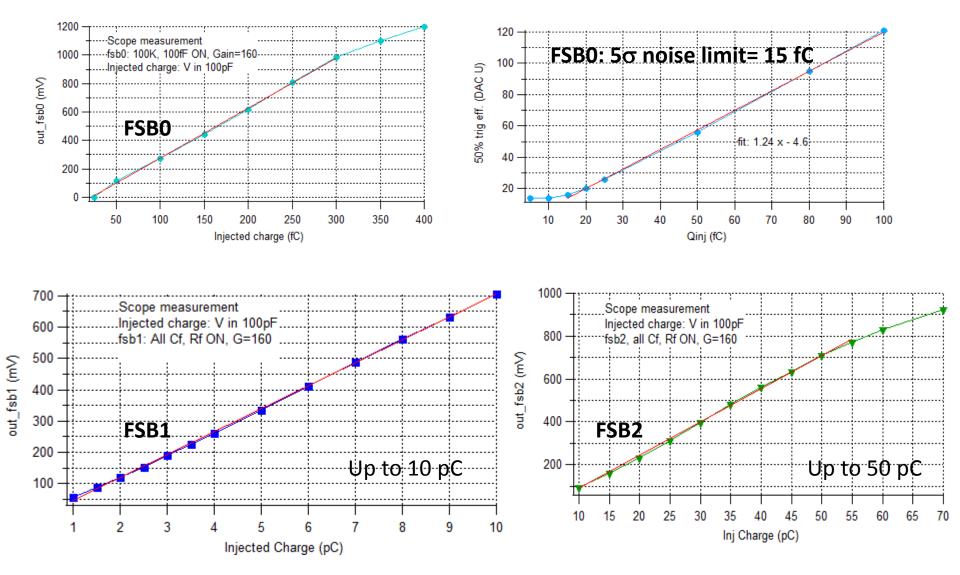

# ANALOG PART: FSB LINEARITY Omega

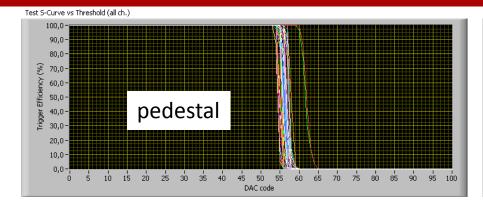

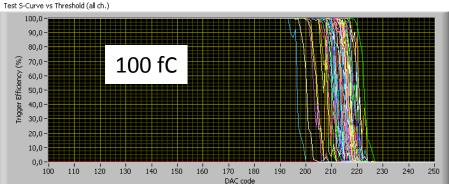

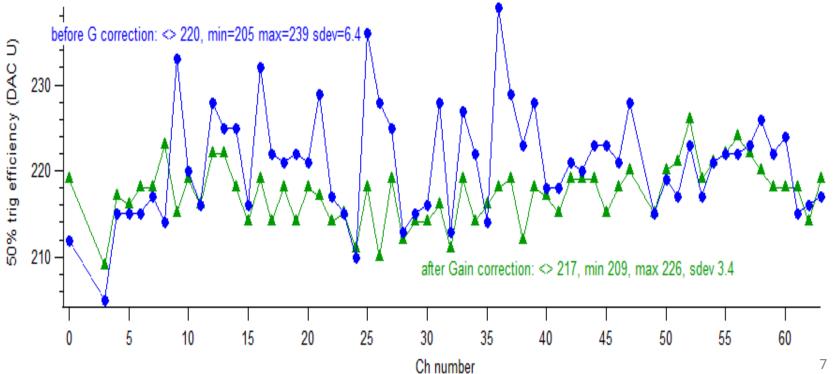

### **SCURVE MEASUREMENTS**

### mega

DESY 9-10/12/2013

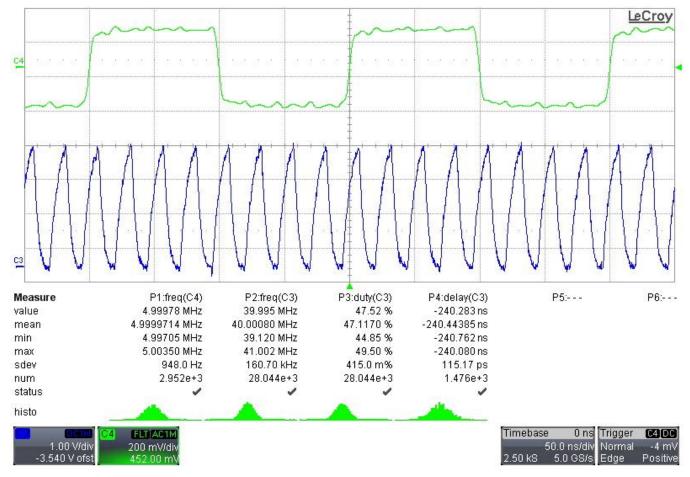

### **HR3: PLL tests**

#### Input LVDS clock @ 5 MHz:

- $\Rightarrow$  Mult factor = N+1 = 8

- $\Rightarrow$  Output freq of PLL = 40 MHz

- $\Rightarrow$  Full chain tested with charge injected on chn 31 and readout on serial link

mega

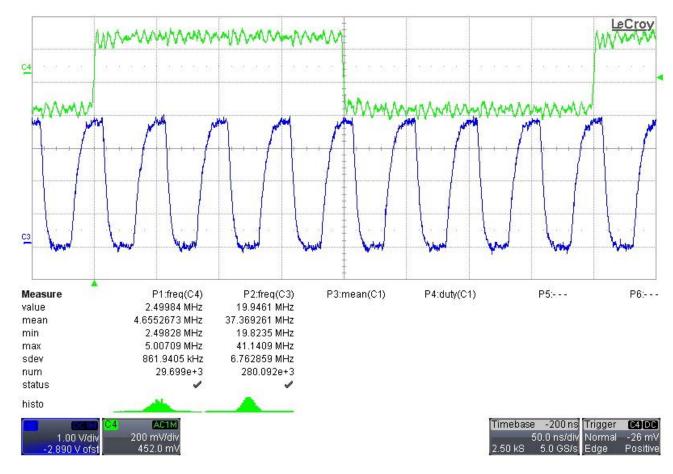

### **HR3: PLL tests**

#### Input LVDS clock @ 2,5 MHz:

- $\Rightarrow$  Mult factor = N+1 = 8

- $\Rightarrow$  Output freq of PLL = 20 MHz

- $\Rightarrow$  Full chain tested with charge injected on chn 31 and readout on serial link

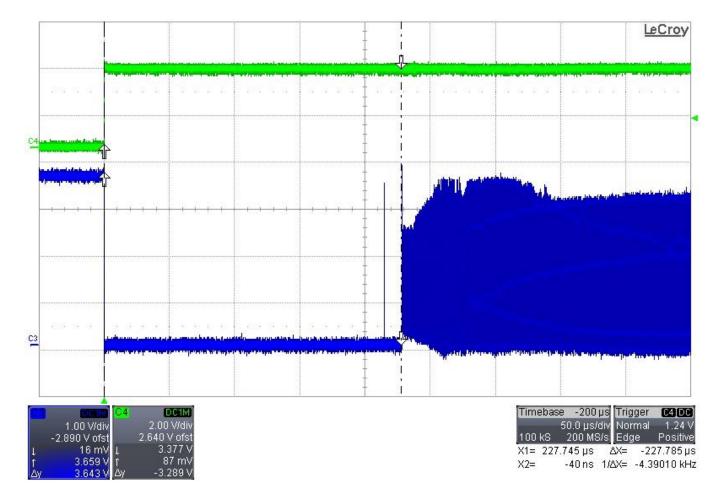

### HR3: PLL lock time

#### Lock time (start time):

- $\Rightarrow$  Green = PowerOnD / Blue = Out\_PLL

- $\Rightarrow$  Time needed to have a stable clock = 230 + 30 = 260  $\mu s$

mega

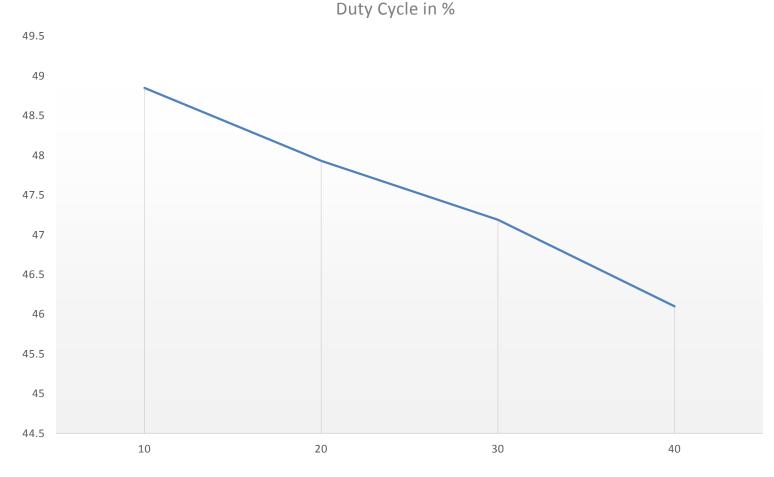

### HR3: PLL Duty cycle

#### Input LVDS clock @ 5 MHz:

- $\Rightarrow$  Mult factor = 2 / 4 / 8 / 16

- $\Rightarrow$  X = freq of Out\_PLL

- $\Rightarrow$  Y = duty cycle in %

DESY 9-10/12/2013

() mega

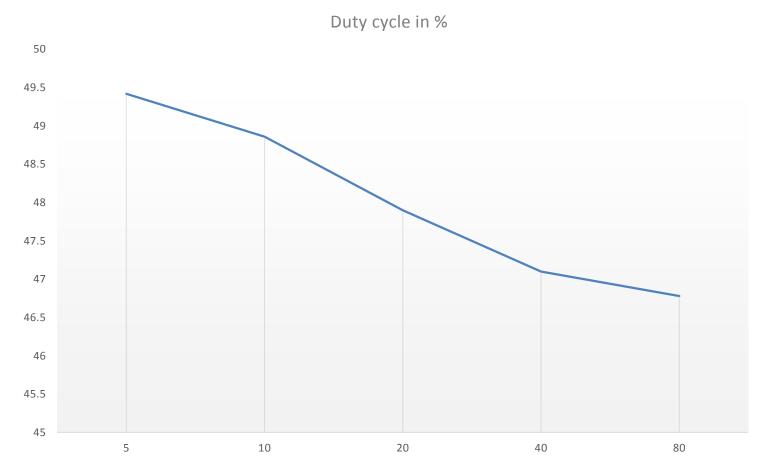

### HR3: PLL duty cycle

#### Input LVDS clock @ 2,5 MHz:

- $\Rightarrow$  Mult factor = 2 / 4 / 8 / 16 / 32

- $\Rightarrow$  X = freq of Out\_PLL

- $\Rightarrow$  Y = duty cycle in %

mega

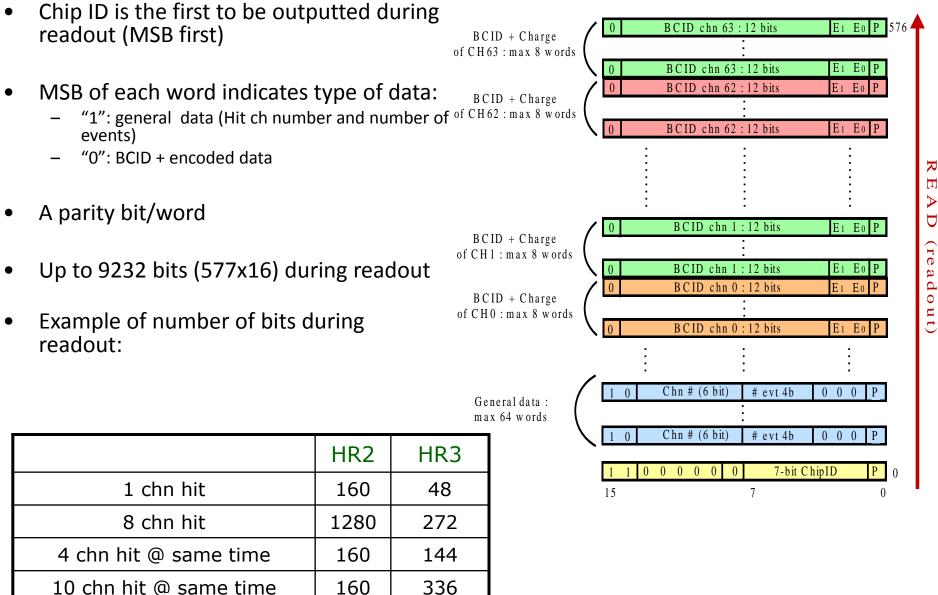

### HARDROC 3 : Memory mapping

### HARDROC 3 : digital part

#### • Zero suppress (only hit channels are readout): test OK

| Setup                                                                                                                    | Slow Co  | Control 1 Slow Control 2 SCA Read, Temp. Fl |      |      |      | FPC  | GA Configuration Info HAI |     |     |                                                                                        | ARDRO | OC3 I2C test Info p         |      |       |                                                                                                                                                                                                            | pcb I/O Info pcb Test |     |       | est                           | Mixed Test: S-Curve (Threshold) |      |                                                                                                |    |   |   |   |  |

|--------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------|------|------|------|------|---------------------------|-----|-----|----------------------------------------------------------------------------------------|-------|-----------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-------|-------------------------------|---------------------------------|------|------------------------------------------------------------------------------------------------|----|---|---|---|--|

| Mixed Test: 5-Curve (Threshold) all Ch. Analogue Test: DAC                                                               |          |                                             |      |      |      |      | Analogue Test: DC         |     |     |                                                                                        |       | External ADC External ADC c |      |       |                                                                                                                                                                                                            |                       |     | calib | alib Digital ASIC Debug / DAQ |                                 |      |                                                                                                |    |   |   |   |  |

| Step by Step DAQ<br>Reset ASIC Digital<br>Start Acquisition<br>FPGA External Trigger<br>Start ReadOut1<br>Start ReadOut2 |          |                                             |      |      |      | E    | hipSat<br>nd Rea          |     |     | Frame received OK ?<br>OK<br>Nb of bits read in ASIC RAM<br>304<br>Chip ID 2<br>100111 |       |                             |      |       | Automatic DAQ Automatic DAQ Automatic DAQ Automatic DAQ ChipSatb must be enabled SlowClock -> CLK_GENE_EXT Nb of Acquisitions 10 TimeDut for 1 Acq/Conv/R0 10ms (Slow Clock @ 5MH2) \[ Current Acquisition |                       |     |       |                               |                                 |      | Data Analysis<br>Clean DAQ<br>data folder<br>Analyze saved<br>data now !<br>Files data loading |    |   |   |   |  |

| ASIC Memory (Raw Data) Decoded Data<br>Signal injected only in ch 20 and 43                                              |          |                                             |      |      |      |      |                           |     |     |                                                                                        |       |                             |      | 1     |                                                                                                                                                                                                            |                       |     |       |                               |                                 |      |                                                                                                |    |   |   |   |  |

|                                                                                                                          |          |                                             |      |      |      |      |                           |     |     |                                                                                        |       |                             | Sig  | nal i | inje                                                                                                                                                                                                       | cte                   | d o | nly   | in c                          | h 2                             | .0 a | nd                                                                                             | 43 |   |   |   |  |

| HR3 Decoded Data                                                                                                         |          |                                             |      |      |      |      |                           |     |     |                                                                                        |       |                             |      | _     | _                                                                                                                                                                                                          |                       |     |       |                               |                                 |      |                                                                                                |    |   |   |   |  |

| Ch                                                                                                                       | nannel # | 20                                          | 20   | 20   | 20   | 20   | 20                        | 20  | 20  | 43                                                                                     | 43    | 43                          | 43   | 43    | 43                                                                                                                                                                                                         | 43                    | 43  | 0     | 0                             | 0                               | 0    | 0                                                                                              | 0  | 0 | 0 | 0 |  |

| ВС                                                                                                                       | ID       | 3753                                        | 3253 | 2753 | 2253 | 1753 | 1253                      | 753 | 253 | 3753                                                                                   | 3253  | 2753                        | 2253 | 1753  | 1253                                                                                                                                                                                                       | 753                   | 253 | 0     | 0                             | 0                               | 0    | 0                                                                                              | 0  | 0 | 0 | 0 |  |

| E1                                                                                                                       | l / EO   | 1                                           | 1    | 1    | 1    | 1    | 1                         | 1   | 1   | 1                                                                                      | 1     | 1                           | 1    | 1     | 1                                                                                                                                                                                                          | 1                     | 1   | 0     | 0                             | 0                               | 0    | 0                                                                                              | 0  | 0 | 0 | 0 |  |

- Roll mode SC : test OK

- If RollMode = "0" → Backward compatibility with 2Gen ROC chips behavior

- Only the N first events are stored

- If RollMode = "1" → 3Gen ROC chips behaviour

- Use the circular memory mode

- Only the N last events are stored

- "Noisy Evt" SC: 64 triggers => Noisy event => no data stored : test OK

- "ARCID" SC (Always Read Chip ID): test OK

- If ARCID = 0  $\rightarrow$  Backward compatibility: No event  $\rightarrow$  No readout

- − If ARCID= 1 → New behavior: No event → Read CHIP ID

### **Summary and next steps**

- Good analog performance:

- dynamic range extended up to 50 pC

- PLL => clocks generated internally

- Preliminary good digital performance

- Zero suppress, roll mode, ARCID mode, Noisy evt mode tested successfully on testboard

- External trigger available to be able to check the status of each channel

- I2C link

- FIB on 2 chips to test the link

- 2-3m long RPC chambers to be built and equipped with HR3 in 2014

nega