# Status of DAQ System for Scintillator Calorimeters.

- Design concept

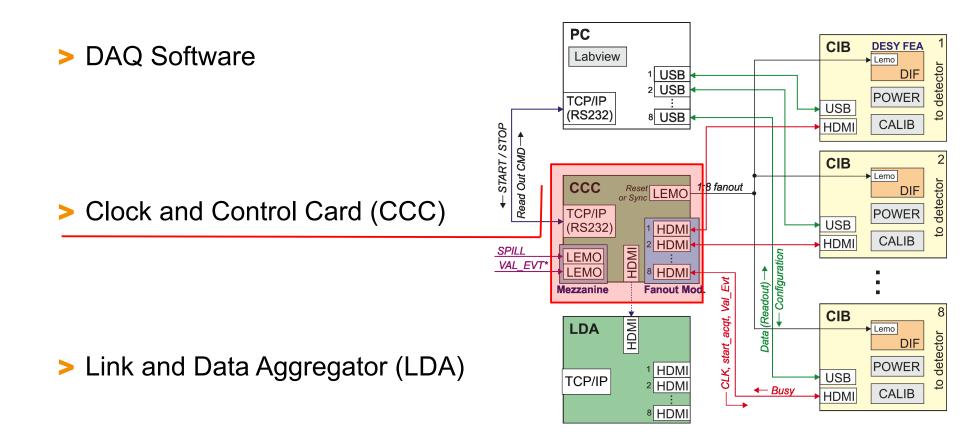

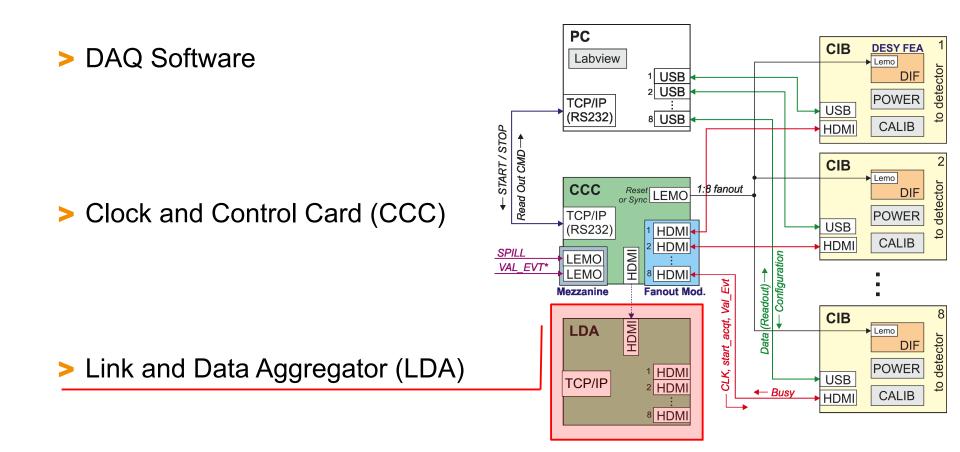

- > DAQ Software

- > Clock and Control Card (CCC)

- Link and Data Aggregator (LDA)

- Future plans

Aliakbar Ebrahimi - DESY CALICE AHCAL Main Meeting 2013 Hamburg, Dec 09-10 2013

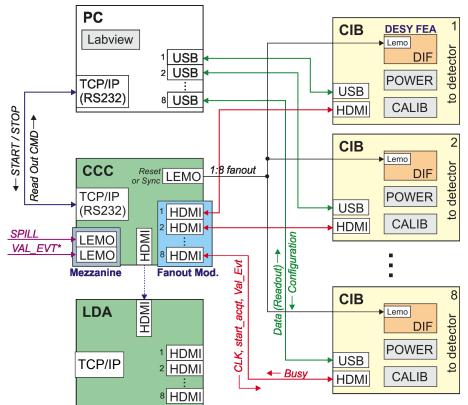

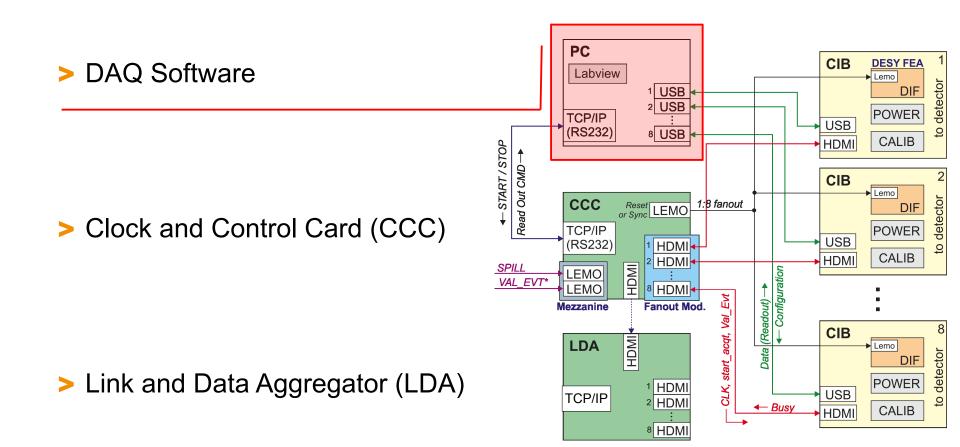

# **DAQ Design Concept**

- The original DAQ could operate only one layer

- New multilayer DAQ based on the original CALICE DAQ concept

- > Built on the single layer DAQ

- Software improvement

- Multiple-DIF configuration

- Global clock and control

- Data aggregator

- Parallel readout

- Scalable

- Currently there are 2 connections to DAQ interfaces (DIF):

- HDMI for fast signals

- USB for slow signals and data

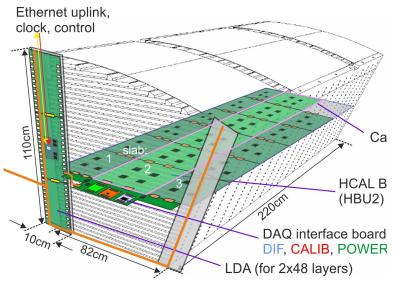

#### **Main DAQ components**

# **AHCAL DAQ Software**

- > Based on LabView

- Live monitoring, easy modifications

- Some tasks done using C++ libraries

- Multithreaded

- > Modular

|                                                                               | ASIC Power Enable         | CCC Connection    | Polling             | Unpacking |

|-------------------------------------------------------------------------------|---------------------------|-------------------|---------------------|-----------|

| No. Devices Handles                                                           | ASIC Power Return         | CCC Address Port  | Polling Poll Device | Method    |

| 0 Handle SerialNo<br>49567872                                                 | ^                         | fichcalccell 3141 | ccc                 | C++ Lib   |

| Handle StriatNo                                                               | off Ack 🥥 🗍 🔘             | CCC Centig Path   | Timeout<br>400      |           |

| 49167872<br>8 Config                                                          | •                         | 1 ccc_conf.uml    |                     |           |

| Latency (ms)                                                                  | VDDA/VDDD Power Enable    | Configure Probe   |                     |           |

| Set: 2                                                                        | VDD Power Return          |                   |                     |           |

| Baud Rate Flow Control Purge Rags<br>9000 None - FT_PURGE_RX                  | ON Set 0                  |                   |                     |           |

| Stop Bits Parity Word Length<br>FT_STOP_BITS_1 + FT_PARITY_NONE + FT_BITS_8 + |                           |                   |                     |           |

|                                                                               | 3.3V+Drivers Power Enable |                   |                     |           |

| b Init Return<br>USB Open (all) OUSB Init (all) OReset DIF (all)              | 3.3V Power Return         |                   |                     |           |

| Single Init Returns                                                           | ON                        |                   |                     |           |

| 51 open init reset SerialNo ^                                                 | OFF ON Adk 🔾 🗍 👅          |                   |                     |           |

| 0 0 0                                                                         |                           |                   |                     |           |

| open init reset SerialNo =                                                    |                           |                   |                     |           |

|                                                                               |                           |                   |                     |           |

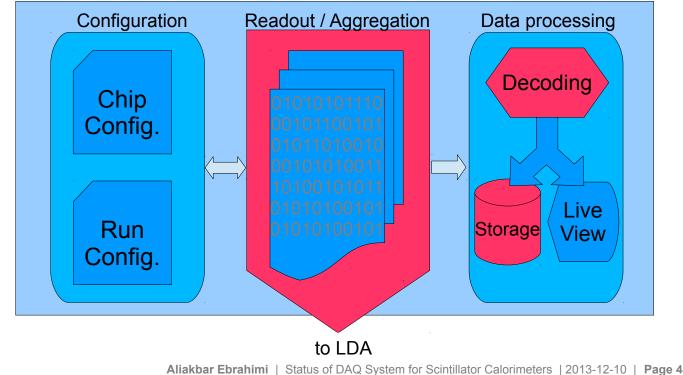

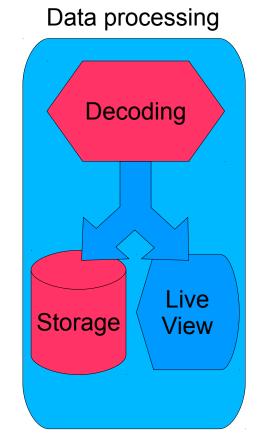

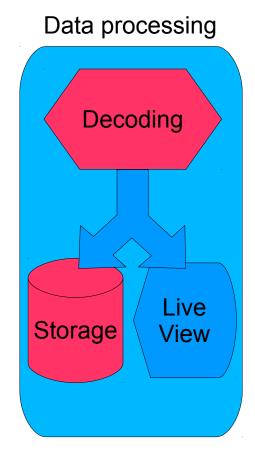

# **C++ Libraries for Decoding and Storage**

- > A C++ windows library (DLL) is developed to replace native LabVIEW decoding

- Faster by a factor of 5

- Calling the C++ DLL from LabVIEW is ~20% faster

- Decoding algorithm will be optimized to make it even faster

- > ASCII file output for storage

- In current version LabVIEW handles the storage

- > A LCIO converter function is developed and is tested in Linux environment

- Not implemented in DAQ software as of yet

- To be added to the LDA master software

#### **Main DAQ Components**

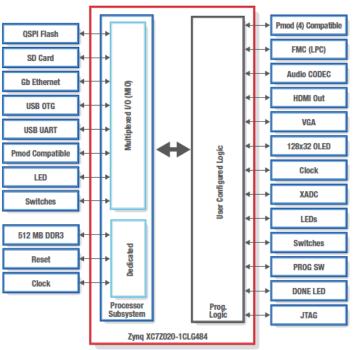

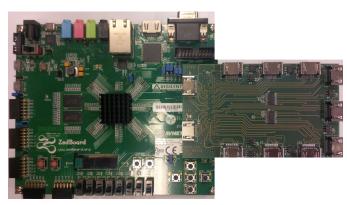

#### ZedBoard

- > Zynq Evaluation & Development Board

- > Xilinx Zynq-7000 SoC

- Processor Subsyst. (PS): Dual ARM Cortex-A9

- Programmable Logic (PL): Xilinx 7 series FPGA

- 100Gbps interconnect bandwidth

- ARM programmability+FPGA flexibility

- > On board memory

- 512 MB DDR3 + 256 MB QUAD-SPI

- > PS is able to run Linux

- > FPG Mezzanine Connector (FMC)

- Allows adding custom boards

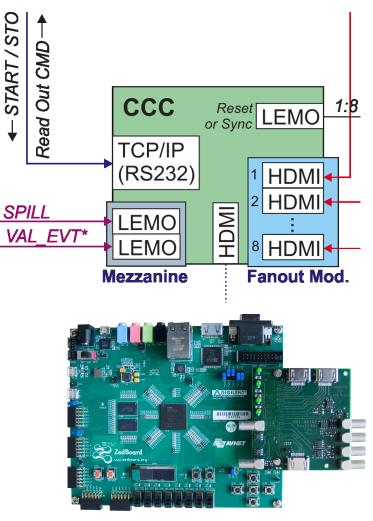

# **Clock and Control Card (CCC)**

- New CCC design by university of Mainz

- Compatible with CALICE DAQ

- Based on the ZedBoard

- Mezzanine board designed at Mainz uni.

- Ethernet connection to DAQ PC

- Start / Stop / Readout

- In temp. setup while LDA is being developed

- 8 layers are served using an 1:8 HDMI fanout

- LEMO connections for

- Validation signal

- Spill signal

- Reset / Sync signal

- > Tested successfully and is in operation

#### ZedBoard and Mezzanine

#### **Main DAQ Components**

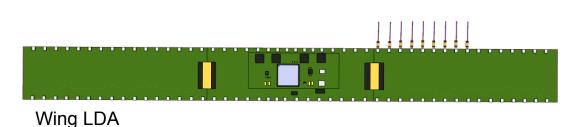

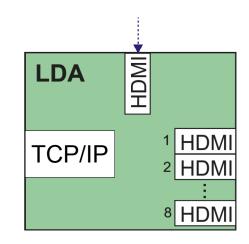

# Link and Data Aggregator (LDA)

- New LDA design by university of Mainz

- Compatible with CALICE DAQ

- Based on the ZedBoard

- Mezzanine board designed at Mainz uni.

- > There are two options

- Mini-LDA: ZedBoard + Mezzanine → Generic

- Wing LDA → AHCAL geometry specific

- Mini-LDA hardware is ready

- I HDMI connection to the CCC

- I0 HDMI connections to the the DIFs

Mini-LDA and Mezzanine

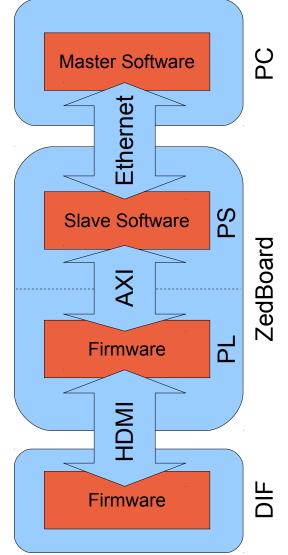

### LDA Development Roadmap

- > A fully functional LDA requires

- Programming the PL (Firmware)

- Programming the PS (Slave Software)

- Change in DAQ software (Master Software)

- 1<sup>st</sup> step: Mini-LDA as fanout

- Only firmware development is needed

- To be tested during December testbeam

- > 2<sup>nd</sup> step: HDMI and USB connection

- HDMI for fast signals and reading data

- Firmware and master/slave software development

- Firmware is being developed at DESY, software at the university of Mainz

- To be tested during January testbeam

### LDA Development Roadmap

- > By the end of the first two steps

- Control signals and data are transferred via HDMI

- Level/Edge sensitive single signals

- All twisted pairs of HDMI cable are already used

- Slow signals are still transferred via USB

- Therefore implementation of protocol for block-transfer and command packets is required

- > 3<sup>rd</sup> step: Only HDMI connection

- LDA Firmware

- LDA master/slave software

- DIF firmware modification

- Parallel development of the wing-LDA

- To allow for more than 10 layers

- Mini\_LDA firmware and software could be adopted with minimum effort

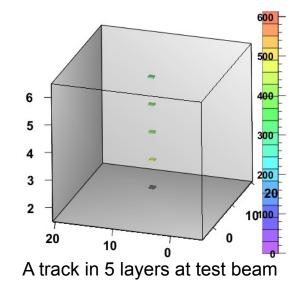

### Performance of the DAQ system

- Current version of the DAQ tested in different setups

- Lab Setup, Cosmic Muon run, Test beams

- Fully synchronous operation of 5 layers

- Very stable operation

- 72+ hours cosmic Muon run

- Faster than ever

- ~9Hz readout frequency

- ~150Hz sustained trigger rate

- Successfully tested in a two detector setup

- 2xHBU + 2xEBU

- It could be used for the other calorimeters

HCAL+ECAL

# **Scalability Considerations**

- Readout rate of ~9Hz (all memories full)

- Seems not to scale with number of layers up to now

- Different components need to be tested in larger setups with more layers/HBUs

- Decoding is the bottle-neck

- Depends on the computing power of the PC

- In previous tests each layer used one core

- Having more layers/HBUs will slow down the system

- Unless computing power is increased

- Decoding on one of the FPGAs could be a better solution

- DIF FPGA or LDA FPGA?

#### **Next Steps and Summary**

#### Next steps

- Full implementation of the Mini-LDA

- Finalizing the Wing-LDA

- > Testing an optimization of the full DAQ in different setups

- Scalability considerations

#### Summary

- > DAQ system for scintillator calorimeters is under development

- Main DAQ software is improved and tested

- > CCC is tested and in operation

- LDA is under development

- Current version of the DAQ was tested successfully in a multi calorimeter setup

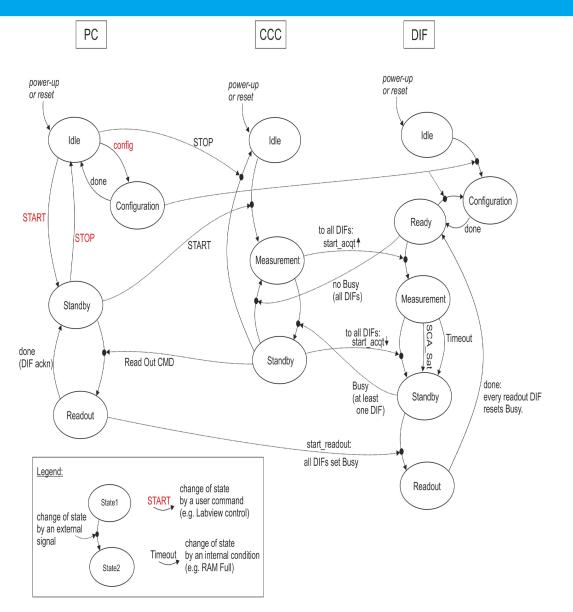

#### Backup

#### **State Diagram**

Aliakbar Ebrahimi | Status of DAQ System for Scintillator Calorimeters | 2013-12-10 | Page 17

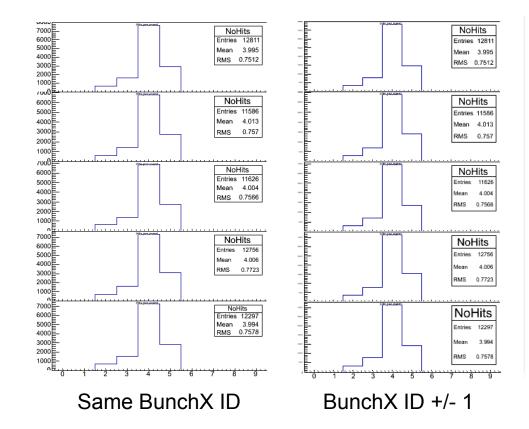

# **Multilayer Synchronicity**

- During July test beam synchronicity was tested

- For the same run, number of hits was checked in two different event builders

- Accepting only the same bunch crossing IDs

- Accepting bunch crossing IDs +/- 1

- > Absolutely no difference is observed

#### > We have a true synchronous detector