# - RF Signal Detection and Actuation

LLRF Lecture Part 3.4 S. Simrock, Z. Geng ITER / PSI

### ilr iit

- Requirements to RF field detector

- RF field detection methodology

- Reduce the noises and compensate the drifts in RF field detection

Outline

- RF actuation

- Appendix

- Typical hardware for RF field detection

- Mixer

- Analog to Digital Converter (ADC)

### **Requirements to RF Field Detector**

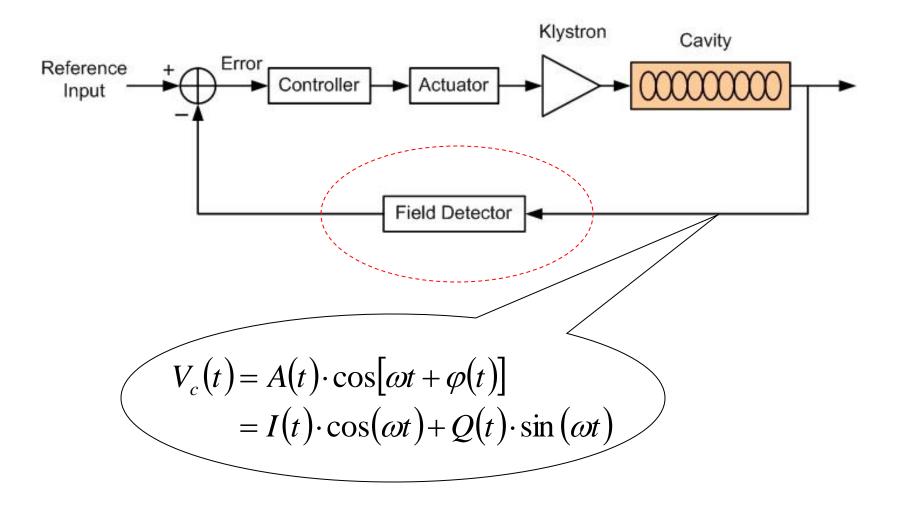

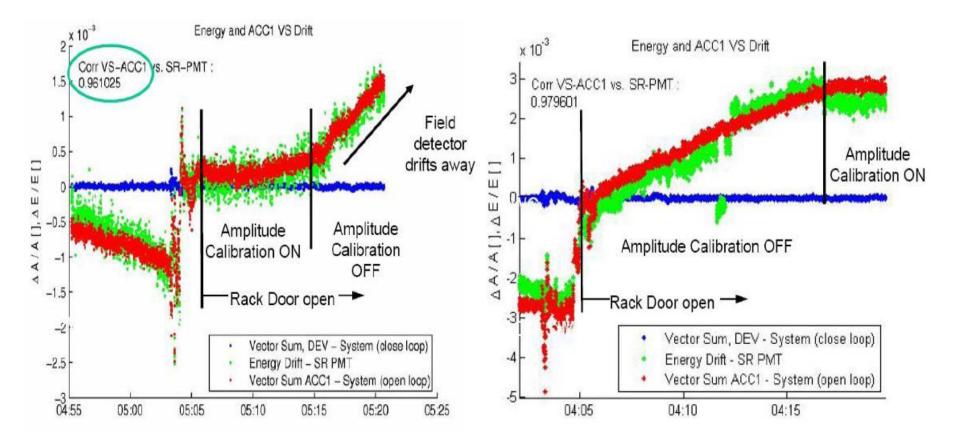

### Context of the RF Field Detector

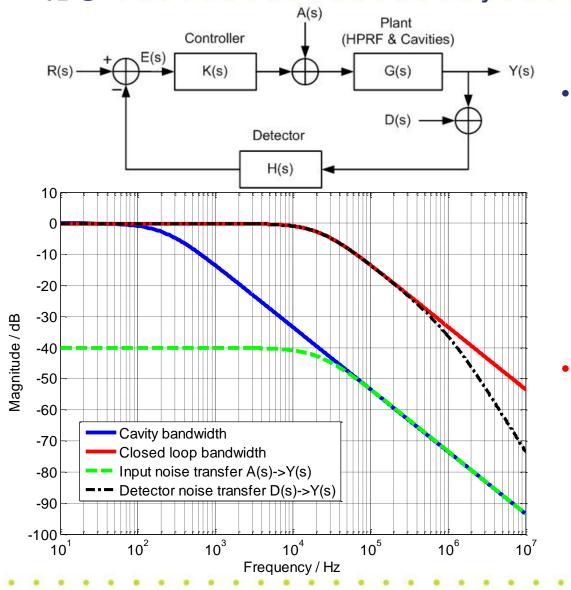

#### Recall: Transfer Function from Detector Noise to Cavity Field

IIL

- Low frequency noise of

detector is transferred

directly to the cavity

output; high frequency

noise is filtered by

closed loop bandwidth

and detector bandwidth

- Reducing the detector noise will be essential to get highly stable cavity field!

- The requirements of the RF field detector should be derived from the overall requirements to LLRF system

- Functional requirements: detect the amplitude and phase of RF field for each cavity in real time

- Quality requirements:

- Field detection bandwidth

- Amplitude and phase error

- Non-linearity

Example for FLASH:

- Field detection bandwidth: 10 MHz

- Amplitude and phase error: < 10^-4

- Non-linearity: at full scale of the measurement, the amplitude compression should be less than 1% and phase shift should be less than 0.5 degree

### **RF Field Detection Methodology**

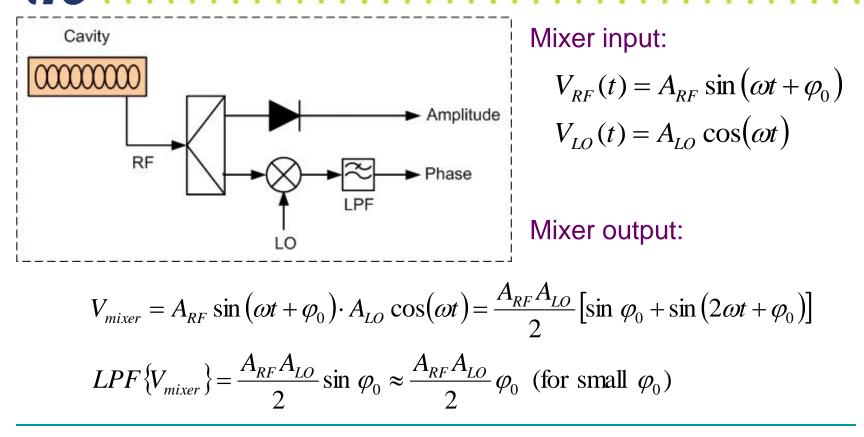

### Direct Amplitude and Phase Detection

- Simple system structure

- Linear for small phase errors

- Phase measurement is influenced by the amplitude error of the RF or LO signal

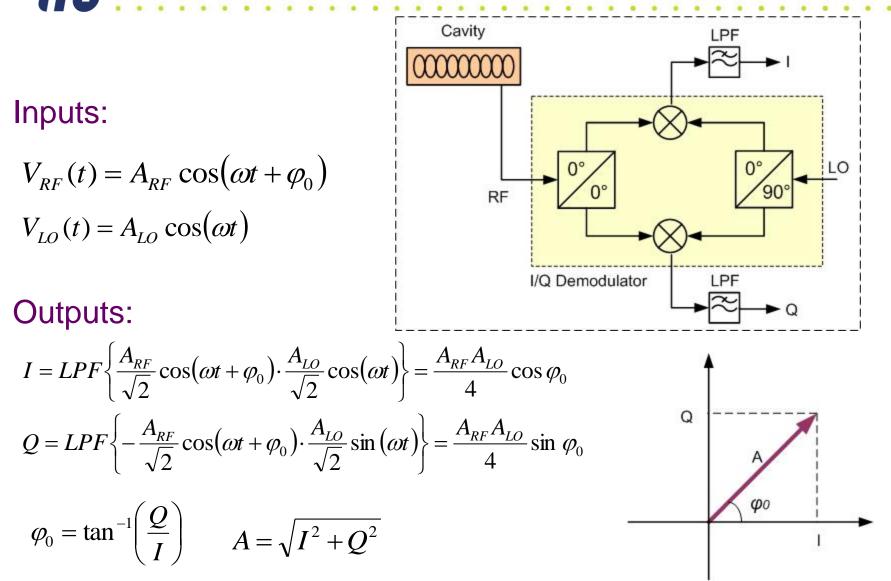

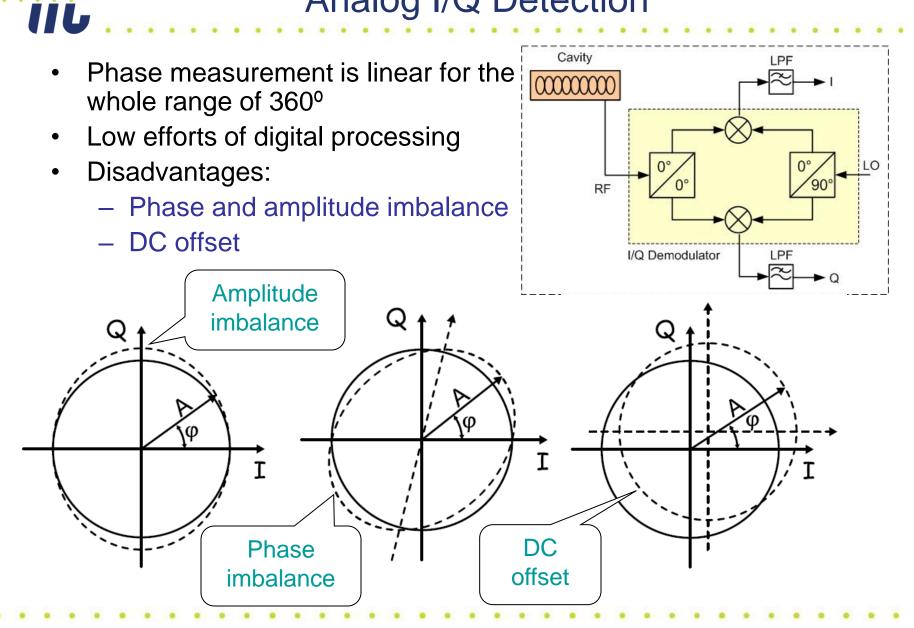

### Analog I/Q Detection

### Analog I/Q Detection

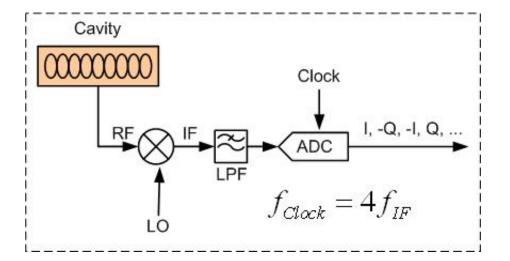

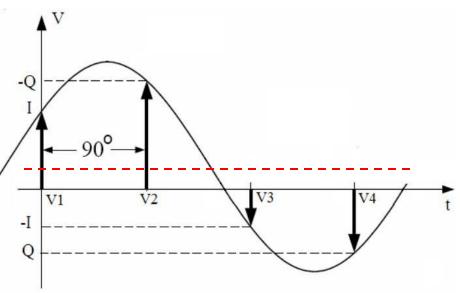

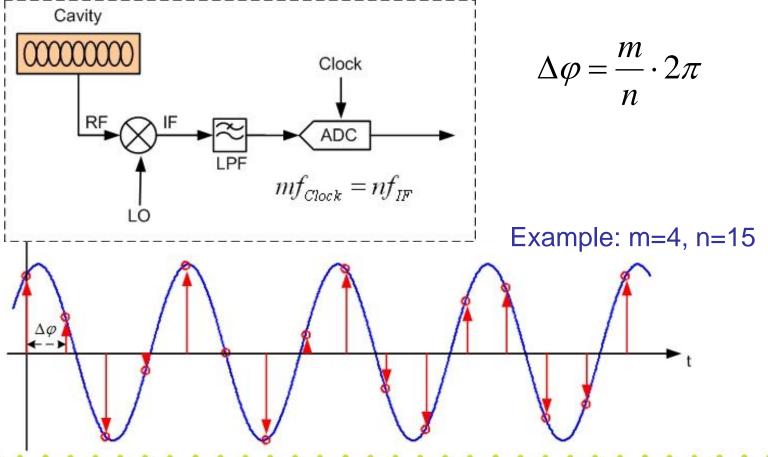

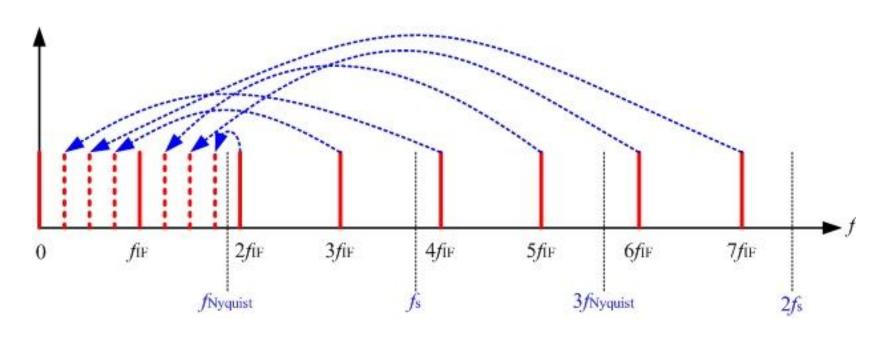

### **IQ** Sampling

IIL

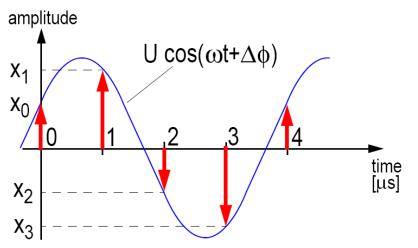

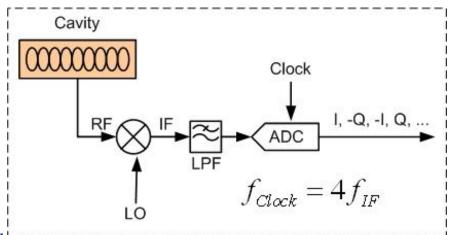

- Digital I/Q detection

- IF and clock signal should be synchronized

- Alternating sample give I and Q components of the cavity field

### IQ Sampling at FLASH

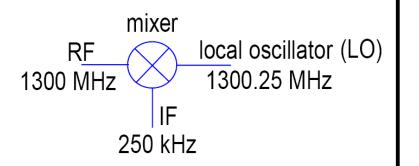

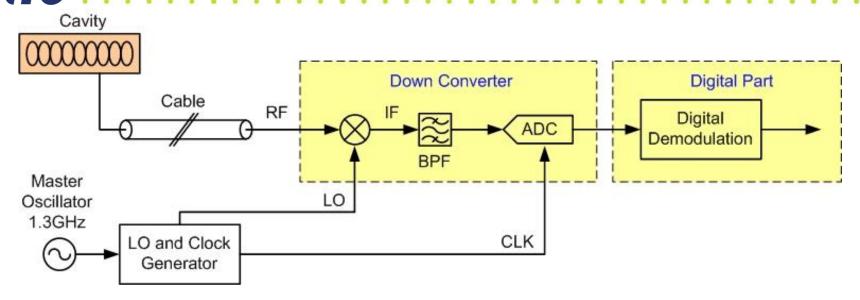

- downconversion of cavity field to IF frequency at 250 kHz

- complete phase and amplitude information of the accelerating field is preserved.

- sample IF signal at 1MHz rate

- subsequent samples describe real and imaginary component of the cavity field.

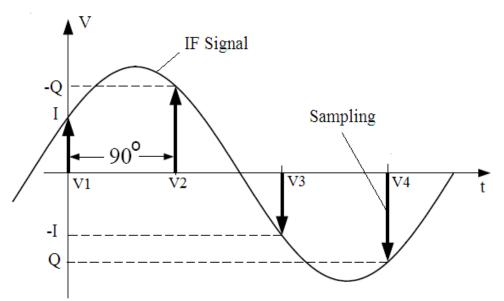

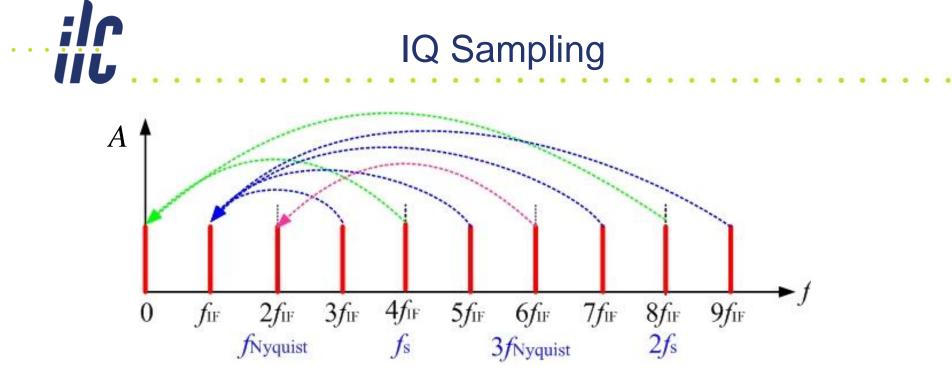

### **IQ** Sampling

Advantages

IIL

- Get rid of the imbalance effect compared with the analog I/Q demodulator

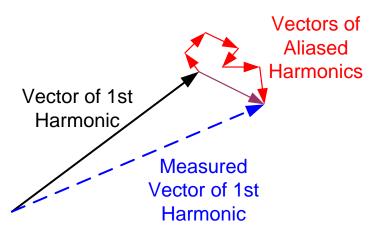

- Problems

- DC offset caused by the mixer

- Nonlinearities in the analog frontend or the ADC generate harmonics, which will be aliased to the IF frequency

- The phase of nth harmonic changes n times faster than the fundamental phase

- Phase shifts in the cavity due to microphonics and Lorenz force detuning will lead to a time dependent error

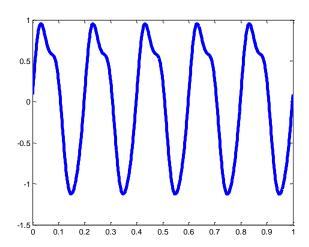

Compared with IQ sampling, non-IQ sampling is aimed to avoid the harmonics aliasing by shifting the sampling frequency slightly from 4 times of the IF frequency

• Fourier series decomposition of the RF signal

$$s(t) = A \sin \left( 2\pi f_{IF} t + \varphi \right) = I \cos \left( 2\pi f_{IF} t \right) + Q \sin \left( 2\pi f_{IF} t \right)$$

$$s(t) = \frac{a_0}{2} + \sum_{k=1}^{\infty} \left[ a_k \cos \left( k 2\pi f_{IF} t \right) + b_k \sin \left( k 2\pi f_{IF} t \right) \right]$$

$$\begin{cases} a_k = \frac{2}{T} \int_0^T s(t) \cos \left( k 2\pi f_{IF} t \right) dt \\ b_k = \frac{2}{T} \int_0^T s(t) \sin \left( k 2\pi f_{IF} t \right) dt \end{cases}$$

$$k = 1, 2, ...$$

• Demodulation algorithm:

IIL

$$I = \frac{2}{n} \sum_{i=0}^{n-1} x_i \cos(i\Delta\varphi), \quad Q = \frac{2}{n} \sum_{i=0}^{n-1} x_i \sin(i\Delta\varphi)$$

- Most harmonics no longer line up with IF frequency. Influence due to the higher order harmonics and DC offset can be reduced with band pass filter.

- The algorithm for demodulation need more computation power and will cause larger latency

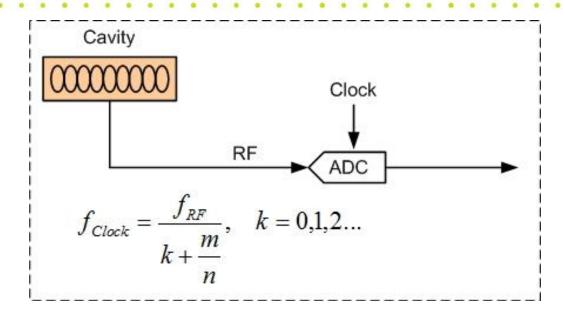

### **Direct Sampling**

- Example for available ADC: ADS5474, 14 bits, 400MSPS, 1.4GHz bandwidth

- Under-sampling

- Non-IQ sampling (m,n have the same meaning as the discussion of non-IQ sampling)

• Advantage: no down converter needed

ΪĹ

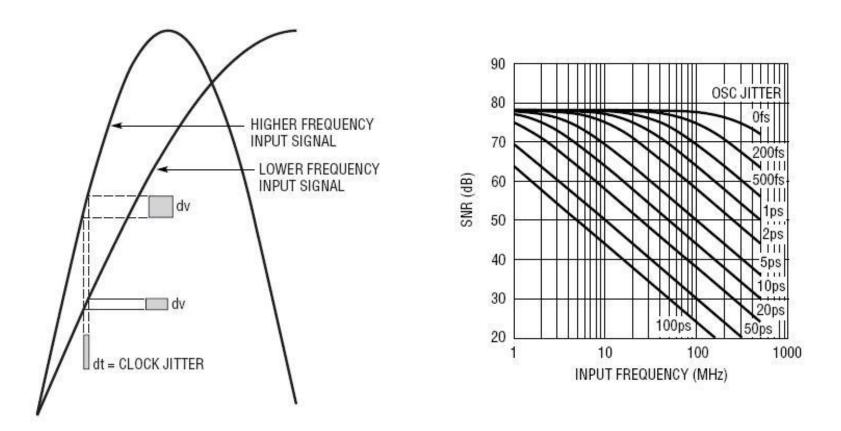

• Essential problems: ADC measurement noise is sensitive to the clock jitter due to the high input RF frequency

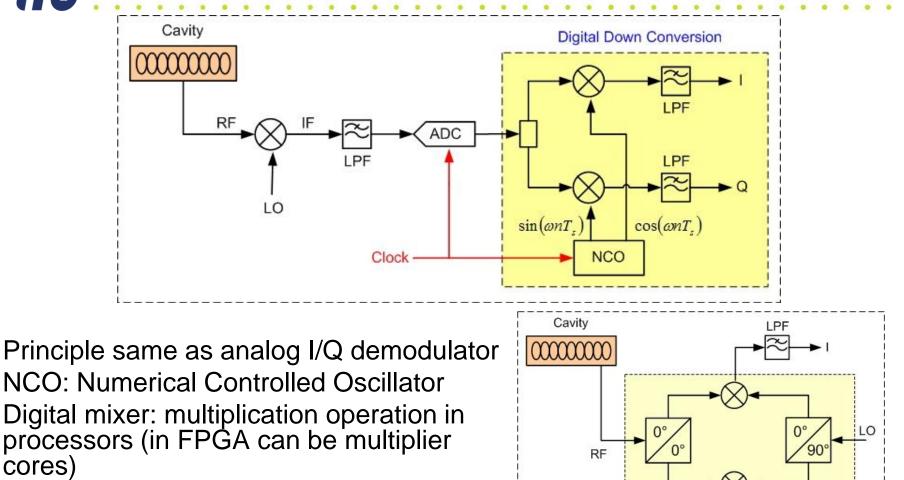

### **Digital Down Conversion**

I/Q Demodulator

LPF

Digital low pass filter, can be IIR, FIR or CIC filter

IIL

cores)

## Reduce the Noises and Compensate the Drifts in RF Field Detection

### Noise and Drift Sources for RF Detection

- Slow phase and amplitude drifts:

- Cavity pick up cables

- Down converter

- LO low frequency phase noise

- Fast phase and amplitude jitters:

- Thermal noise

- LO high frequency phase noise

- ADC noise

### Reduce the High Frequency Noise

- Select components of down converter with low noise level

- Filtering in RF side

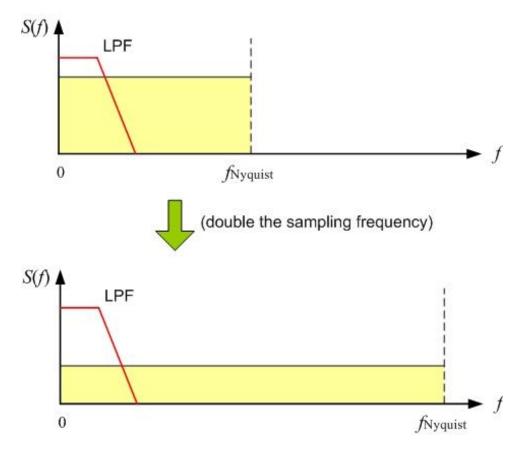

ΪĹ

ADC oversampling

### **Drift and Fluctuation Correction**

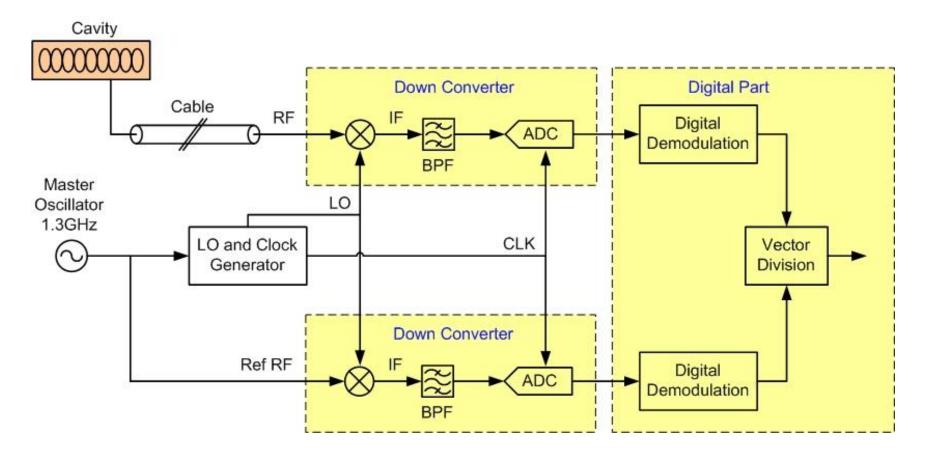

#### **Reference tracking**

ΪŪ

### Drift and Fluctuation Correction

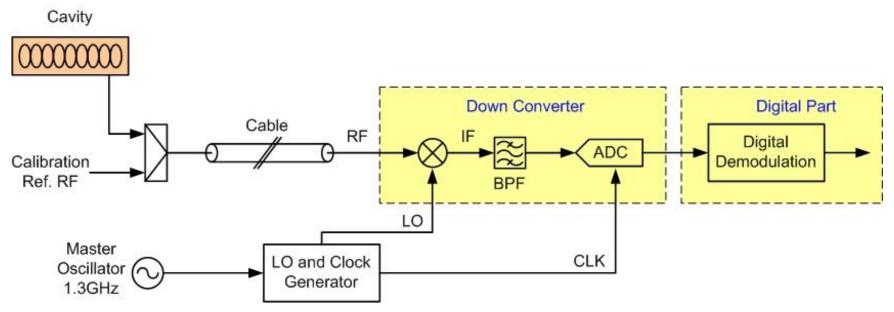

#### Measurement chain drift calibration

IIL

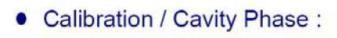

- Pulsed RF Station: Calibration Ref. RF can have the same frequency but be injected at different time slot compared to the RF pulse

- CW RF Station: Calibration Ref. RF should have different frequency to the cavity RF

### **Drift and Fluctuation Correction**

#### Measurement chain drift calibration: test setup

• Setup DEV System :

ΪĹ

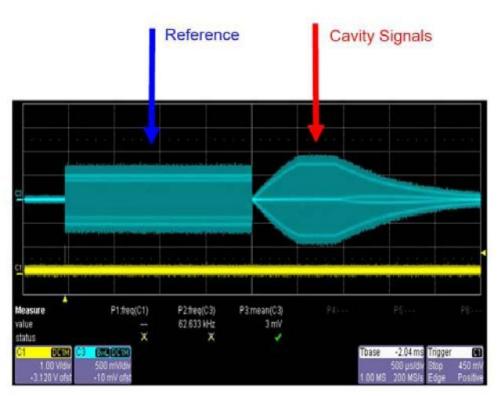

### Measurement chain drift calibration: test result at ACC1 of FLASH

İİĻ

### **RF** Actuation

## ir

- Change the amplitude and phase of RF driving signal and perform frequency up-conversion

- Widely used solutions:

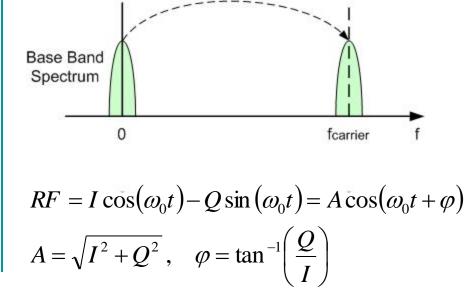

- Direct up-conversion

- IF up-conversion

- Single sideband up-conversion

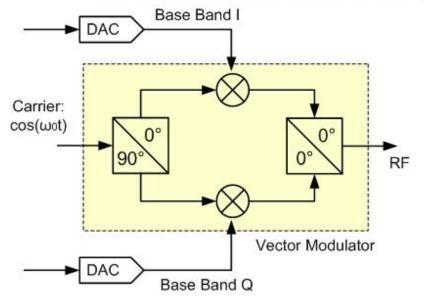

### **Direct Up-conversion**

- Easy to implement

- Requirements to DAC clock jitter is low

- Suffers from the DC offset in I/Q base band signals and the phase and amplitude imbalance of the vector modulator

- Band pass filter after the DAC can remove the DC offset

- Band pass filter after the mixer is necessary

- If IF is small, filter design will be critical

- Requires high quality DACs and low DAC clock jitter

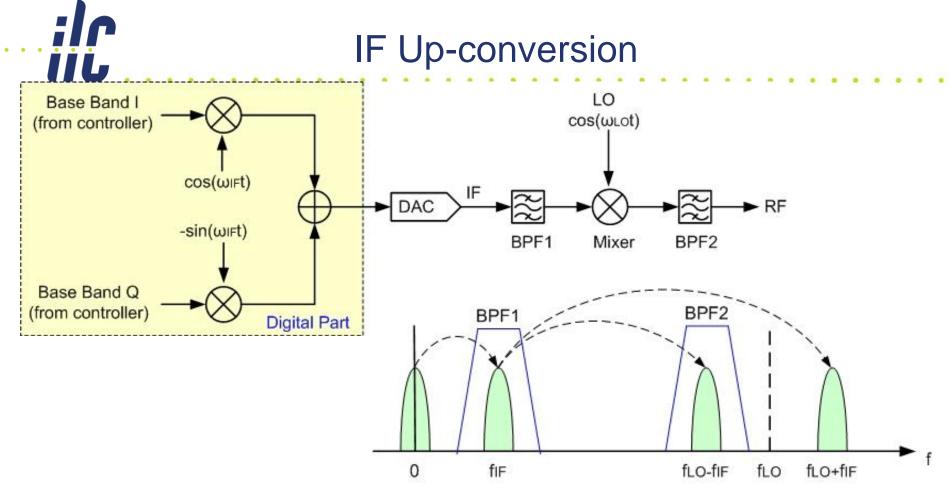

### Single Sideband Up-conversion

Summary

In this part, we have learnt:

- Principles and characteristics of several RF field detection methods

- Ideas to correct the noise and drift of the RF field detector

- Principles for several RF actuation (up-conversion) methods

[1] Z. Geng. Design and Construction of the Phasing System for BEPCII Linac. Ph.D. thesis of Chinese Academy of Sciences, 2007

[2] T. Schilcher. Vector Sum Control of Pulsed Accelerating Fields in Lorentz Force Detuned Superconducting Cavities. Ph. D. Thesis of DESY, 1998

[3] M. Hoffmann. Development of A Multichannel RF Field Detector for the Low-Level RF Control of the Free-Electron Laser at Hamburg. Ph.D. Thesis of DESY, 2008

[4] L. Doolittle. Digital Low-Level RF Control Using Non-IQ Sampling. LINAC2006, Knoxville, Tennessee USA

[5] Z. Geng, S. Simrock. Evaluation of Fast ADCs for Direct Sampling RF Field Detector for the European XFEL and ILC. LINAC2008, Victoria, BC, Canada

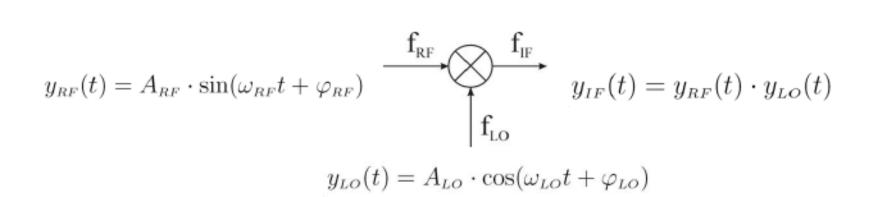

### Appendix: Typical Hardware for RF Field Detection

Mixer

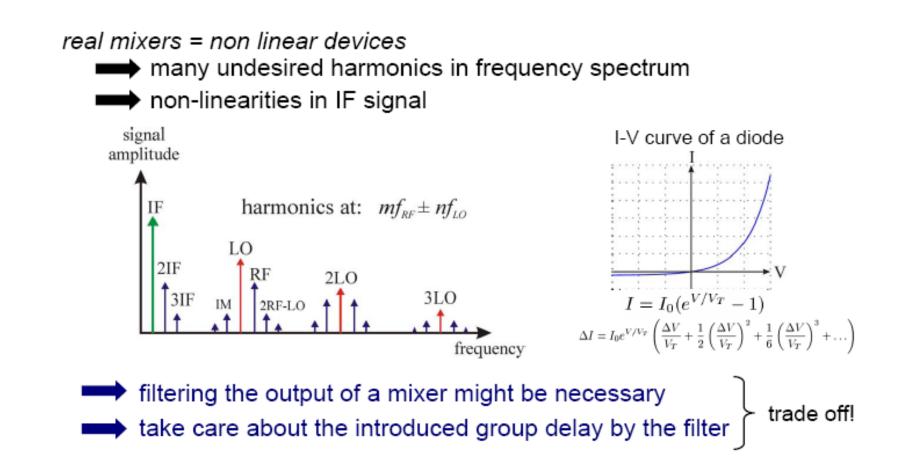

mixer: linear time varying circuit, non-linear circuit (diodes...)

$$\Rightarrow y_{IF}(t) = \frac{1}{2} A_{LO} A_{RF} \cdot \left( \frac{\sin[(\omega_{RF} - \omega_{LO})t + (\varphi_{RF} - \varphi_{LO})]}{+\sin[(\omega_{RF} + \omega_{LO})t + (\varphi_{RF} + \varphi_{LO})]} \right)$$

lower sideband upper sideband

even ideal mixers produce two sidebands

İİĻ

Mixer

down conversion:

IIL

RF, LO are high frequency inputs IF: lower intermediate frequency output

IF is input, RF is output

#### down conversion:

IL

$y_{IF}(t) = \frac{1}{2} A_{LO} A_{RF} \cdot \left( \sin \left[ (\omega_{RF} - \omega_{LO}) t + (\varphi_{RF} - \varphi_{LO}) \right] + \sin \left[ (\omega_{RF} + \omega_{LO}) t + (\varphi_{RF} + \varphi_{LO}) \right] \right)$ low pass filtering the upper sideband:  $\implies y_{IF}(t) = A_{IF} \cdot \sin \left( \omega_{IF} t + \varphi_{IF} \right)$  $\omega_{IF} = \omega_{RF} - \omega_{LO}$  $A_{IF} = \frac{1}{2} A_{LO} A_{RF} \sim A_{RF} \quad \text{with constant } A_{LO}$  $\varphi_{IF} = \varphi_{RF} - \varphi_{LO} \sim \varphi_{RF} \quad \text{with constant } \varphi_{LO}$ basic properties of RF signal are conserved (ampl./phase)

#### important properties:

- In phase changes/jitter are conserved during down conversion, e.g. 1° @ f<sub>RF</sub>=1.5 GHz ↔ 1° @ f<sub>IF</sub>=50 MHz

- comparison: sampling IF or RF (direct sampling)? timing jitter results in different phases! (e.g. 10 ps @ 500 MHz → 1.8°; 10 ps @ 50 MHz → 0.18°)

- tougher requirements for direct RF sampling !

Mixer

**||**L

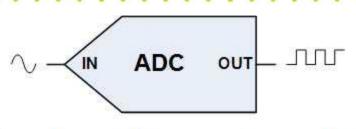

ELECTRICAL SYMBOL FOR ANALOG TO DIGITAL CONVERTER (ADC)

## What is an ADC?

### Mixed-Signal Device

- Analog Input

- Digital Output

- May be Considered to be a Divider

- Output says: Input is What Fraction of V<sub>REF</sub>?

- → Output = 2<sup>n</sup> x G x A<sub>IN</sub> / V<sub>REF</sub>

- n = # of Output Bits (Resolution)

- G = Gain Factor (usually "1")

- A<sub>IN</sub> = Analog Input Voltage (or Current)

- V<sub>REF</sub> (I<sub>REF</sub>) = Reference Voltage (or Current)

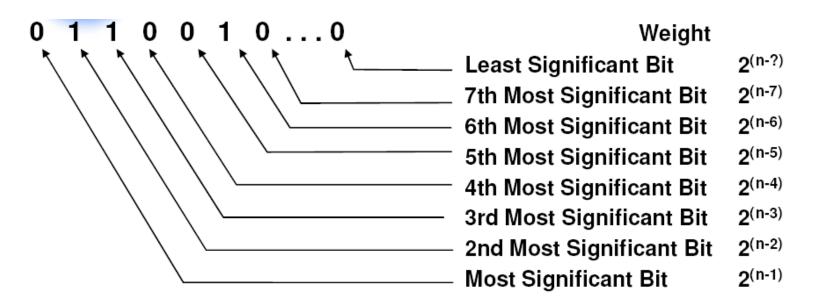

## Least Significant Bit (LSB) and Most Significant Bit (MSB)

#### Bit Weights of an 8-Bit Word

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| B7  | B6 | B5 | B4 | B3 | B2 | B1 | B0  |

| 128 | 64 | 32 | 16 | 8  | 4  | 2  | 1   |

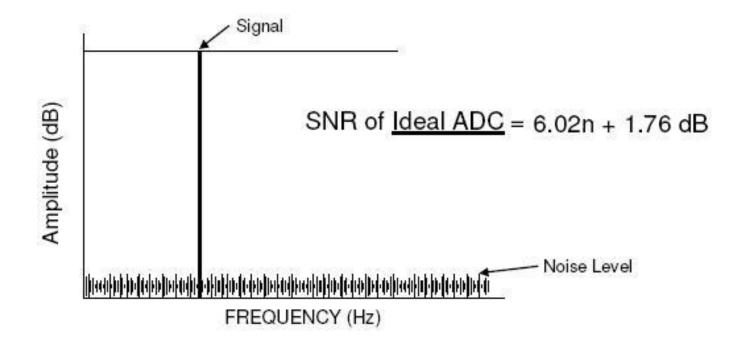

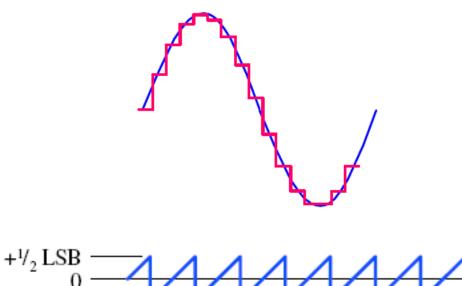

ADC noise source: Quantization noise

-1/2 LSB

- Quantization Produces Noise

- Quantization Noise Is Inversely

- Inversely Proportional to ADC Resolution

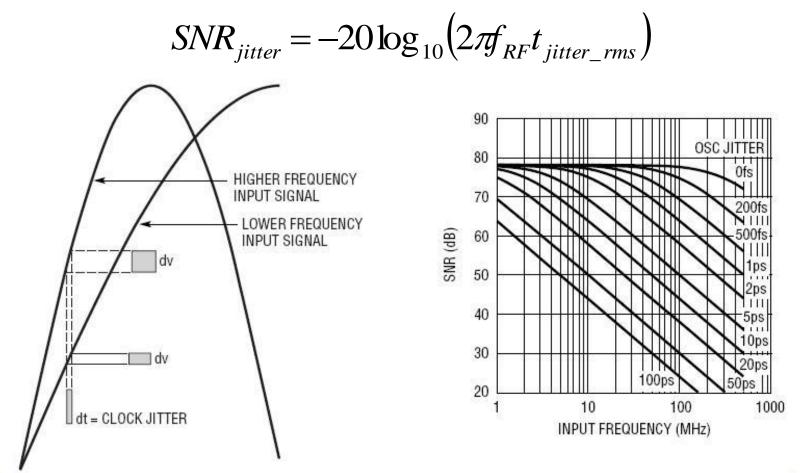

ADC noise source: Clock jitter

İİĻ

$$SNR_{jitter} = -20\log_{10}(2\pi f_{RF}t_{jitter\_rms})$$

ADC noise source: Noisy components or circuitry

- ADC Input Signal Conditioning is Common

- Noisy Amplifiers

- Resistors

IIL

- Noise

- Use Low Values

- High Frequency Coupling

- Resistor Packs

- Bandpass Characteristics

- Oscillation

- D.C. Offset

Signal to Noise Ratio (SNR) of ADC:

ΪĹ

$$SNR_{dB} = -20 \log_{10} \left[ (2\pi f_a t_j)^2 + \frac{2}{3} \left( \frac{1+\epsilon}{2^N} \right)^2 + \left( \frac{2\sqrt{2}V_n}{2^N} \right)^2 \right]^{\frac{1}{2}}$$

- $f_a$  : input frequency [Hz]

- $t_j$  : rms clock timing jitter [s]

- $\epsilon~:~{\rm differential~nonlinearity,~DNL~[LSB]}$

- N : number of bits

- $V_n$  : equivalent input noise [LSB].

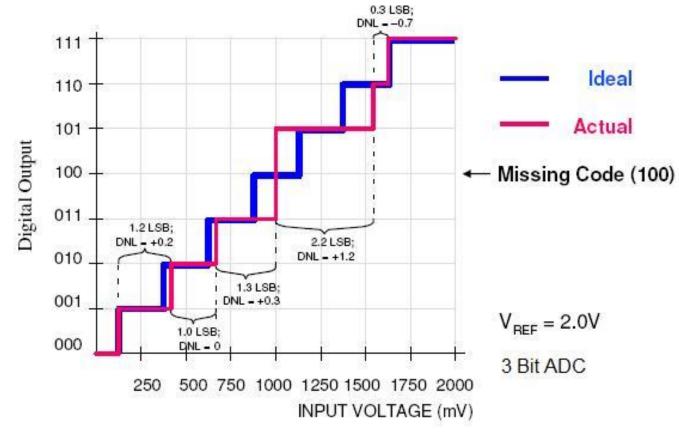

Differential Non-Linearity (DNL): "small scale" code to code errors

ΪĹ

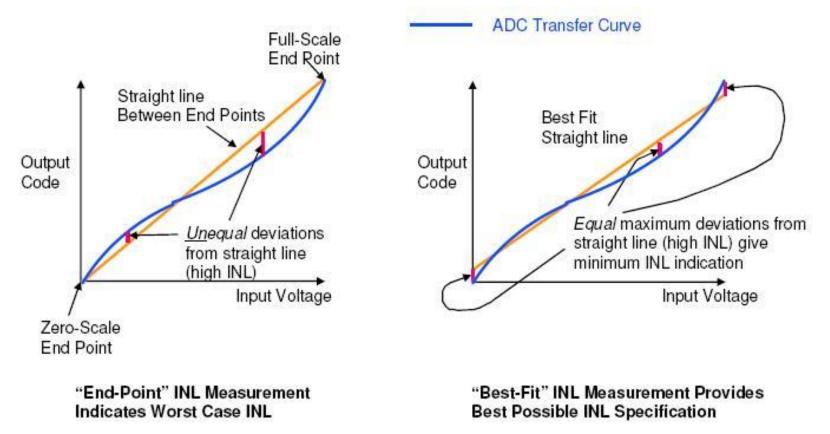

## Integral Non-Linearity (INL): "large scale" overall transfer function error

ΪĹ