# FPCCD VTX R&D Status and Prospects

#### Yasuhiro Sugimoto KEK 2014/9/8 @ILD meeting

# **R&D** issues

- FPCCD sensor

- Readout electronics

- Front-end ASIC

- Peripheral circuit

- Engineering R&D

- Support structure including ladders

- Cooling system

# **FPCCD** Sensor

| R&D Goal                                                   | Achievement                                            | Prospect                                    |

|------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|

| Pixel size; 6um $\rightarrow$ 5um                          | 6um fabricated, under evaluation                       | 5um after ILC approval                      |

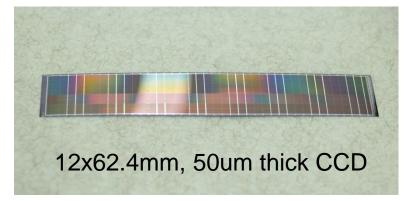

| Chip size; $1x6.25cm^2 \rightarrow 2x12.5cm^2$             | 1.2x6.24cm <sup>2</sup> achieved, to be evaluated      | 2x12.5cm <sup>2</sup> after ILC approval    |

| Chip thickness; 50um                                       | 50um achieved for 1.2x6.24cm <sup>2</sup> chip         |                                             |

| Speed; >10Mpix/s                                           | Under investigation → Improved<br>clock circuit needed | New clock circuit/cable in coming 2~3 years |

| Power; <10mW/ch                                            | Achieved in design                                     | To be verified soon                         |

| Radiation tolerance; >1x10 <sup>13</sup> e/cm <sup>2</sup> |                                                        | Neutron irradiation test soon (2014/Oct.)   |

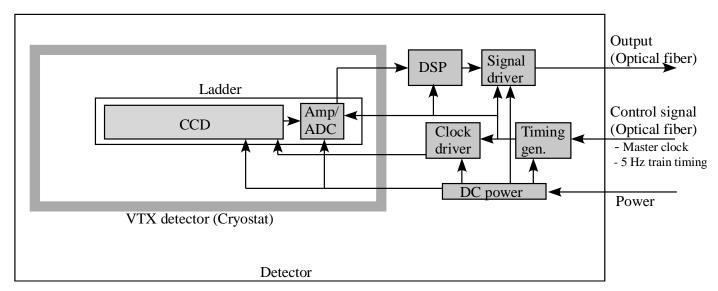

### **Readout electronics**

| R&D Goal                 | Achievement | Prospect                     |

|--------------------------|-------------|------------------------------|

| ASIC speed; >10Mpix/s    | ОК          |                              |

| ASIC power; <6mW/ch      | ОК          |                              |

| ASIC noise; <30electrons | ОК          |                              |

| 3-value clock driver     |             | To be developed in 2~3 years |

| Low mass FPC             |             | To be developed in 2~3 years |

| Data compression circuit |             | To be developed in 2~3 years |

# Engineering R&D

| R&D Goal                                                     | Achievement               | Prospect                                      |

|--------------------------------------------------------------|---------------------------|-----------------------------------------------|

| Low mass ladder                                              |                           | To be developed in 2~3 years                  |

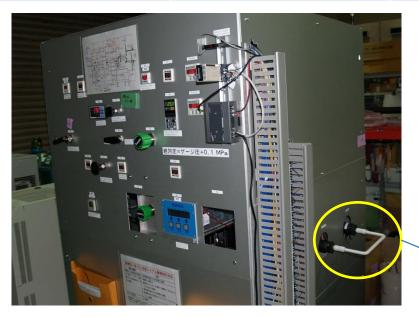

| 2-phase CO2 cooling<br>system; −40°C using gas<br>compressor | Principle<br>demonstrated | More stable and practical system in 2~3 years |

| Support structure                                            |                           | To be developed in 2~3 years                  |

| Engineering prototype                                        |                           | To be developed in 3 years                    |

2-phase CO2 cooling system for proof of principle

-40°C here

#### **BACKUP SLIDES**

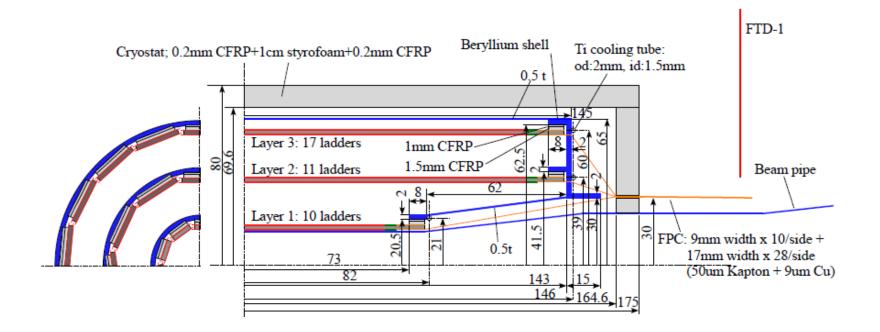

### FPCCD VTX